说明:在刷HDLBits题库中遇到一些值得自己注意的点,记录在下,希望分享给大家,也能时刻提醒自己偶尔过来复习。

- 基础

1.1 关于建模方式的理解

Verilog HDL描述语言可以被分为数据流建模、行为级建模以及结构化建模三类建模方式,其中结构型建模主要是通过对电路结构的描述,即是对电路进行连线,属于比较少用的一类;数据流建模在我理解下就是通过对信号的幅值所进行的,主要使用assign;而行为级建模主要则是在过程中进行对信号的变化,主要使用initial与always。

1.2 关于建模方式的理解

在Verilog HDL中有很多运算符在对信号进行处理时会需要,在此整理如下方便查询:

|与||:|按位或,||逻辑或,a[31:0] | b[31:0]会得到一个32位的数,a[31:0] || b[31:0]会得到一个1位的数.

^的执行逻辑是:a ^ b ^ c ^ d = ((a ^ b) ^ c) ^ d

1.3 四个很绕的问题

1.敏感信号的选取

在always语句块中存在敏感事件,其语法格式是:always@(<敏感事件列表>),每当敏感事件列表中的信号被满足,always语句就将被触发开始执行。在实际设计中,(1)采用过程语句块对组合电路进行描述时,全部输入信号都需列入敏感信号列表。(2)采用过程对时序电路进行描述时,需要把时间信号和部分输入信号列入敏感信号列表,同时,不同的敏感事件列表会产生不同的电路形式。

2.阻塞性和非阻塞性过程赋值语句的区别

阻塞赋值语句的操作符号为“=”,而非阻塞赋值语句则是“<=”。二者最大的区别则是在串行语句块中,阻塞赋值语句按照先后排列顺序依次执行,而非阻塞赋值语句则是并行执行。使用不同的赋值语句在实际综合时会产生不同的电路:

概括而来:只有行为级描述语言+串行语句+阻塞赋值语句才能是串行执行。

3.流水线设计

所有的数字逻辑电路都可以分为组合逻辑电路(门电路)和时序逻辑电路(寄存器),根据输入量、输出量以及状态量之间的关系,可以构建电路的输出方程,输入方程以及状态转移方程。如下图所示:

其中,组合逻辑电路实际上是带有容性的,并且组合逻辑元件越多,C越大,由于,即电路的延时越大,则会影响电路工作效率。如果我们能把一个“时序→组合→时序”改变成“时序→组合→时序→组合→时序”,这样的延时会大大降低,这样的设计方式即是流水线设计。如下图所示:

4.循环的可综合性

“for”循环实际上也是可综合的,在电路中用计数器去实现,但是一般来说,循环需要实现的功能,用移位器也可以实现。

1.4 模块的例化

在顶层模块中实例化(简称例化)下层模块时(在顶层模块中使用其它模块),只需关注下层模块的端口,而不必在乎它的内部代码。

模块的层次化结构通过在一个模块中例化另一个模块来实现,只要这些模块都处于一个project(项目)中,编译器就能找到相对应的模块。注意,在一个模块中可以例化,但不允许定义和编写其他模块。

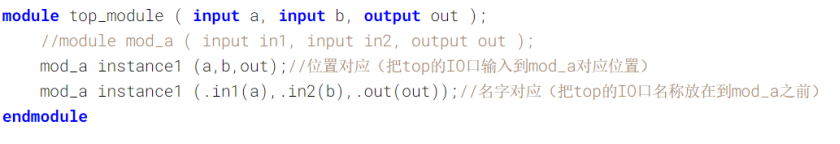

模块的连接有两种方法:1.位置对应;2.名字对应。例如:实例化一个下层模块mod_a,将其三个端口in1,in2,out按照图中的连接方式,分别连接到顶层模块的a,b,out端口上。

1.5 时序图中的信息

1.不定状态——在实际电路中不影响电路结果;

2.省略号——在电路中表示长时间电平状态不发生变化;

1181

1181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?