目录

写在前边

在验证的过程中,有时我们需要对协议的某些特殊场景进行验证,这就要求一些信号要被刻意的拉高放低。比如现在有一个场景,在验证低功耗Q_channel 协议时,device中的reset信号要在规定时间拉高,以验证reset在拉高是,qreq_n拉低的场景。这样的信号是不受系统reset控制的,可以通过force release进行控制,当然这只是举了一个小例子,针对force release的应用在验证过程中是会经常遇到的,所以特别有必要熟练掌握该语法。

1. 概念

force的作用相当于给模块的接口强制赋值了一个值;

release的作用相当于把force这个强制条件给解除了。

2.示例

module arb_port(output logic [1:0] grant,

output logic grant_valid,

input logic [1:0] request,

input logic rst,

input logic clk);

logic pri;

always_ff@(posedge clk or negedge rst)

begin

if(rst)

pri<=0;

else

pri<=~pri;

end

always_comb begin

grant_valid=|request;

if(request==2'b01||request==2'b10)

grant=request;

else if(request==2'b11)

unique case(pri)

1'b0: grant=2'b01;

1'b1: grant=2'b10;

endcase

else begin

grant_valid=0;

grant=0;

end

end

endmodule

module test(input logic [1:0] grant,

input logic grant_valid,

output logic [1:0] request,

input logic rst,

input logic clk);

initial begin

@(posedge clk)

request<=2'b01;

$display("@%0t: Drove req=01",$time);

repeat(2) @(posedge clk)

request<=2'b10;

$display("@%0t: Drove req=10",$time);

repeat(2) @(posedge clk)

request<=2'b11;

$display("@%0t: Drove req=11",$time);

end

endmodule

module top;

logic [1:0] grant;

logic grant_valid;

logic [1:0] request;

bit rst;

bit clk;

initial begin

rst=0;

clk=0;

forever

#5 clk=~clk;

end

initial begin

#25 rst=1;

#100 rst=0;

end

initial begin

#35 force port1.rst = 0;

#50 release port1.rst ;

end

initial begin

$fsdbDumpfile("top.fsdb")

$fsdbDumpvars()

end

initial begin

#200 $finish();

end

arb_port port1(grant,grant_valid,request,rst,clk);

test test1(grant,grant_valid,request,rst,clk);

endmodule波形展示:

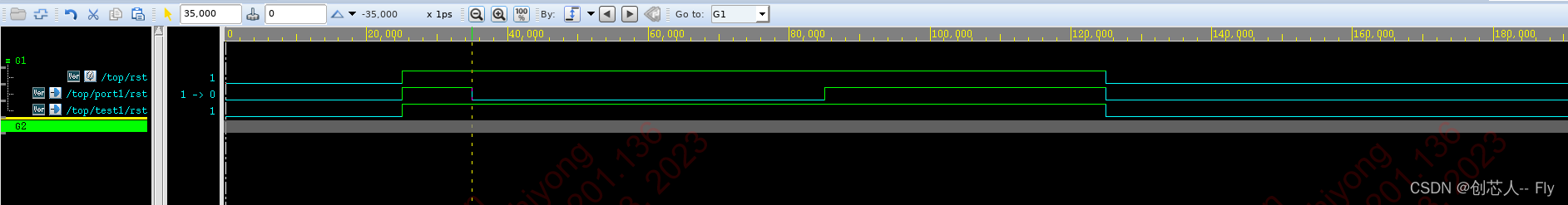

示例中,在35ns时使用force强制将port1中的rst拉低,再过50ns release,从波形可以发现,由于代码中只针对port1进行force,所以test中的rst与top中给定的一致。

3.小结

(1)在没有force下,即release环境下,模块的接口输入的就是其对应信号;

(2)在force下,相当于系统做了一个强制赋值,被force的信号要优先被执行,只有release之后才接入模块中的对应信号。

3806

3806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?