相关文章

Verilog基础专栏![]() https://blog.csdn.net/weixin_45791458/category_12263729.html

https://blog.csdn.net/weixin_45791458/category_12263729.html

1.disable语句

Verilog中的disable语句提供了终止并发活动过程的能力,同时保持了Verilog过程描述的结构化本质,它在处理意外情况时很有用,例如硬件中断或全局复位,但其可综合性无法保证,只应在仿真时使用。

disable语句可以有如下用途:

1、提前结束任务的执行。

2、提前结束命名块的执行。

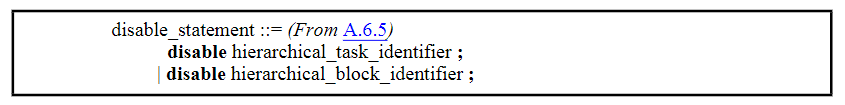

图1是disable语句的BNF范式语法(有关BNF范式,可以参考以往文章)。

图1 disable语句的语法

disable语句能够结束任务或命名块的执行,说明如下:

1、在disable语句执行后,受影响(直接或间接)任务或者命名块的执行将被停止,然后直接受影响的task使能语句和命名块之后的语句开始执行。

2、在disable语句执行后,受影响(直接或间接)的任务或命名块中已调度但还未执行的语句将不再执行。

3、如果一个任务被并发地使能多次,那么disable该任务将结束该任务的所有激活(无论其是否是自动任务)。

4、在disable语句执行后,受影响(直接或间接)的任务中从output和inout参数返回给实参的值(通常在任务返回时传递)是未定义的。

5、在disable语句执行后,受影响(直接或间接)的任务或命名块中的过程连续赋值(assign和force)的行为是未定义的。

6、如果一个函数中的disable语句结束了调用(直接或间接)该函数的任务或命名块,该行为是未定义的。

2.disable语句的例子

例1:disable语句结束命名块的执行,块后语句继续执行

// 一个命名块在块内终止了自己

initial begin

begin: block_name

rega = regb;

#1 disable block_name;

#2 regc = rega; // 不会执行

end

$display("hello world"); // 在1ns时执行

end例2:disable语句结束命名块的执行,间接结束命名块中正在执行的任务和任务中已调度的系统函数的执行

initial begin: test

task1(); // task使能

end

initial begin

#1 disable test; // 结束命名块的执行

end

task task1;

#5 $display("hello world"); // 不会在5ns时执行

endtask例3:disable语句结束多个task的激活

initial fork: test

task1(); // 多个task使能

task1(); // 多个task使能

task1(); // 多个task使能

task1(); // 多个task使能

join

initial begin

#1 disable task1; // 结束四个任务的执行

end

task task1;

#5 $display("hello world"); // 不会在5ns时执行

endtask例4:disable语句结束任务的返回值是未定义的

module example;

reg [3:0] a, b;

reg [3:0] result;

// 定义一个task

task add;

input [3:0] x, y;

output reg [3:0] z;

begin

z = x + y;

disable add; // 禁用task

end

endtask

initial begin

a = 4'b0011; // 3

b = 4'b0101; // 5

add(a, b, result); // 调用task执行加法

$display("Result: %b", result); // 输出结果是未定义的

endmodule

不同的仿真器给出的结果也不同

对于Mentor Modelsim SE,输出结果为

Result: 1000

对于Aldec Riviera Pro,输出结果为

Result: 1000

对于Cadence Xcelium,输出结果为

Result: 1000

对于Mentor Questa,输出结果为

Result: 1000

对于Synopsys VCS,输出结果为

Result: xxxx

对于Icarus Verilog,输出结果为

Result: 1000例5:一个可触发单稳态的行为描述

// 事件retrig的发生将重新启动单稳定时间段并给q赋值1,如果在250ns内retrig重复发生,那么q将保持为1,否则会变成0

always begin : monostable

#250 q = 0;

end

always @retrig begin

disable monostable;

q = 1;

end

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?