相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

本文是对Synopsys Design Compiler Topographical/Graphical Workshop Lab Guide中Lab1的翻译,Lab文件可以从以下链接获取。

实验一、检查DC-T物理元素(实验时长:30分钟)

学习目标

在本次实验中,你将检查Design Compiler Topographical(后面简称DC-T)环境。

完成本次实验后,你应能够:

- 启动DC-T

- 验证所需的物理元素是否已加载到DC-T中

- 在布局窗口中查看时序路径

- 在布局窗口中使用常用快捷键

- 描述用于设置DC-T环境的三个脚本

实验环境中已经使用DC-T为你编译生成了一个网表(.ddc格式),你将检查该最终结果。请快速完成任务1,因为从任务2开始才是你的重点(也是这个实验的重点)。

任务1、将已编译的网表读入DC-T

1、启动DC-T

cd lab1_elements

dc_shell -topo | tee -i mylog.log

# 下面的方式也是可选的

# dc_shell -topographical_mode | tee -i mylog.log2、使用source命令执行一些设置命令并导入包含布图规划(floorplan)的网表

source dc_setup.tcl

read_ddc ./results/ORCA_TOP.mapped_lab.ddc

link任务2、检查所需的物理元素

在本次实验中,使用了基于参考方法(Reference Methodology, RM)脚本,用户变量名使用大写的英文字母,下面将利用这种方法来检查该设计中定义的内容。

1、检查输入文件

printvar *FILE*问题 1:上述命令显示了代表各种文件类型的变量,其中哪三种文件类型是DC Topographical特有的?

答案 1:.tf后缀的工艺文件、.tluplus后缀的tluplus文件和.map后缀的映射文件(用于在工艺文件和 tluplus文件之间映射名称)。

2、检查库文件

printvar *LIB*问题 2:逻辑库(.db文件)和物理库(Milkyway 库)的主要区别是什么?

答案 2:逻辑库是文件而物理库是目录,逻辑库文件包含功能和时序信息,而物理库目录包含布局信息,例如单元和端口的位置、形状和大小。

3、检查Milkyway库

current_design

current_mw_lib

report_mw_lib -mw_reference_library问题 3:当前设计和当前Milkyway库的区别是什么?

答案 3:current_design命令报告在处理的当前设计;current_mw_lib报告存储与当前设计相关的所有数据(如tluplus信息)的Milkyway设计库目录。

问题 4:Milkyway设计库和Milkyway参考库之间的区别是什么?

答案4:Milkyway设计库是包含当前设计数据的目录,而Milkyway参考库是由半导体供应商提供的,包含当前设计中的基础物理单元。

4、检查tluplus文件、映射文件和工艺文件

report_tlu_plus_files

check_tlu_plus_files问题 5:是否已指定这三种类型的文件?

答案 5:是的,check_tlu_plus_files命令明确显示了tluplus文件和映射文件的文件名,并说明了映射文件与ITF(工艺文件)中使用的名称一致。

任务 3、检查DC-T中的可选元素

1、检查物理约束

report_physical_constraints问题 6:是否已定义物理约束?

答案 6:是的,可以看到布局区域,以及端口和宏单元的位置都已被报告。此外,还指定了一些禁布区域(keepouts)。

2、检查物理约束(布图规划)

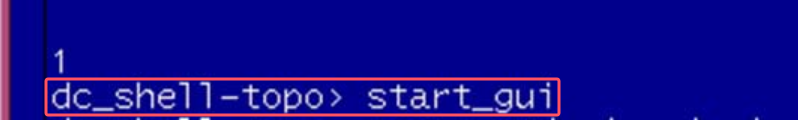

start_gui # 图1

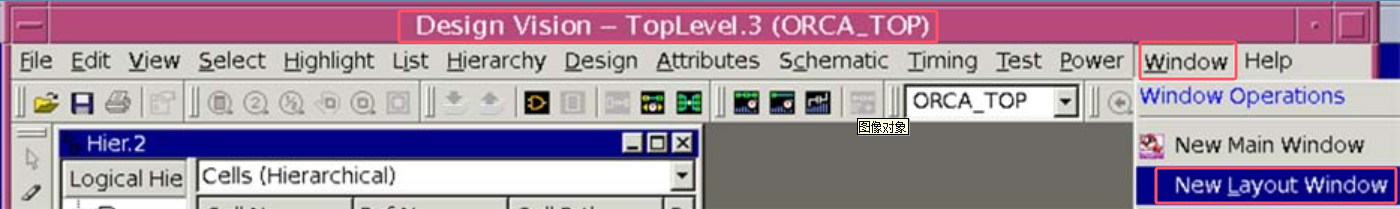

Window->New Layout Window # 图2

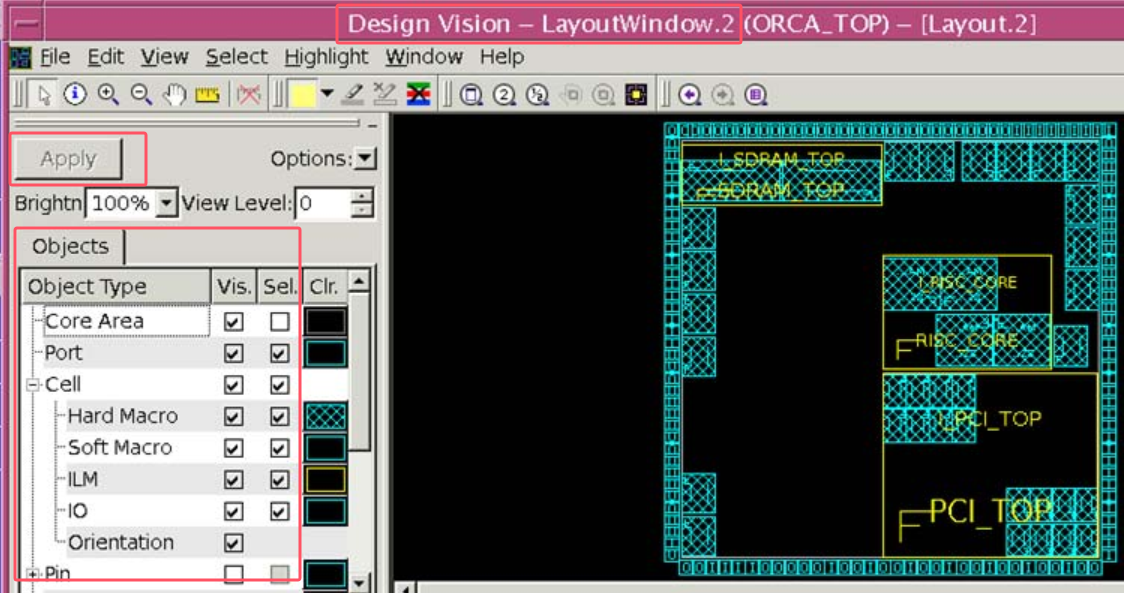

关闭除端口以外的所有对象的可见性 # 图3

关闭除单元以外的所有对象的可见性

打开单元、端口和标签的可见性

图1 开启GUI

图2 打开布局窗口

图3 改变可见性

问题 7:将鼠标悬停在端口或单元上时,会显示什么信息?信息显示在哪里?

答案 7:对象的名称、位置等信息会显示在GUI窗口的左下角(前提是该对象拥有可选择性)。

3、检查floorplan中的PCI_TOP单元

在floorplan的右下方选择PCI_TOP,右键单击->Properties,查看其cell_type

选择PCI_TOP,Select->Cells->Leaf Cells of Selected Cells,右键单击->Properties,查看PCI_TOP中某个单元的cell_type问题 8:该设计是分层的还是扁平的?

答案 8:这是一个分层设计,包含了三个子模块。

4、单击布局左侧对象(Objects)框中的Cell类型的加号(+),展开该对象

问题 9:如何查看不同类型的单元?

答案 9:通过使用可见性(Vis.)框并单击应用(Apply)。

任务 4、窗口快捷键和功能

以下是一些快捷键和功能,可以帮助更好地浏览所有实验的结果。

1、使用Ctrl+`(反引号)在窗口间切换

在TopLevel和LayoutWindow之间切换

调整窗口位置和大小,使得即使在TopLevel处于前景时,屏幕右下角仍然可以看到floorplan2、在LayoutWindow中检查时序路径

切换到TopLevel,依次选择Timing->Timing Analysis Driver,在对话框中点击OK

在Timing Analysis Driver中通过单击Slack标题按Slack排序

选择一个时序路径,使用向下箭头键在LayoutWindow中连续显示多个时序路径,使用Ctrl键并点击选择多个路径,使用Shift键并点击选择一系列路径3、在LayoutWindow中比较时序路径的布线

在Timing Analysis Driver中选择一个路径,TopLevel窗口->Highlight->Selected

在Timing Analysis Driver中选择其他路径,TopLevel窗口->Highlight->Selected

切换到LayoutWindow,查看突出显示的时序路径4、在LayoutWindow中检查单元

在TopLevel窗口->Logical Hierarchy中选择I_PCI_TOP

在Logical Hierarchy右侧,点击下拉箭头并选择Cells(All)

通过以下步骤突出显示一系列单元:

选择列表中的第一个单元

滚动到列表底部

按住Shift键选择列表中的最后一个单元

切换到LayoutWindow,查看这些单元在物理floorplan中的位置5、在LayoutWindow中放缩

放大PCI_TOP中的某个单元:

点击窗口左上角的加号(+)图标

点击并拖动选择该单元区域

使用键盘上的+和-键进行放大或缩小

按F键将视图适配到窗口大小

返回选择模式:

点击窗口左上角的箭头图标

注意:如果找不到加号、减号和箭头图标,请尝试启用鼠标工具:View->Toolbars->Mouse Tools问题 10:顶层设计中宏单元的参考名称是什么?

答案 10:参考名称是ram8x64,可以通过放大查看floorplan或选择该单元并显示其属性来找到该信息。

任务 5、检查元素是如何定义的

DC-T环境是由三个文件设置的,任务是确定这些文件的名称、如何在它们之间划分设置,以及哪个文件调用哪个文件。

首先,打开一个Linux终端。

1、找到这三个脚本

在lab1_elements目录中:

ls *setup.tcl

ls ./dc_scripts/*.tcl

问题 11:这三个脚本的名字是什么?

答案 11:common_setup.tcl、dc_setup.tcl和dc.tcl(fm.tcl是用于Synopsys的形式验证工具Formality,通常在设计转换后运行)。

2、确定三个脚本的调用顺序

grep source *setup.tcl

grep source ./dc_scripts/dc.tcl问题 12:这三个脚本的调用顺序是什么?

答案 12:dc.tcl调用dc_setup.tcl,而dc_setup.tcl调用common_setup.tcl。

3、确定这三个文件的基本功能。请查看一个常用变量(DESIGN_NAME),以及这三个文件如何处理该变量

grep DESIGN_NAME *setup.tcl

grep DESIGN_NAME ./dc_scripts/dc.tcl问题 13:简单来说,这三个文件的作用是什么?

答案 13:common_setup.tcl定义设计元素和许多工具通用的工作环境,dc_setup.tcl引用 common_setup.tcl中的信息,进行工具特定的设置,dc.tcl对common_setup.tcl和dc_setup.tcl中定义的设计元素执行多种操作。

问题 14:使用common_setup文件的好处是什么?

答案 14:它有助于确保一系列工具的环境一致,从而在整个工具套件中获得更高的关联性和更可预测的结果。当您开始一个新设计时,脚本的更改将限于一个小文件;也就是说,主要更改会在common_setup.tcl中,而dc_setup.tcl中只有少量修改。

实验二

原文链接

Design Compiler Topographical/Graphical Workshop Lab Guide![]() https://download.csdn.net/download/weixin_45791458/89988989 感谢EETOP坛友的分享。

https://download.csdn.net/download/weixin_45791458/89988989 感谢EETOP坛友的分享。

2079

2079

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?