项目场景:

阅读了一下system generator生成的源代码,一开始对testbench中的调用模块的方式不是很理解,后来发现其实这就是Verilog中的参数传递,特此记录。

Verilog代码截图:

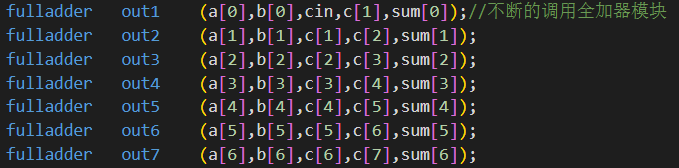

Verilog调用函数的代码如下图所示:

Tips:可以直接把vivado的编辑界面转到vscode里面,具体位置在Tools—setting–text editor中进行修改,具体方法请参考如下博客:

VScode快捷键小技巧:

ctrl + f : 搜索、替换

ctrl + r : 搜索过去曾经使用code打开的文件

Verilog代码分析:

在分析代码之前,先回顾一下Verilog的调用方式。

第一种,也是最简单明了的一种调用方式。假设其子模块如下,其名字为full adder,即我们熟悉的全加器,有三个输入端口,其名字分别为a,b,cin;有两个输出端口,其名字分别为cout和sum:

接下来,为了方便展示调用的写法,在一个8位加法器中调用8次全加器(full adder),调用关系如下图所示:

则第一种调用方法的写法如下,最前面的是被调用的子模块的名字,再是用户自定义的例化名字,再由子模块中定义的端口对应输入变量和输出变量:

这种写法的优势就是简单快捷,但是也有缺点,当我们阅读这几行代码的时候,我们无法很清楚的看到子模块中端口定义的名称是什么,因此就引出了第二种调用方法。

第二种写法如下,也可以达到同样的效果,同时可以根据

⋅

\cdot

⋅后面的名称很清楚的看出在(此处名为fulladder)子模块中,对端口的定义名称是什么:

OK,现在回到之前的那段system generator自动生成的代码,为了方便阅读我再贴一遍:

我们发现,这段代码和之前第二种调用方法非常类似,但是多了一个#号,这个就是Verilog的参数传递的写法,即可以通过参数传递改变在被引用模块中已经定义的参数。其具体的格式如下:

module_name # ( parameter1, parameter2) inst_name ( port_map)

即最先是被引用模块的名字,#后面跟着的是原来模块中定义的parameter的名称以及需要被改变的值,再后面则是和第二种调用方法一样了,说白了就是多加入了参数的传递。因此,以上的代码变得很容易读懂。

我们先找到被调用的子模块xltbsource的位置,可以使用vscode的Ctrl+f查找快捷键,如下图所示:

我们可以看出,它里面定义了7个parameter,一个input和一个output,而调用它时对其中的五个parameter通过参数传递的方法进行了修改:

对参数修改完之后,就是常规的调用方法,确保端口顺序对应即可。以下图的例子为例,xltbsource为子模块,而gateway_in_driver为用户自己定义的例化的名字:

解决了第一部分之后,后面的这段代码完全同理,不作过多说明。

7239

7239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?