文章目录

第 1 节 开发环境

对于初学者而言,首先需要了解的是 FPGA 的开发需要有对应的开发环境。目前两大 FPGA 制造厂商分别是 Xilinx 和 Altera(目前已被 Intel 收购),而每个厂商生产的 FPGA 芯片都需要在对应的开发工具上才能够进行设计。Xilinx 芯片的开发工具包括 Vivado 和 ISE(推出 Vivado 平台后,Xilinx 已经不考虑升级 ISE 版本),Altera 芯片的开发工具是 Quartus。本书以 Quartus prime 开发工具为例来详细介绍 FPGA 的开发设计流程。

Quartus prime 是 Altera 公司为其生产的 FPGA 芯片所设计的一款开发软件,其软件内嵌自有的综合器以及仿真器,可以支持原理图、VHDL、Verilog HDL 以及 AHDL(Altera Hardware 支持 Description Language)等多种设计输入形式,可以完成从设计输入到硬件配置的完整 PLD 设计流程。Altera Quartus prime 是 Altera 被 Intel 收购后在已完成开发的 quartus II 软件基础上开发的新软件。作为一种可编程逻辑的设计环境,该软件强大的设计能力和直观易用的接口使其越来越受到数字系统设计者的欢迎。Altera 的 Quartus prime 可编程逻辑软件属于第四代 PLD 开发平台,该平台支持一个工作组环境下的设计要求,其中包括支持基于 Internet 的协作设计。Quartus 平台与 Cadence、ExemplarLogic、MentorGraphics、Synopsys 和 Synplicity 等 EDA 供应商的开发工具相兼容,其改进了软件的 LogicLock模块设计功能,增添了 FastFit 编译选项,推进了网络编辑性能,而且提升了调试能力。该设计软件是业界唯一提供 FPGA 和固定功能 HardCopy 器件统一设计流程的设计工具(15.1 以及更高版本)。工程师可以使用同样的低价位工具对 Stratix FPGA 进行功能验证和原

型设计,同时可以设计 HardCopy Stratix 器件用于批量成品。系统设计者现在能够用 Quartus prime 软件评估 HardCopy Stratix 器件的性能和功耗,相应地进行最大吞吐量设计。

第2节 软件界面

在 Quartus prime 软件中进行开发工作的顶级组织单元叫做工程(Project),一个工程可以代表一个完整的软件解决方案。工程师设计的每一个工程文件都应该保存在单一的一个文件夹中。因此,开始一个新的逻辑电路设计的第一步就是新建一个文件夹来保存文件。接下来将详细介绍如何新建一个工程。为了保存此次的设计文件,在 D 盘新建一个 introtutorial 文件夹。本次运行的范例为一个简单的双路灯控电路。打开 Quartus prime 软件后将看到类似于图 1.4- 1 的画面。此主界面中包括若干窗口,用户可使用鼠标选择以访问 Quartus prime 软件的相关功能。Quartus prime 提供的大多数命令都可用菜单形式来访问。

例如,在图 1.4- 1 所示的主界面中,左键点击 File 标签,可打开如图 1. 4- 2 所示的菜单。用左键单击 Exit 可退出 Quartus prime 软件.

对于有些命令,需要连续访问两个或以上的菜单才可以使用。

第 3 节 第一个上板例程

本教材中涉及的所有案例,均是在 Quartus prime18.1 精简版开发软件上进行。其他版本的软件在界面上会略有不同,为了避免未知的错误,建议统一使用此版本。

本章将介绍 Quartusprime 软件的基本特征,并展示如何使用 Verilog 硬件描述语言来设计和实现电路功能。通过本章节的学习将掌握以下几方面的内容:

1、新建工程;

2、使用 Verilog 代码录入设计;

3、将综合的电路布局到 Altera FPGA ;

4、分配电路的输入输出到 FPGA 上的指定引脚;

5、编程配置教学板上的 FPGA 芯片。

3.1新建工程

按如下步骤新建工程:

-

选择 File>New Project Wizard,以打开图 1.4-3 所示窗口,可通过勾选 Don’t show me this introduction again 跳过此窗口步骤。随后单击 Next,此时会会出现图 1.4-4 所示窗口。

-

工程保存在新建的工作文件夹 introtutorial 下(也可以使用自己设定的文件夹),工程必须有一个名字,通常情况下工程名与顶层设计实体的名字相同。如图 1.4-4 所示,选择 light 作为工程名和顶层实体名。单击 Next。因为还未创建 introtutorial 文件夹,Quartus prime 会弹出一个对话框,询问是否新建所需文件夹,如图 1.4-5 所示。单击 Yes 后将会出现图 1.4-6 所示的窗口。

-

如果没有已存在的设计文件,单击 Next,将会打开如图 1.4-8 所示的界面。

4. 教学板采用的器件为 Cyclone ⅣE EP4CE15F23C8。此处选择 Cyclone ⅣE 器件家族。单击 Next 后出现图 1.4-9 所示界面,在此界面下选定第三方 EDA 仿真工具,并选择硬件描述语言为 Verilog HDL。

4. 教学板采用的器件为 Cyclone ⅣE EP4CE15F23C8。此处选择 Cyclone ⅣE 器件家族。单击 Next 后出现图 1.4-9 所示界面,在此界面下选定第三方 EDA 仿真工具,并选择硬件描述语言为 Verilog HDL。

5. 用户可指定一些第三方 EDA 工具。不改变默认,随后单击 Next,出现图 1.4-10 所示窗口。

5. 用户可指定一些第三方 EDA 工具。不改变默认,随后单击 Next,出现图 1.4-10 所示窗口。

6. 设置总览如图 1.4-10 所示。单击 Finish,返回 Quartus prime 主体窗口。标题栏将显示 light 工程,如图 1.4-11 所示。

至此,一个工程新建完毕,接下来将进入逻辑代码的设计。

3.2 代码设计

以双路的灯控电路作为一个设计范例,其数字逻辑如错误!未找到引用源。所示。此灯可由 x1和 x2 两个按键共同控制,当按键按下表示为逻辑 0,其真值表也同时在图中给出。注意输入 x1 和 x2 是异或的关系,但是在设计中仍然用最简单的与或非门来显示。

将上面的数字逻辑用硬件描述语言 Verilog 代码来描述。注意,此模块的名称仍为 light,其与图1.4-4 所示的名称一致。可以使用任何可存储 ASCprime 码的文本编辑器或者使用 Quartus prime 自带的编辑器进行该代码的编辑。当然,理论上模块的名称可以任意设定,此处设计的名称与顶层 Verilog 模块的名称一致是设计的惯例。文件名称必须带.v 扩展名用以指示此文件为 Verilog 文件。综上所述,本模块使用 light.v 这一名称。

将上面的数字逻辑用硬件描述语言 Verilog 代码来描述。注意,此模块的名称仍为 light,其与图1.4-4 所示的名称一致。可以使用任何可存储 ASCprime 码的文本编辑器或者使用 Quartus prime 自带的编辑器进行该代码的编辑。当然,理论上模块的名称可以任意设定,此处设计的名称与顶层 Verilog 模块的名称一致是设计的惯例。文件名称必须带.v 扩展名用以指示此文件为 Verilog 文件。综上所述,本模块使用 light.v 这一名称。

3.2.1 使用官方编辑器

本节将展示如何使用 Quartus prime 软件中的文本编辑器。喜欢使用其他文本编辑器来创建 Verilog 源文件也可以跳过此节。

首先选择 File>New 打开图 1.4-14 所示窗口,选择 Verilog HDL File 后单击 OK,打开文本编辑器窗口。第一步是指定所创建的文件的名称。选择 File>Save As,打开图 1.4-15 所示的对话框来命名并保存文件。选择存储类型为 Verilog HDL File,填写文件名称为 light.v。单击 Save,打开图 1. 4-16 所示窗口,在文本编辑界面中输入上图中的代码,输入完毕后使用快捷键 Ctrl+S 保存该文件。

3.2.2 使用GVIM编辑器

上一节为大家详细介绍了使用官方文本编辑器来编写 Verilog 代码的方法。事实上,也可以选择使用其他文本编辑工具来提高编写、修改代码的效率。在此推荐一款文本编辑器 GVIM,并展示如何使用该软件来设计 Verilog 代码。

首先,打开 GVIM 软件,打开文件>另存为。在弹出的图 1.4-17 界面中将文件名写为.v 格式,表示创建一个 Verilog 语言设计文本。这样在创建的文本编辑界面中,会高亮显示 Verilog 语法中的一些关键字。在此文本编辑界面中对案例中的代码进行编写,如图 1.4-18 所示。

3.2.3 添加文件

一个工程中可以包含许多个模块,每个模块又可以保存为一个独立的文件。正如图 1.4-7 所讨论的那样,设计师可以告诉 Quartus prime 软件哪些文件是当前工程的一部分。在前面的案例中如果要查看当前 light 工程中已包含的文件列表,可以选Assignment>Setting>File,随后可以打开图 1.4- 17 所示界面。另外一个操作方法是选择 Project>Add/Remove Files in Project。使用 Quartus prime 文本编辑器创建文件时勾选 Add file to current project 选项,所创建文件即可自动加入到工程文件列表。如果使用的不是 Quartus prime 自带的文本编辑器,那么在打开图 1. 4-19 所示的界面查看列表中的文件时,列表中没有所创建的文件,此时必须手动添加文件到工程文件列表中。具体操作方法为:单击图 1.4-19 中 File Name 方框后的按钮,弹出图 1.4-20 所示对话框,选择 light.v 后单击 Open 即可将该文件添加到工程文件列表中。此时再次查看图 1.4-19 界面,可以看到所添加的文件已经进入文件列表。需要注意的是,在大多数案例中 Quartus prime 软件可根据各个实体自动找到正确的文件,即使没有将文件添加到工程中也没有问题。然而,对于包含许多文件的复杂工程,将所需文件按照上述方法一个个添加到工程中去是一个很好的设计惯例。

3.3 编辑设计电路

设计完整个工程之后,要经过 Quartus prime 软件中几个工具的处理,分别是分析代码、综合电路以及生成目标芯片的实现内容。这些应用工具被聚集在一起,统称为编译器。选择 Processing>Start Compilation 运行编译器,或者单击如下:

按钮运行。在编译过程中,Quartus prime 的左边会显示编译的进度过程。当进度到达 100%即表示编译成功.

当编译成功后,可以通过如下:

按钮手动打开编译报告。

在此窗口的左面列出了许多信息的列表,其中比较有价值的信息是此工程使用的芯片资源情况。如图 1.4-21 所示,本工程使用到了 1 个逻辑单元(LE)和 3 个引脚资源。

在此窗口的左面列出了许多信息的列表,其中比较有价值的信息是此工程使用的芯片资源情况。如图 1.4-21 所示,本工程使用到了 1 个逻辑单元(LE)和 3 个引脚资源。

在编译期间,Quartus prime 在消息窗口会显示生成的消息。如果此工程编译通过,其中一条消息会显示编译成功,没有产生错误。

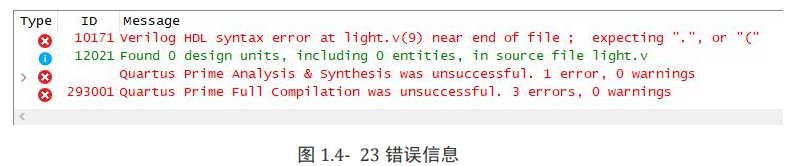

如果工程编译不通过,那么就代表设计的 Verilog 代码中至少有一个或以上错误。在这种情况下与代码中错误对应的消息就会在消息窗口显示。双击某条错误信息,该信息将会滚动显示完整并且打开 Quartus prime 自带文本编译器,将 Verilog 代码中处出现错误的地方高亮显示。类似的,编译器也会显示许多警告消息,同样的方法也适用于查看完整的警告消息。如果想获取针对于某条错误或警告消息的更多报告信息,可选住此报告后按 F1 功能键即可进行查看。

为了演示上述的现象,将模块 light.v 的最后一行改成 endmodules 后重新进行编译。Quartus prime 弹出对话框,显示编译不通过,编译报告如图 1.4-22 所示,单击 OK 以确认。在消息窗口单击Error 标签,显示图 1.4-23 所示消息。双击第一条错误信息后 Quartus prime 文本编辑器打开 light.v模块,可以看出最后一行被高亮显示,如图 1.4-24 所示。修正代码后重新进行编译,此时工程编译可以通过。

3.4 引脚分配

使用开发板上的 LED6(连接的信号线为 LED1_NET)代表 f,sw0 和 sw1 分别代表 x1 和 x2,所需引脚如图 1.4-25 所示。选择 Assignments>Pin Planner(或单击如下按钮),

打开图 1.4-26 所示窗口,在下方 Location 下面输入要配置的引脚信息。

3.5 编程及配置FPGA器件

引脚分配完毕之后,需要重新进行一次全编译。当全编译通过后 Quartus prime 软件即可生成可以烧录到 FPGA 中的配置文件。将下载器 USB-Blaster 与 FPGA 开发板进行连接,打开 FPGA 开发板电源后回到 Quartus prime 主界面,选择 Tools>Progrmmer 或单击如下按钮,打开图 1.4-27 所示窗口,

选择配置模式 Mode 为 JTAG。在缺省情况下,USB-Blaster 没有被选中,单击 HardwareSetup 按钮,在弹出的窗口选择 USB-Blaster 即可选定下载器,如图 1.4-28 所示,单击 Close 完成配置并退出。

如图 1.4-29 所示,待烧录进 FPGA 的配置文件 light.sof 已被列入窗口。如果该文件没有列入窗口,则单击 Add File 手动选择烧录文件 light.sof 加入。该文件是一个由编译器的汇编模块生成的二进制文件,其包含配置 FPGA 器件的数据。其中,.sof 文件后缀表示 SRAM 目标文件(SRAM Object File)。选中的器件为 EP4CE15F23,勾选 Program/Configure 选项,单击 Start。

注意,在使用前需要安装下载器的驱动程序。

USB-Blaster 用户,请参考 http://www.altera.com.cn/literature/ug/ug_usb_blstr.pdf

Byte-Blaste-rprime 用户,请参考 http://www.altera.com.cn/literature/ug/ug_bbprime.pdf

Ethernet-Blaster 用户,请参考 http://www.altera.com.cn/literature/ug/ug_ebcc.pdf

3.6 在线调试

下载完毕后即可进行电路的测试,利用 sw0 和 sw1 输入所有可能值,观察 LED 亮灭是否和预期保持一致。如果与预期不致,那么就需要去定位问题,此时将使用到 SINGNALTAP 工具,具体使用方法请参照下一章内容。

3.7 固化程序

将.sof 格式的配置文件烧录到 FPGA 中后,FPGA 无法完成配置文件的保存,在下一次上电的时候,FPGA 内部仍为空白。如果不希望每次上电后再次手动的将配置文件烧录到 FPGA 芯片内部,可以通过程序固化的方式,将配置文件烧录到 FPGA 芯片外部掉电不丢失数据的 Flash 存储器中。这样在每次上电的时候便可以自动的完成配置,外部存储器就会自动的将配置文件下载到 FPGA 中。

下面来介绍一下程序固化的具体步骤。

首先,打开 File>Convert Programming File,在 Programming file type 选项中选择.jic 文件格式。

如图 1.4-30 所示,将待烧录文件类型更改为.jic 格式后,在 Configuration Device 选项中选择设备配置为 EPCS64,在 Input files to convert 栏中,选择 Flash Loader 后点击 Add Device 按钮。随后选择 FPGA 器件型号,选择芯片型号为 EP4CE15,弹出如图 1.4-31 所示窗口后点击 OK。

如图 1.4-30 所示,将待烧录文件类型更改为.jic 格式后,在 Configuration Device 选项中选择设备配置为 EPCS64,在 Input files to convert 栏中,选择 Flash Loader 后点击 Add Device 按钮。随后选择 FPGA 器件型号,选择芯片型号为 EP4CE15,弹出如图 1.4-31 所示窗口后点击 OK。

接下来需要将.sof 配置文件转为.jic 格式,点击 SOF Data,如图 1.4-32 所示,选择相应的.sof配置文件。点击 Generate 按钮,生成.jic 文。

回到 Programmer 界面,点击 Add File 按钮,在文件夹下选择相应的.jic 文件。如图 1.4-32 所,将该文件加入之后在界面上将.sof 格式文件(通常情况下在第一行)取消勾选,在名称含有.jic 的文件选项中,勾选以下几个选项:Program/configure,Verify,Blank-Check。勾选 Program/configure 时其他文件的该选项也会自动勾选。

回到 Programmer 界面,点击 Add File 按钮,在文件夹下选择相应的.jic 文件。如图 1.4-32 所,将该文件加入之后在界面上将.sof 格式文件(通常情况下在第一行)取消勾选,在名称含有.jic 的文件选项中,勾选以下几个选项:Program/configure,Verify,Blank-Check。勾选 Program/configure 时其他文件的该选项也会自动勾选。

随后点击 Start 按钮,进行程序固化。

496

496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?