前言: 现代fpga的结构越来越复杂,经常会涉及到多时钟域的设计。其中对于功能电路来说,复位结构都必不可少。在同步逻辑设计中如何很好地处理异步复位,甚至在多时钟域之间传递(异步)复位信号也是逻辑工程师经常面临的问题与挑战。

接下来将从fpga逻辑设计的基本指导原则和代码优化方法进行学习;比如时钟域处理、如何进行速度和面积的互换和优化等等;实际应用中需要从FPGA硬件电路设计开始。fpga工程师在对设计进行系统联调时,如果对电路设计不了解,很可能会妨碍逻辑设计中故障的排出;所以掌握一些通用电路的设计方法和技巧就显得极为重要;

逻辑设计是FPGA设计的核心,时钟及多时钟域处理在现在的FPGA设计中极为常见,接下来将重点介绍跨越时钟域的数据处理。所以,我们需要根据一些特有的逻辑设计原则将电路设计得更简单、更直接、更易优化以及可重用。

今天将从基于FPGA的PCB设计开始介绍FPGA的设计开发,其中专门介绍了有关FPGA的高速电路设计。

目录

1.1基于fpga的高速电路板设计

-----名词解释:ocb(printed circuit board,印刷电路板);fpga(field-programmable gate array,现场可编程门阵列)

-----器件引脚密度和系统频率的增大,使得pcb布板越来越复杂;其中altera器件具有高速I/O引脚,支持多种高速特性,边沿速率不到100bps,因此实现成功的设计需要满足:对所有器件进行电源滤波(均匀分配电源,降低系统噪声)、匹配信号线(减少信号反射)、降低并行走线之间的串扰、减少地反弹效应、进行阻抗匹配。

1.1.1PCB材料选择和PCB上的传输线走线

pcb材料一般指pcb介质的构成材料;其中相对介电常数是相对于真空的介电常数,是两块金属板之间以绝缘材料为介质时的电容量与同样两块板之间以真空为介质时的电容量的比值,其影响传输线的阻抗;

当高频信号在pcb上从驱动器沿较长的传输线传输到接收器时,介电常数的损耗因数对信号的影响非常大。较大的损耗因数意味着较高的介质吸收,从而影响了传输线上的高频信号,并增大了高频衰减。通常,pcb的常用的介质材料为FR-4和GETEK;在制作pcb时,可以向厂商了解产品的介质材料相关信息,后期会进行阻抗匹配。

pcb上的传输线是一种具有分布式电阻(R)、电感(L)和电容(C)的走线。有微带线(只有一个电压参考平面,并且走线在pcb顶层或者底层)和带状线(走线在pcb内层,有两个电压参考平面eg:双带线布局:两个参考平面之间有两个靠近的信号层,如下图所示)两类传输线布局(W:走线宽度;T:走线厚度;H:两个参考平面之间介质层的厚度)。

1.1.2阻抗计算及降低串扰和维持信号完整性的布线方法

电路设计要在PCB走线的时候尽量做到阻抗匹配,这样子将设计文件交给生产厂家时,才能有裕量以便从容的进行阻抗控制。其中,基本阻抗控制的原则是:单端走线控制阻抗为50Ω;差分走线控制阻抗为100Ω,生产厂家阻抗控制的偏差范围一般在正负5%左右。阻抗计算需参考1.1.1中的介绍的介电常数以及传输线形式等参数。

串扰:并行走线之间耦合进了不必要的信号;其中1.1.1中的微带传输线和带状传输线的正确布线和叠层布线能够降低串扰。eg:为降低双带线的串扰,所有走线垂直布设,并增大两个信号层之间的距离(保持在介质高度的3倍以上),减少信号层和邻近参考平面的距离;两条邻近走线中心之间的距离应至少是走线宽度的4倍。分离走线,降低串扰。

对于高速电路板设计来说,fpga的高速数据传输均采用差分走线。为减少串扰及阻抗控制,还应该注意两个原则:1)不要将发送端线靠近接收端线;2)相邻信号层不要布平行差分走线,而应该使用正交走线。

1.2FPGA的电源供应

如果fpga周围缺乏足够退耦,将会显著降低FPGA设计的可靠性。

1.2.1供电要求

现代fpga的封装都非常小,而且通常都需要多种供电电压和复杂的供电要求;不同器件之间,fpga对于供电的整体要求会有差异,还体现在以下方面,分别是单调性(线性)要求(电源必须始终具有正斜率(或零斜率))、软启动要求、电压爬升控制(fpga上电过程中供电电压的上升速率)、用于时钟管理的干净电源(敏感的模拟电路要求干净的供电,通常需要使用线性电源,尤其是那些在电源轨上滤除了主要高频分量的电源器件(整个带宽内只剩线性电压自身)eg:fpga中的pll、transceiver等模块中模拟器件都要求单独使用线性电源供电)等等。

1.2.2PCB设计的电源和地叠层分布

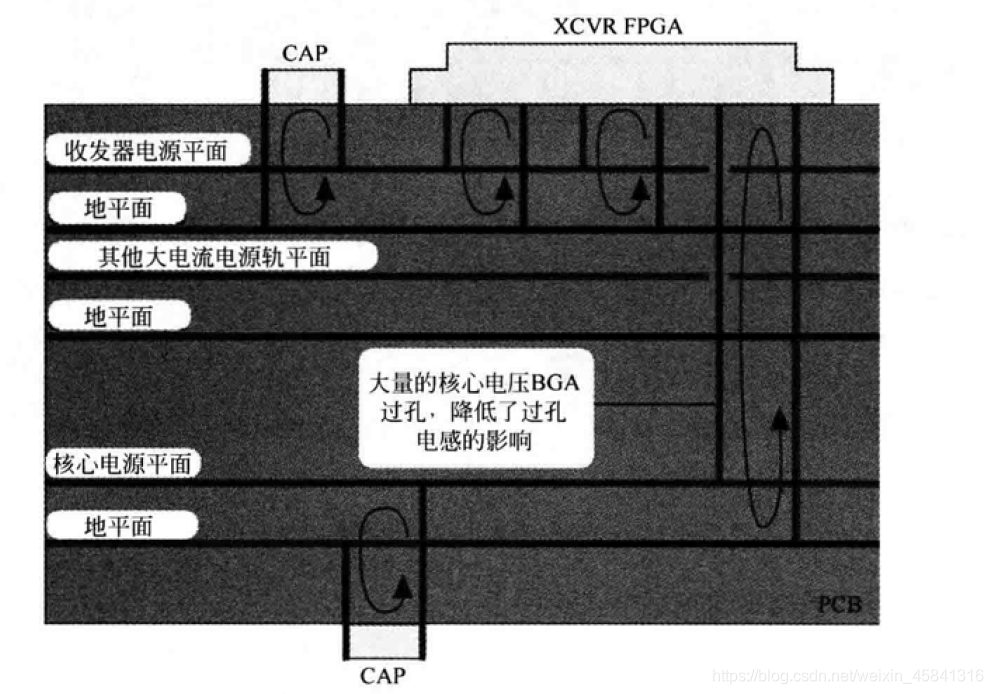

altera给出了一个大致的电源层分布原则:尽可能的将电源层放置在靠近fpga;与transceiver有关的电源平面布局;大电流电源的布局;pll电源的布局;叠层安排如下图所示:

1.3退耦电容

退耦电容可以在电源轨波动时为其提供少量的瞬态能量。pcb设计者如何比较恰当地使用电容以获取最佳的退耦效果。为此,xilinx分布了一个关于电源分配系统(PDS)设计的应用手册XAPP623https://ishare.iask.sina.com.cn/f/13505430.html;

1.3.1为何需要退耦电容

真实世界中的电容不仅具有作为支配属性的容抗,而且还具有感抗和阻抗。电容的二阶模型将会是一个RLC电路,也就是说,可以将一个退耦电容看做是一组电阻(R:表现为电容的等效串联阻抗ESR)、电感(L:表现为电容的等效串联感抗ESL)和电容(C:表现为电容的容抗)的串联组合。

理论上,电容上占主导地位的阻抗将由电容在低频和电感在高频上进行控制来实现。故一个真正的电容将同时在甚低频和甚高频具有一个高阻抗。通常会在某个频点时阻抗最小(称为电容的谐振频率),只有在这点上退耦电容才会提供最佳的滤除供电干扰的能力。

1.3.2计算电容值

altera为客户提供的电子数据表格实现了用户输入一定范围的容值到表格自动画出相应的阻抗图。另外注意的是:对于每次降低电容量级选择电容时,在该范围内选择的电容数据大约应增加1倍eg:两个0.1uf的电容--四个0.01uf的电容。

1.3.3电容的摆放

电容摆放位置的不佳将会导致寄生的电感的增加,退耦电容使用效果的下降。故长而窄的走线更趋于具有显著的感抗分量,并将会被添加到退耦电容的有效电感之中。

每一个电容引脚安排一个独立的过孔,而且过孔和引脚之间的连线要尽量短。如下图所示:

1.4小结

本篇主要讲解了fpga工程师需掌握的硬件电路设计的知识,特别是高速电路板设计的基础知识。以及如何安排pcb的叠层及各种供电电源的叠层和退耦电容的正确设计方案。

447

447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?