目录

一、实验目的

1、复习EDA的设计方法及原理;

2、学习Verilog HDL的设计方法,会使用Verilog HDL进行较复杂数字系统的设计。

二、数字秒表实验内容

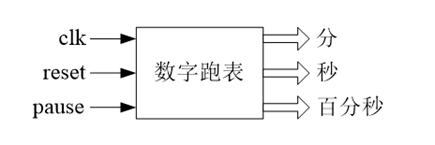

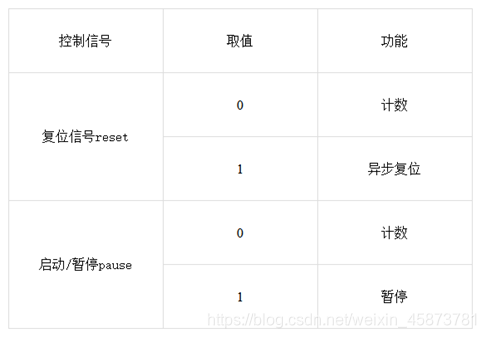

用Verilog HDL设计一个数字跑表,所需引脚和功能如下所示:

三、数字秒表实验步骤

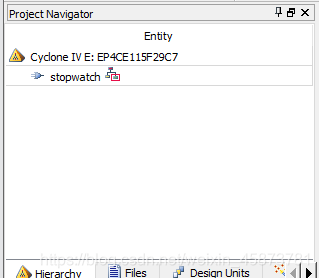

1.新建工程

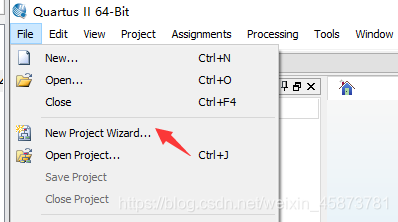

- 点击【File】→【New Project Wizard…】

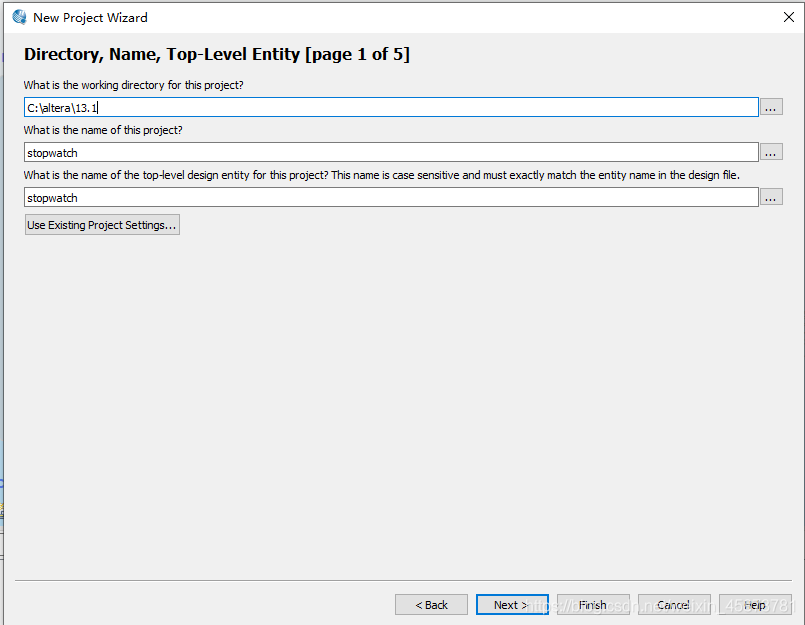

- 点击【Next >】,选择工程保存路径及工程名

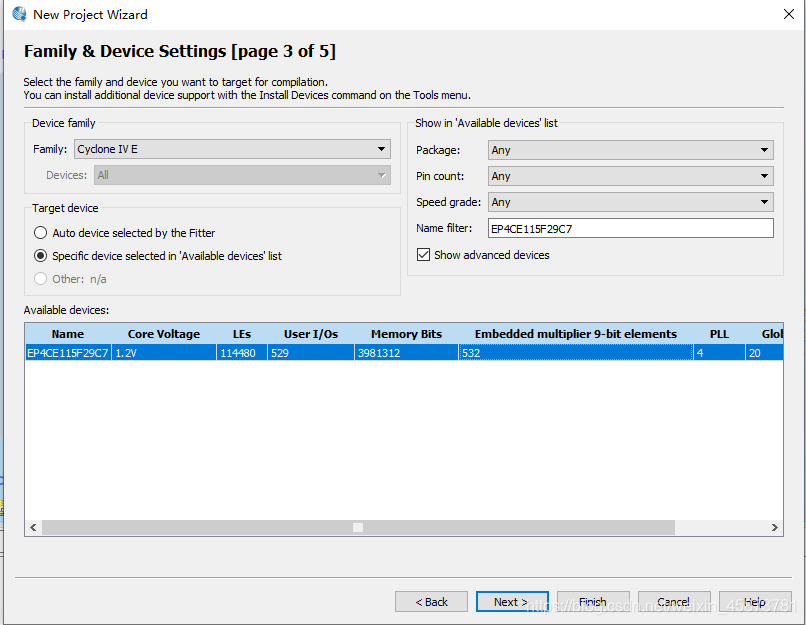

- 一直点next,知道见到如下界面,【Family】选择 Cyclone IV E,芯片选择 EP4CE115F29C7,然后点击【Next >】

- 点击finish

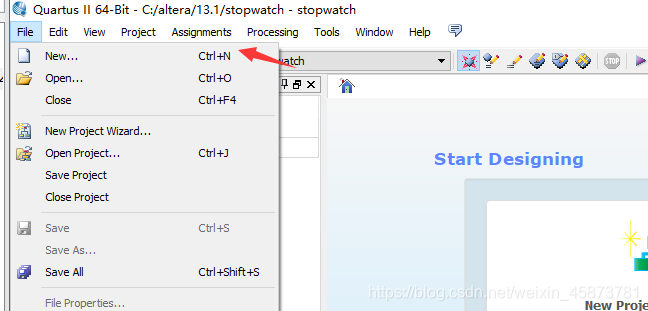

2.添加 Verilog 文件

- 点击【File】→【New…】

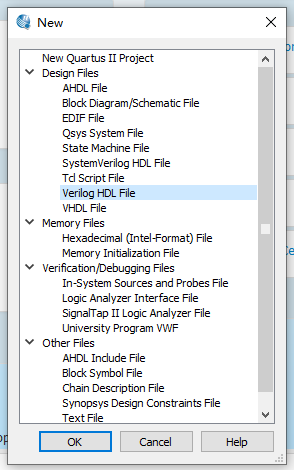

- 选择【Verilog HDL File】,再点击【OK】

写入如下代码

module stop_watch(

clk,

reset,

pause,

msh,

msl,

sh,

sl,

minh,

minl);

input clk, reset, pause;

output [3:0] msh, msl, sh, sl, minh, minl;

reg [3:0] msh, msl, sh, sl, minh, minl;

reg count1, count2;

always@(posedge clk or posedge reset) begin

if(reset) begin

{

msh, msl} <= 0;

count1 <= 0;

end

else if(!pause) begin

if(msl == 9) begin

msl <= 0;

if(msh == 9) begin

msh <= 0;

count1 <= 1;

end

else

msh <= msh + 1;

end

else begin

msl <= msl + 1;

count1 <= 0;

end;

end

end

always@(posedge count1 or posedge reset) begin

if(reset) begin

{

sh, sl} <= 0;

count2 <= 0;

end

else if(sl == 9) begin

sl <= 0;

if(sh == 5) begin

sh <= 0;

count2 <= 1;

end

else

sh <= sh + 1;

end

else begin

sl <= sl + 1;

count2 <= 0;

end

end

always@(posedge count2 or posedge reset) begin

if(reset) begin

minh <= 0;

minl <= 0;

end

else if(minl == 9) begin

minl <= 0;

本文介绍了如何使用Verilog HDL设计数字秒表并进行VGA显示的实验过程。首先,文章详述了创建Verilog HDL工程、编写代码、波形仿真的步骤。接着,对于VGA显示实验,同样涵盖了新建工程、编写Verilog代码、配置管脚以及烧录程序的详细步骤,最后展示了成功下载到开发板上的结果显示。

本文介绍了如何使用Verilog HDL设计数字秒表并进行VGA显示的实验过程。首先,文章详述了创建Verilog HDL工程、编写代码、波形仿真的步骤。接着,对于VGA显示实验,同样涵盖了新建工程、编写Verilog代码、配置管脚以及烧录程序的详细步骤,最后展示了成功下载到开发板上的结果显示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1936

1936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?