1.上游器件给下游器件同时提供时钟和数据叫做源同步接口,

上游器件只提供数据,由外部时钟源同时提供给上游和下游器件时钟的类型叫做系统同步接口。

源同步接口里包括了边缘对齐和中心对齐。

高速传输中一般使用源同步接口,比如高速的ADC和DAC。

在更高速的接口中,使用高速收发器替代了源同步接口,比如JEDSD204b,PCIE,SATA,USB3.0等。传输只有数据,使用CDR恢复时钟。

在源同步接口中,Tsu_slack = Tcycle + Tc_d + Tc_bd + Tc_fi - Tsu - Td_fi - Td_bd - Tco;等式中只有Tcycle在变化,所以只要在最快的频率下满足时序需求,在其他频率下也能满足。系统同步则不然。

Inputdelay_max与建立时间余量有关系,inputdelay_min与保持时间余量有关系。图中可以明显的看到。

在 create clock时,如果选择add this clock…不覆盖模式,则会为这个时钟添加两个约束,因为实际从pin脚进来的时钟不一定只有一种频率,其他同理。

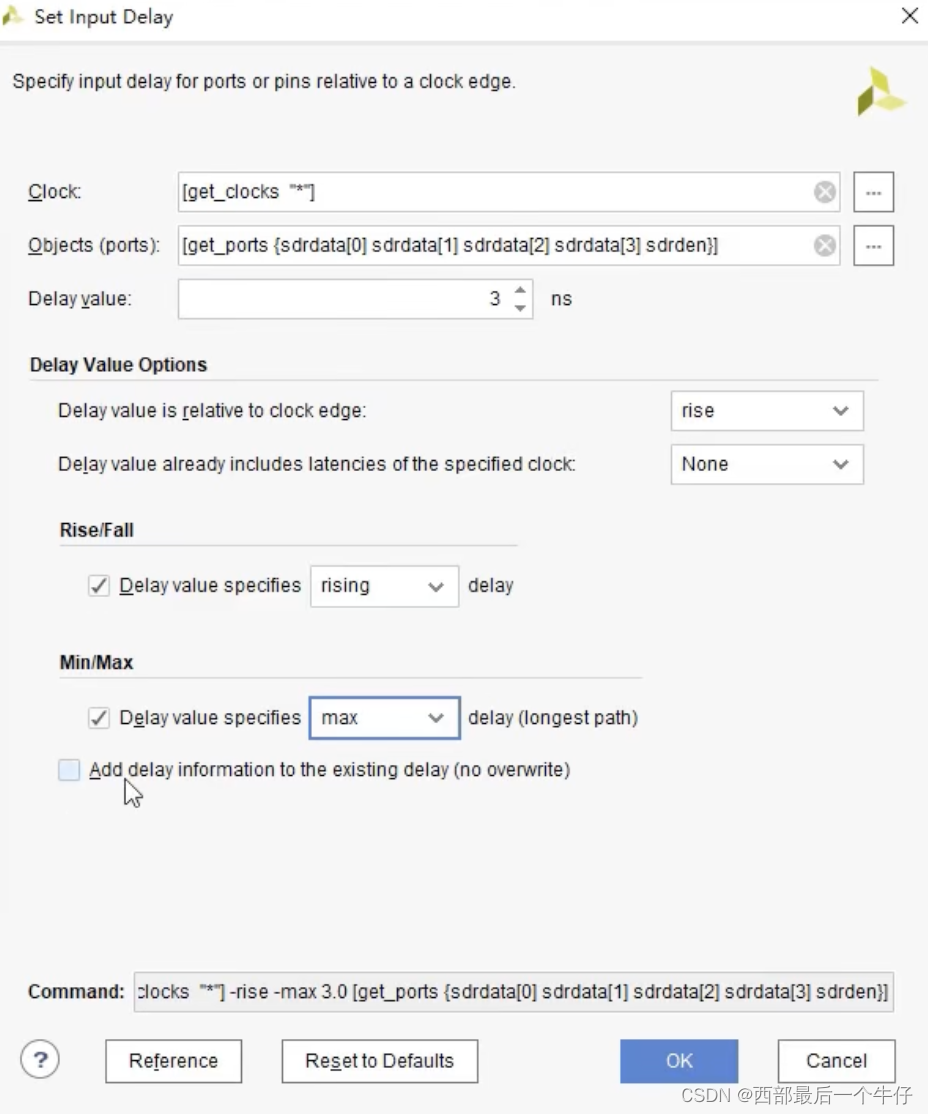

例:sdr模式下,时钟到达3ns后数据到达,T = 10ns,如何约束?

set_input delay min/max = 3ns。注意,在ddr模式下,添加下降沿或者上升沿时,需要选中前边说到的add delay,否则会覆盖之前的约束。

1636

1636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?