一、生成RAL model命令

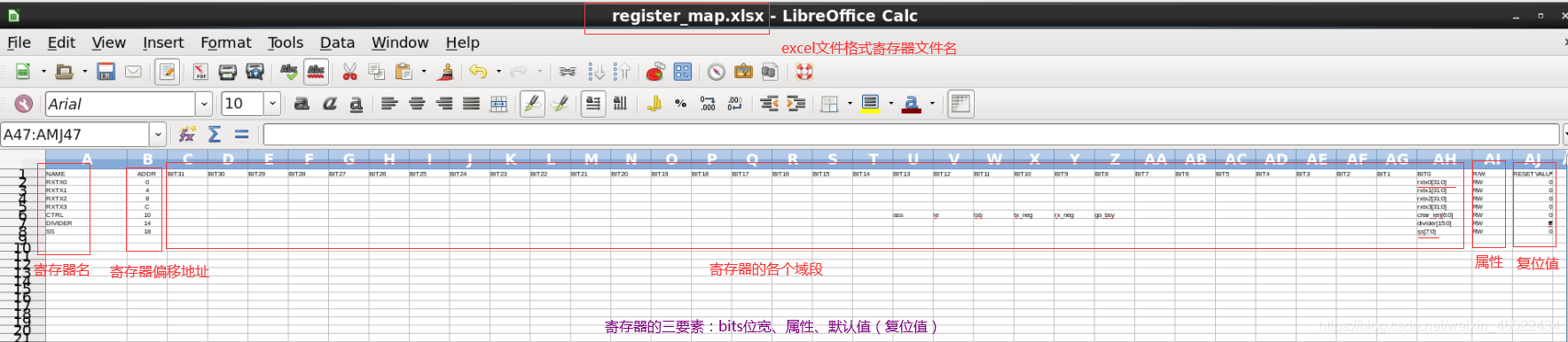

生成RAL model命令: ralgen [options] -t topname -I dir -uvm {filename.ralf}。ralgen是vcs工具的命令,输入对象是*.ralf文件,生成*.sv文件。.ralf文件可以通过excel表格生成。典型的寄存器表格文件如下。

- -uvm —— 生成的代码基于UVM方法学

- -t topname —— RALF文件中顶层模块的名称,生成的RAL model文件名称为ral_topname.sv

- -I dir(注意是i的大写,不是L的小写;可选项) —— ralgen搜索源文件的可选目录列表

- filename.ralf —— 包含Ralf描述的文件名。

命令执行完毕后该文件会转换成目标ral_topname.sv文件

Options可选项包括有:(更多详情

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+