一、DDR Controller功能

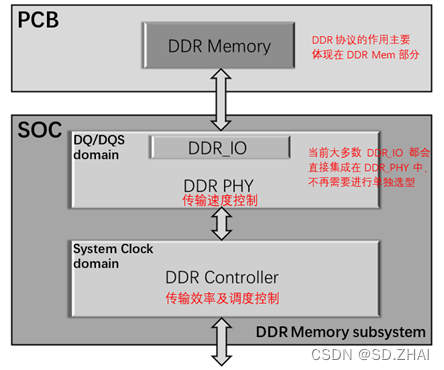

DDR Controller是Memory子系统的重要组成部分之一,另一部分为DDR_PHY(含DDR_IO)。DDR Controller主要承担其它子系统(如CPU)与Memory子系统进行数据交互时的传输效率及调度,DDR_PHY主要负责数据交互过程中的传输速度。其结构简图组成如下:

DDR Controller主要功能如下:

- 命令调度:为了提高对DDR颗粒的访问效率,DDRC会对总线AXI的访问命令进行重新分配调度,提高数据交互传输效率。

- 协议转换:DDRC接受AXI总线发过来的命令后,会将其转化为DDR协议类型的Burst命令,并按照DDR协议将其发送给Memory颗粒;同时读取DD

本文详细介绍了DDR Controller的功能,包括命令调度、协议转换和兼容性,并探讨了DDR Controller的效率计算方法。接着,文章揭示了DDR Controller的架构,如AXI Interface、Command Split、Write Data Buffer等组件的工作原理,以及如何通过Command Reorder优化传输效率,以减少Page Conflict。DDR Controller在内存系统的高效运行中起着关键作用。

本文详细介绍了DDR Controller的功能,包括命令调度、协议转换和兼容性,并探讨了DDR Controller的效率计算方法。接着,文章揭示了DDR Controller的架构,如AXI Interface、Command Split、Write Data Buffer等组件的工作原理,以及如何通过Command Reorder优化传输效率,以减少Page Conflict。DDR Controller在内存系统的高效运行中起着关键作用。

订阅专栏 解锁全文

订阅专栏 解锁全文

8526

8526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?