1、概念

竞争(competition):

说法一:在组合逻辑中,信号由于经由不同路径达到输出端,由于每条途径延迟时间不同,达到输出门的时间就有先有后,这种现象就称之为竞争。

说法二:门电路的两个输入信号同时向反向的逻辑电平跳变(一个从1跳变到0,另一个从0跳变到1)的现象称之为竞争。

说法一从原理上去概述,说法二从现象上去概述,两种说法都对,要达到冒险,缺一不可,但两者都满足不一定会有冒险。

冒险(risk):

多路信号电平值发生改变时,在信号变化的瞬间,组合逻辑的输出有先有后,并不是同时变化,往往会出现一些尖峰信号,这些尖峰信号称之为毛刺,如果一个电路中出现毛刺,就说明该电路存在冒险。

竞争冒险(competition risk ):

由于竞争而在电路输出端可能产生尖峰脉冲的现象就称之为竞争冒险。

如下图的简单电路,由于门电路的延时,A非相对于A信号会滞后一段是时间(时间由工艺决定),这就会导致输出产生一个干扰脉冲。

2、竞争与冒险的关系

有竞争不一定有冒险,但出现了冒险就一定存在竞争。 如果两个跳变信号,其中一个在到达VIL(max)或VIH(min)时另一个已经到达稳定状态,则此种情况下竞争不会导致冒险。

3、竞争与冒险的判断

判断电路中是否存在静态冒险,主要有两种方法:代数法与卡诺图法。

(1)代数法

对于任意组合电路,当其表达式的某种组合会导致出现F=A+(~A)(A取反)或者F=A(~A)时,就会产生静态冒险,理由反相器必定会产生延时。比如下面这个表达式:

当输入Y与Z稳定在1时,F应该稳定产生1,而X发生变化时,就会导致电路产生0的窄脉冲,也就产生了静态1型冒险。静态0型冒险类似。

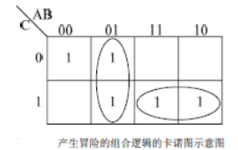

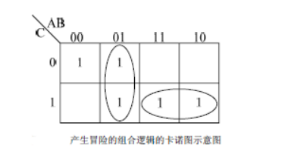

(2)卡诺图法

当对卡诺图化简时存在相切的最小项或者最大项时,电路中就可能存在竞争冒险。如下图所示,所圈出最小项存在相切的现象,就产生了冒险。

4、竞争与冒险解决方法

(1)修改逻辑设计,增加冗余项:(设计中)

对于给定的逻辑 Y=AB+ÃC,当BC都为1的时候,若A值改变,则会发生竞争。所以可以添加冗余项:Y=AB+ÃC+BC

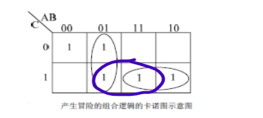

分析有无竞争冒险:画出函数的卡诺图,检查有无几何相邻的逻辑项,有则可能产生竞争冒险。

如下图所示电路,可以增加冗余项来抵消静态冒险,具体做法是在相切的最小项中增加一个最小项,使相切的点合二为一。

原来的表达式为:

当B与C均为1时,就会产生静态冒险,而圈上相切项之后,表达式为:,这样便不会再产生冒险。

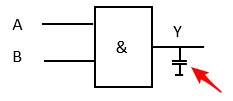

(2)引入滤波电容:输出端并接一个不大的滤波电容

缺点:输出波形边沿变坏。

(3)引入选通脉冲

(4)格雷码计数器

对于一般的二进制或十进制计数器,在计数时,将有多bit信号同时跳变。使用格雷码将避免毛刺的出现,因为格雷码让计数器的输出每次只有一次跳变。

(5)利用D触发器对毛刺不敏感的特性,对组合逻辑输出加寄存器。可以通过改变设计,破坏毛刺产生的条件来减少毛刺的发生。(组合逻辑输出加寄存器)毛刺并不是对所有的输入都有危害,对于D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且不满足数据的建立和保持时间,就不会对系统造成危害,因此可认为D触发器的D输入端对毛刺不敏感。根据这个特性,应当在系统中尽可能采用同步电路,因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间。

(6)信号同步法:

A、信号延时同步法

其原理是在两级信号传递的过程中加一个延时环节,这里的信号延时可以是数据信号的延时也可以是时钟信号的延时。

B、状态机控制

使用状态机可以实现信号的同步和消除毛刺的目的。在传输比较复杂的多模块系统中,由状态机在特定的时刻分别发出控制特定模块的时钟信号或者模块使能信号,状态机的循环控制就看以使整个系统协调运作,同时减少毛刺信号。

5、在verilog编程时需要注意以下几点:

(1)时序电路建模时,用非阻塞赋值。

(2)锁存器电路建模时,用非阻塞赋值。

(3)用always和组合逻辑建模时,用阻塞赋值。

(4)在同一个always块中建立时序合组合逻辑模型时,用非阻塞赋值。

(5)在同一个always块中不要既用阻塞赋值又用非阻塞赋值。

(6)不要在多个always块中为同一个变量赋值。

5898

5898

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?