学习不能稀里糊涂,要学会多思考,发散式学习以及总结:

FPGA作为一种器件,只是实现目的的一种方法,过度追求实现的技术细节(用hdl还是hls,用啥芯片,用啥接口)容易只见树木不见森林。工具软件的用法也好,器件的架构也好,语言孰优孰劣的争论也罢。工程应用里大概更多应该去考虑适合的实现方式,现在software define network/flash/xxx,已然大势所趋,算法是纲,纲举目张。是因为在实现上需要有流水线,多路并行,快速部署的目的所以考虑使用FPGA,而不是为了使用而使用。

不管实现目的的方法是FPGA还是DSP甚至是GPU,这些都是工具,工程师的核心竞争力除了在于熟练地掌握开发的技巧。更重要的在于信号与系统、数字信号处理、图像处理之类的让你了解算法、优化算法的基石;以及数字电路、微机原理、处理器体系结构这些让你了解为什么这些工具要这样设计,要这样发展的课程(系统学习一点体系结构,那么这些数据级并行、指令级并行、线程级并行的处理器就不再陌生了)工程师应该顶天(了解应用,了解算法)也应该立地(了解工具,掌握技巧)。

——引用某个大佬的话,作为学习共勉

简单来说就是:FPGA是工具用来搬砖,更多的知识在FPGA之外

在上一节接口描述的时候,总结了在使用接口的时候,我们应该关注以下接口:时钟,复位,数据,使能以及配置(回环测试还是外接)和状态(链路状态)这些接口。本节我将通过这些接口进行实例分析。

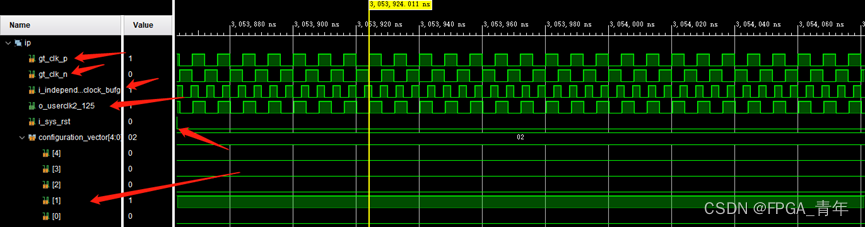

一、时钟

gt_clk_p/n:外部接入的GT收发器的差分参考时钟125Mhz。

i_independet_clock_bufg:独立时钟,用作IDELAYCTRL和主GT收发器复位逻辑的参考时钟200Mhz。

o_userclk2_125:由IP核产生的GMII的时钟源125Mhz,可以理解为数据链路层与IP核PMA层间通信的时钟。

二、复位

i_sys_rst:IP核的复位信号,设计常用的复位信号多由时钟IP核的locked信号

三、配置(回环测试还是外接)

本次实例仿真,是以太网的的回环测试,在接口与框架里边已经介绍过了,仿真采用回环模式,将configuration_vector这个接口配置为(5’b00010),以太网IP核就会在PMA层进行回环测试,它会将内部的TXP/TXN与RXP/RXN进行回环连接。

四、状态(链路状态)

观测链路状态信号,这个信号是以太网链路链接的标志,即status_vector接口的最低位置,它也是整个工程开始执行的重要信号,可以作为程序开始的使能。

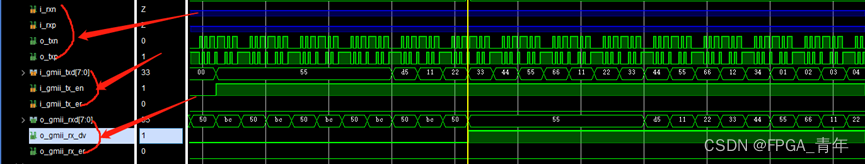

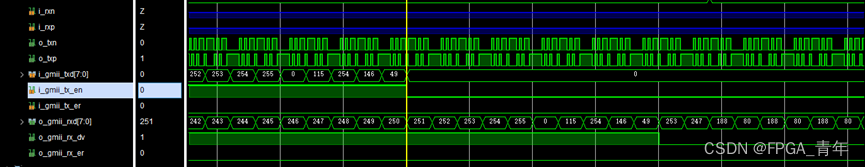

五、数据、使能

TXP/TXN,RXP/RXN是与外部通信的接口,由于本次设计采用的是内部循环,所以这两对差分接口我们暂时没有用到,就不用关心。GMII接口当使能en/dv拉高的时候,txd和rxd数据有效。关于传输的数据(5555…d5…)这里就不再做介绍了,在第一篇文章中的以太网协议中已经介绍过。

至此FPGA以太网学习告一段落,本系列是为了将学习过的IP核知识进行总结,以备以后学习使用。

记录美好学习,从总结开始;💪

8437

8437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?