四、生成.mcs文件

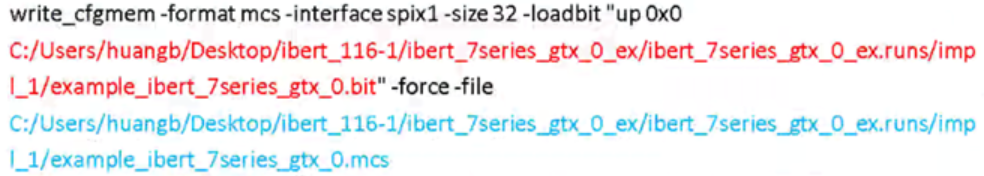

1.在“TCl Cons…”选项框中输入如下内容:

红色文字部分是第三步中生成的.bit文件的地址及文件名,蓝色部分是即将生成的.mcs文件的地址及文件名;

2.输入完成后,单击回车,文件开始编译,出现如下提示则编译完成:

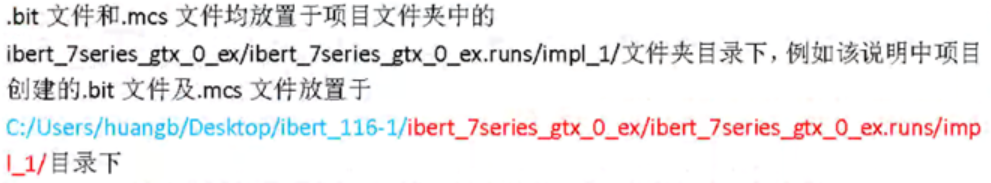

蓝色文字部分为创建新项目时自定义的项目文件夹目录,红色文字部分是生成的.bit文件及.mcs文件后自动生成的文件夹地址;

.mcs文件于测试准备阶段烧写入待测试板卡中;.bit文件于测试过程中提供在线调试使用。

五、测试准备

1.将待测试的输入输出板卡烧写.mcs文件;

2.待测试输出板插入FPGA烧写器,与PC连接;

3.测试PC与待测试PC处于同一网段;

4.测试PC安装Vivado及SecureCRT Portable测试工具。

六、连接设备

1.待测设备开机;打开SecureCRT Portable测试工具;

2.输入主机名(即IP地址),用户名:root;点击“连接”;

3.显示如下界面即登录成功:

七、读取眼图

1.打开Vivado,点击Open hardware manager:

2.点击Open target,在下拉菜单选择Auto connect;

3.出现下图则连接成功:

出现下图所示,则连接失败:

需要在线烧写.bit文件;

4.连接成功后,点击Create links:

5.在弹出窗口中多次点击加号,将所有通道添加到下方,点击OK;

6.在成功连接的通道处右键,选择Create Scan:

7.弹出的窗口中,点击OK,等待眼图生成。

FPGA基础–基于Vivado的眼图测试(二)

最新推荐文章于 2024-07-08 11:08:50 发布

1975

1975

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?