@[TOC](ip核中的 srst(系统复位引脚低电平时有效) )

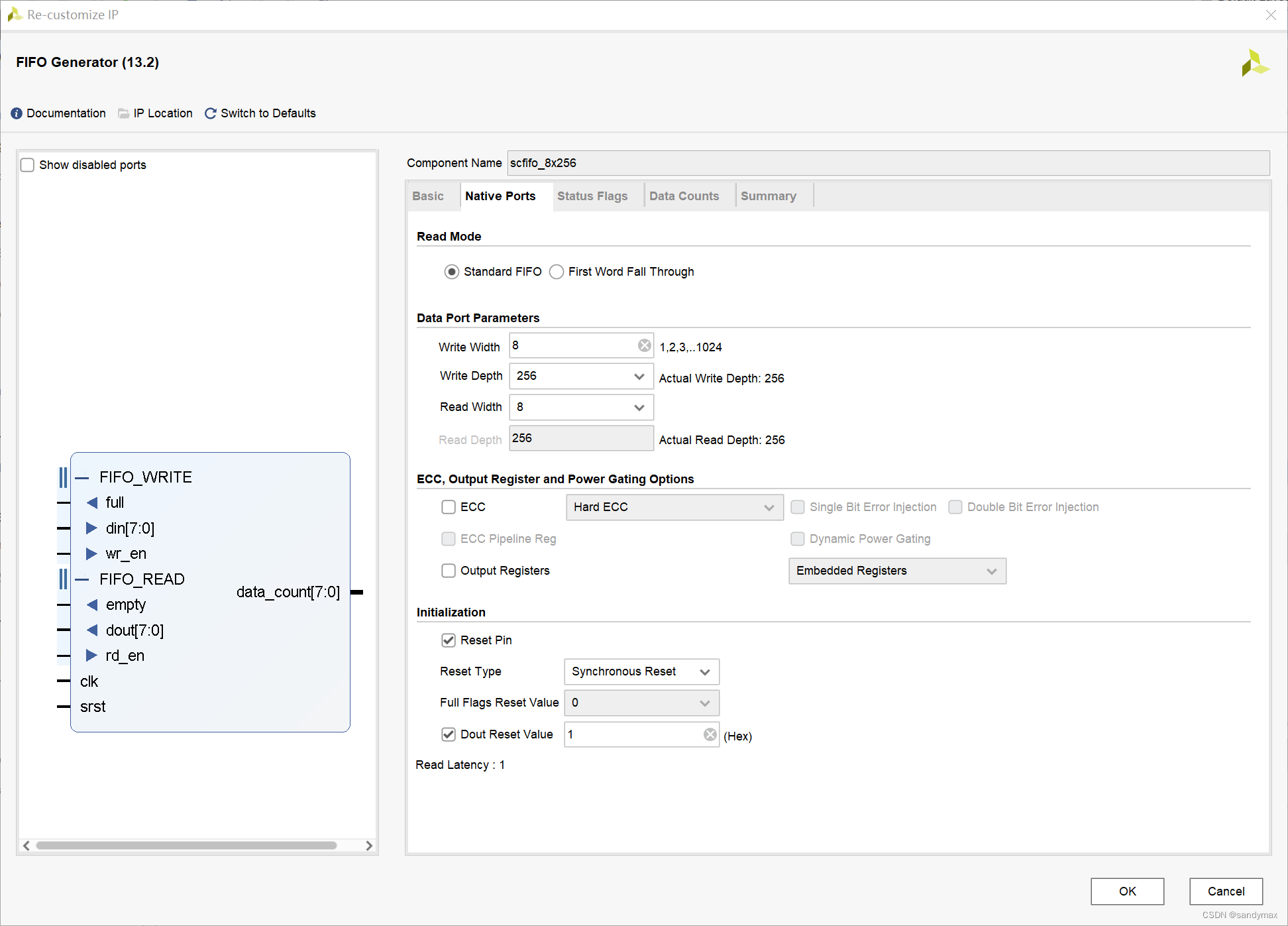

1. ip 核设置

2. fifo.v文件

module fifo

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire [7:0] pi_data ,

input wire rd_req ,

input wire wr_req ,

output wire empty ,

output wire full ,

output wire [7:0] po_data ,

output wire [7:0] data_count

);

scfifo_8x256 fifo_inst

(

.clk (sys_clk ), // input wire clk

.srst (sys_rst_n ), // input wire srst

.din (pi_data ), // input wire [7 : 0] din

.wr_en (wr_req ), // input wire wr_en

.rd_en (rd_req ), // input wire rd_en

.dout (po_data ), // output wire [7 : 0] dout

.full (full ), // output wire full

.empty (empty ), // output wire empty

.data_count(data_count) // output wire [7 : 0] data_count

);

endmodule

3. tb_fifo.v文件

`timescale 1ns/1ns

module tb_fifo();

reg sys_clk ;

reg sys_rst_n ;

reg [7:0] pi_data ;

reg rd_req ;

reg wr_req ;

reg [1:0] cnt ;

wire empty ;

wire full ;

wire [7:0] po_data ;

wire [7:0] data_count ;

initial

begin

sys_clk = 1'b0;

sys_rst_n <= 1'b1;

#15

sys_rst_n <= 1'b0;

end

always #10 sys_clk = ~sys_clk;

//cnt

always@(posedge sys_clk or posedge sys_rst_n)

if(sys_rst_n == 1'b1)

cnt <= 2'd0;

else if(cnt == 2'd3)

cnt <= 2'd0;

else

cnt <= cnt + 1'b1;

//wr_req 写使能

always@(posedge sys_clk or posedge sys_rst_n)

if(sys_rst_n == 1'b1)

wr_req <= 1'b0;

else if(cnt == 2'd3 && rd_req == 1'b0)

wr_req <= 1'b1;

else

wr_req <= 1'b0;

//pi_data

always@(posedge sys_clk or posedge sys_rst_n)

if(sys_rst_n == 1'b1)

pi_data <= 8'd0;

else if(pi_data == 8'd255 && wr_req == 1'b1)

pi_data <= 8'd0;

else if(wr_req == 1'b1)

pi_data <= pi_data + 1'b1;

//rd_req 读使能

always@(posedge sys_clk or posedge sys_rst_n)

if(sys_rst_n == 1'b1)

rd_req <= 1'b0;

else if(full == 1'b1)

rd_req <= 1'b1;

else if(empty == 1'b1)

rd_req <= 1'b0;

fifo fifo_inst

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.pi_data (pi_data ),

.rd_req (rd_req ),

.wr_req (wr_req ),

.empty (empty ),

.full (full ),

.po_data (po_data ),

.data_count (data_count)

);

endmodule

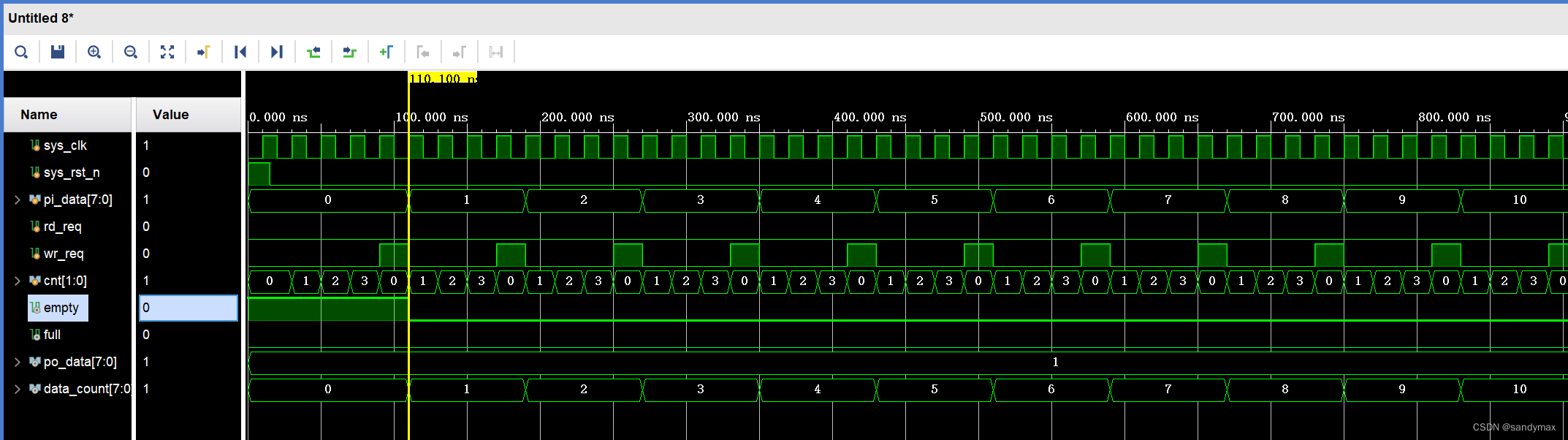

4. vivado 仿真波形

wr_req,写使能信号第一次触发后,empty信号置0

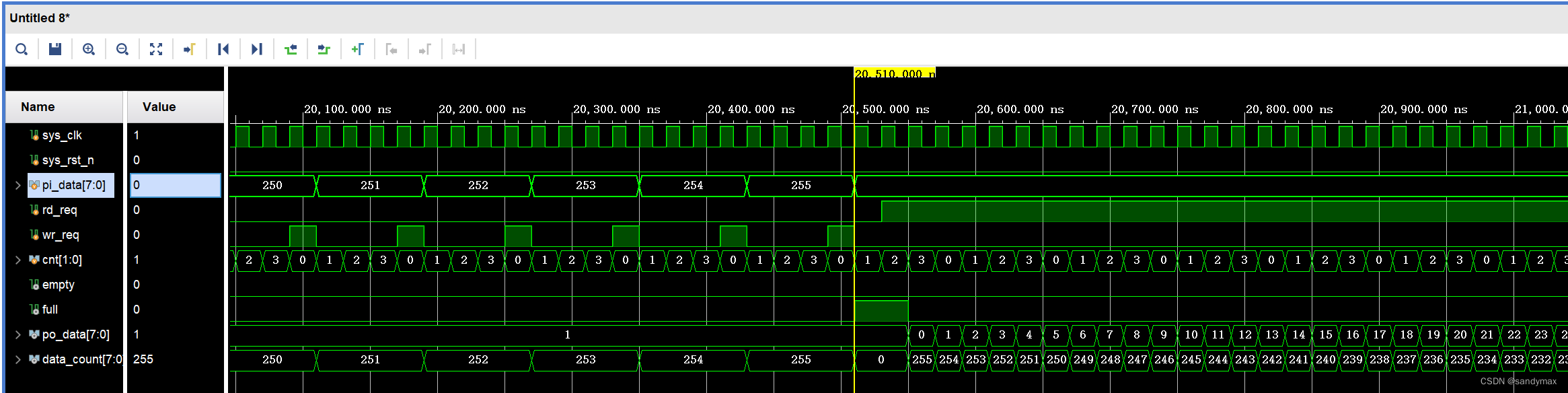

写满256个数据后,full信号出现两个周期的高电平;

rd_req信号置1后开始读取数据,此过程中写使能信号wr_req一直为低电平

data_count计数器在写过程增加;读过程减小

写过程4个周期一次,读过程1个周期一次

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?