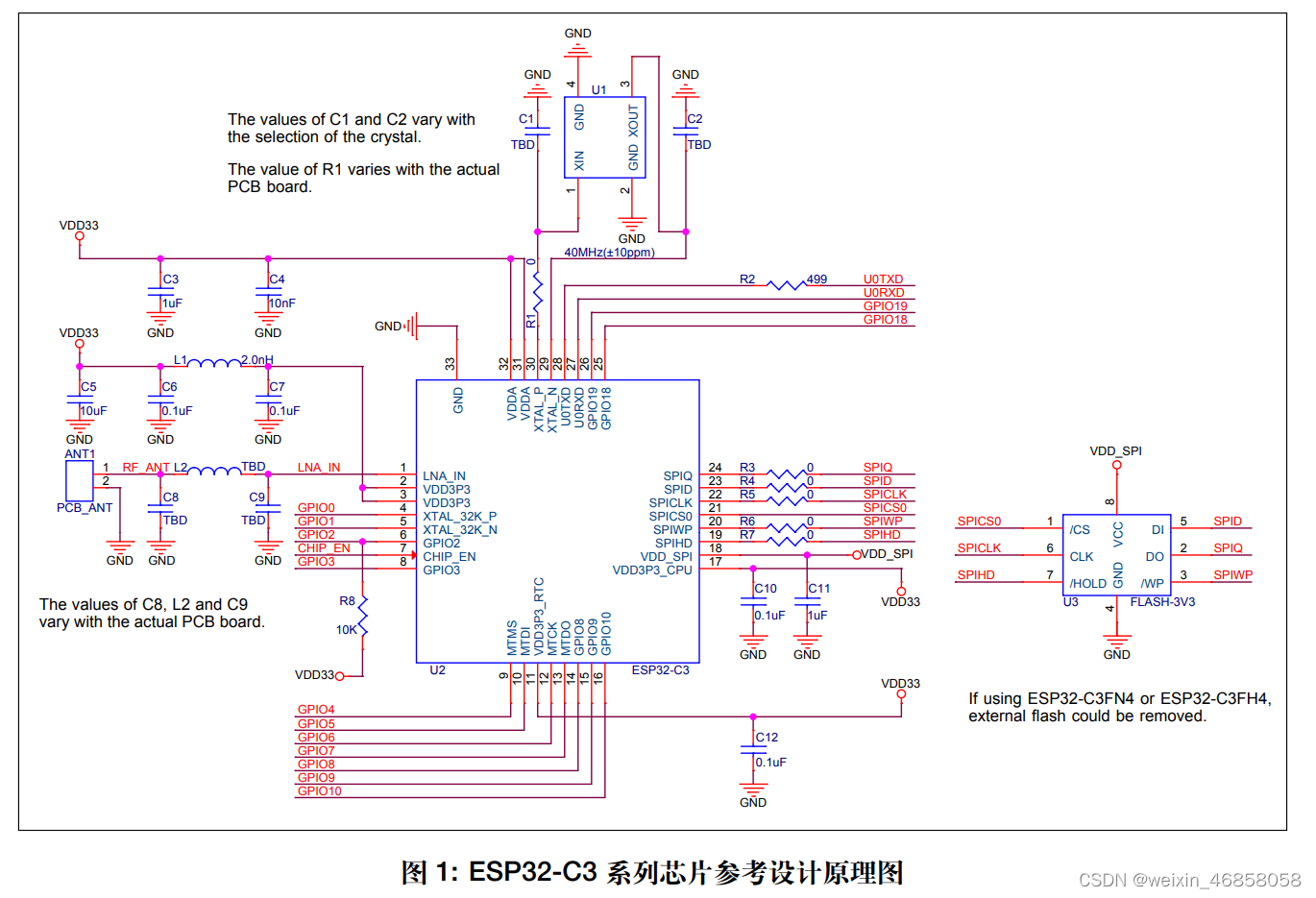

共33个管脚。

电源管脚7个,数字电源管脚11、17、18、模拟电源管脚2、3、31、32。18管脚可复用。

复位管脚1个,7号。

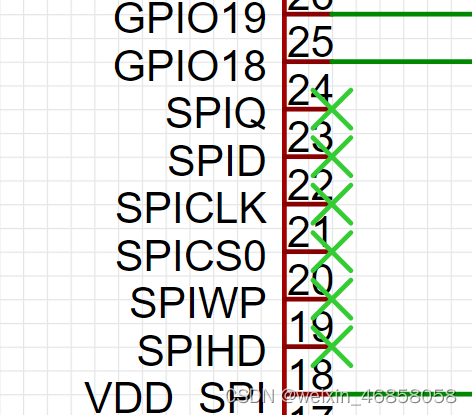

Flash管脚,6个,19-24为外接Flash管脚可不接。

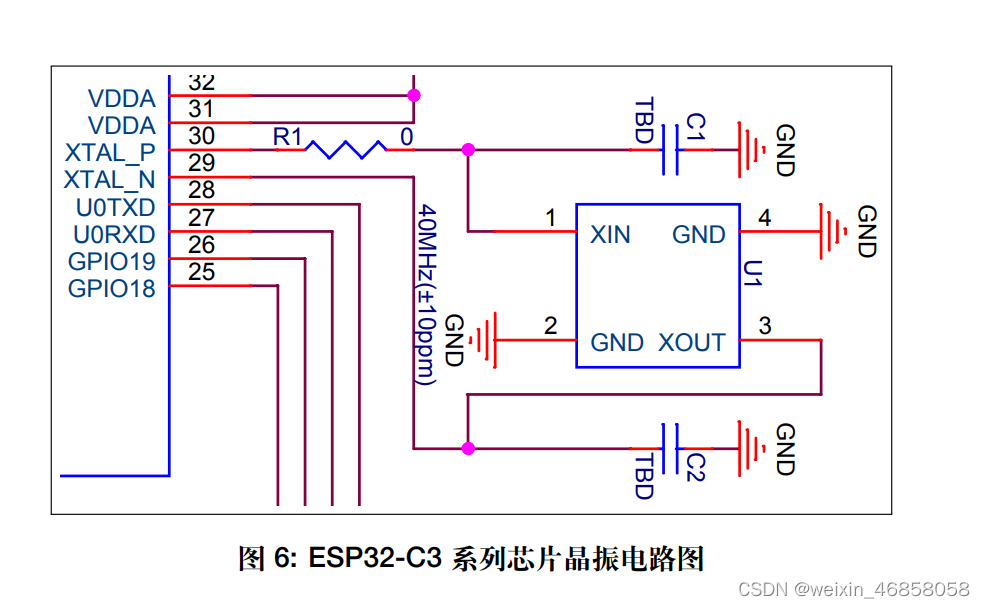

晶振时钟管脚4个,29,30为外部晶振,4、5为时钟管脚可不接,可复用。

UART管脚 2个 20,21可不接,可复用。

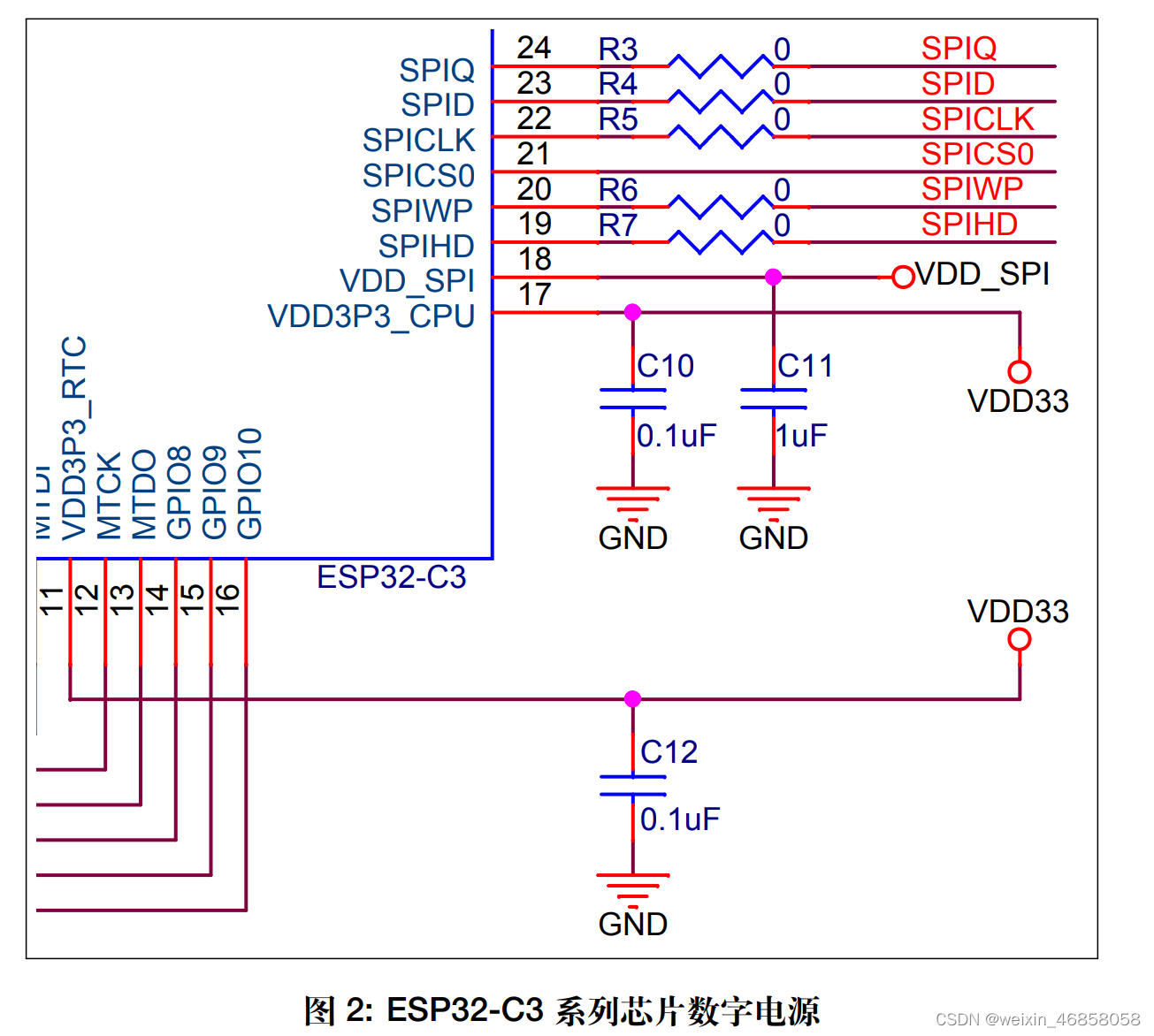

2.1.1数字电源管脚。11引脚 时钟RTC IO、17管脚为CPU IO 数字电源VDD ,靠近数字电源管脚处增加0.1μF电容。18引脚为串行外设SPI IO数字电源引脚,靠近数字电源管脚处增加1μF电容 。

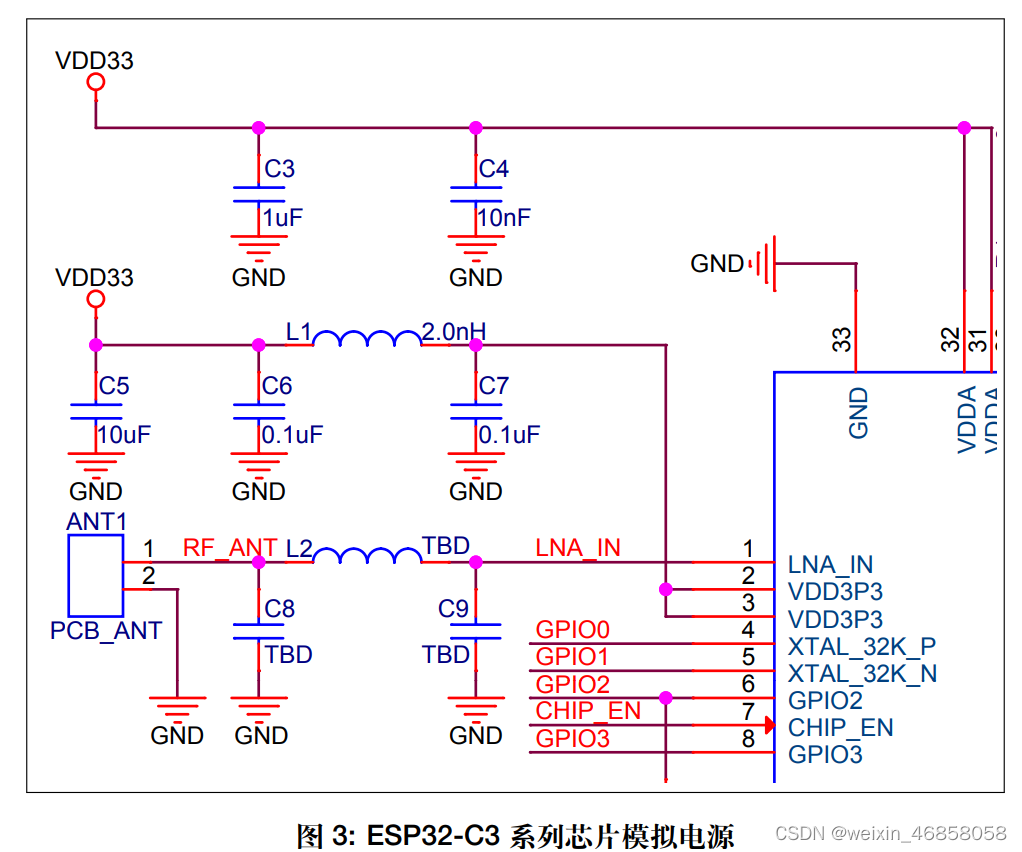

2.2.2模拟电源管脚。管脚 2、管脚 3、管脚 31 和管脚 32 为模拟电源管脚。当 ESP32-C3 系列芯片工作在 TX 时,瞬间电流会加大,往往引起电源的轨道塌陷。在电源走线上增加一个 10 µF 电容,该电容可与 0.1 µF 电容搭配使用。另外,在靠近管脚 2 和管脚 3 处还需添加 LC 滤波电路,用于抑制高频谐波,同时请注意该电感的额定电流最好在 500 mA 及以 上。其余电源管脚请参考图 3 放置相应的去耦电容。

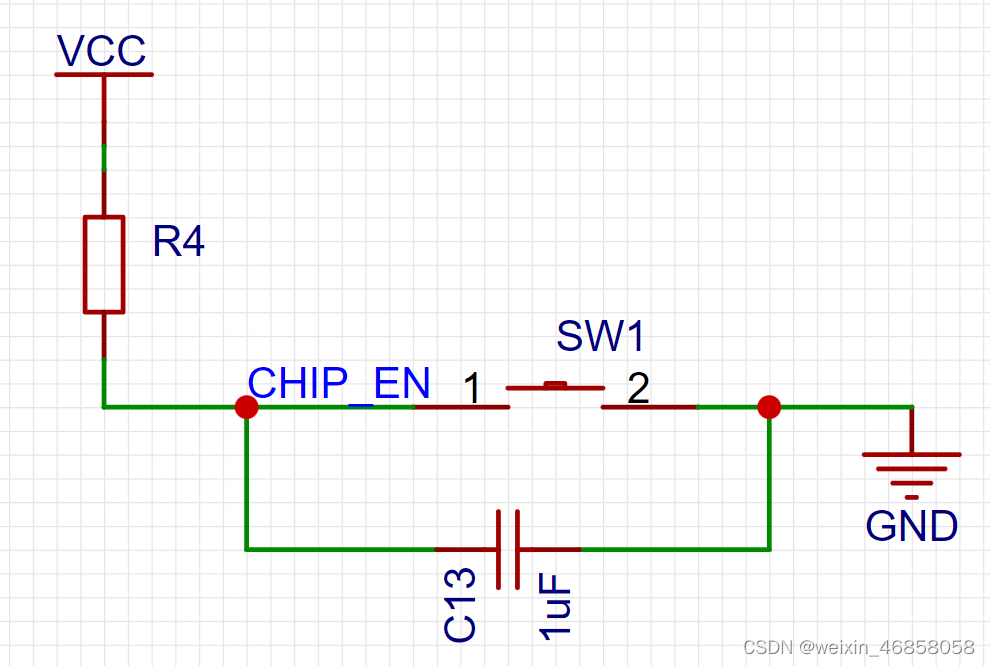

2.2 CHIP_EN 管脚7。处需要增加 RC 延迟电路。RC 通常建议为 R = 10 kΩ,C = 1 µF,但具体数值仍需根据电源的上电时序和芯片的上电复位时序进行调整。复位可使用 CHIP_EN 管脚。当 CHIP_EN 为低电平时,建议复位电平 (VIL_nRST ) 范围为 (–0.3 ~ 0.25 × VDD) V(其中 VDD 为 I/O 的供电电源)。为防止外界干扰引起重启,CHIP_EN 引线需尽量短一 些,且最好加上拉电阻和对地电容。该管脚不可旋空。参考下图。

2.3 外接Flash管脚 19-24管脚,用内置4MbFlash可以不外接。

2.4.1 晶振电路 管脚29,30. C1 、C2取22μF 。R1,0欧姆电阻。

2.4.1 RTC外接管脚,不接时管脚4\5释放出来。

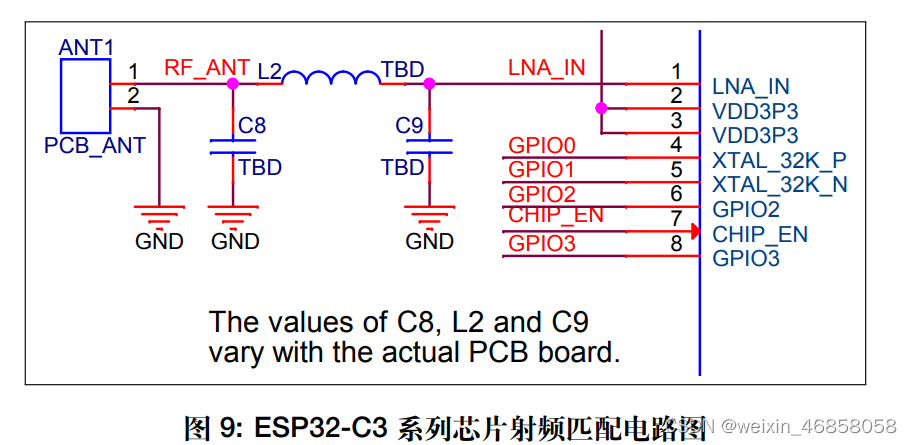

2.5 天线 管脚1 接天线,建议Π型CLC滤波天线设设计。

2.6 UART 可以不接,需要的话要接499偶电阻抑制谐波

2245

2245

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?