文章目录

The GIC logical components

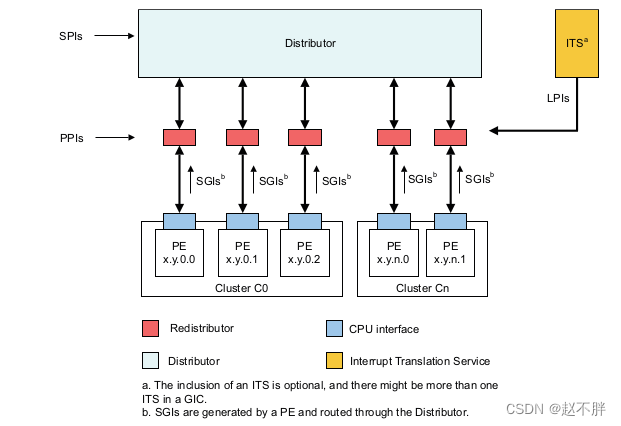

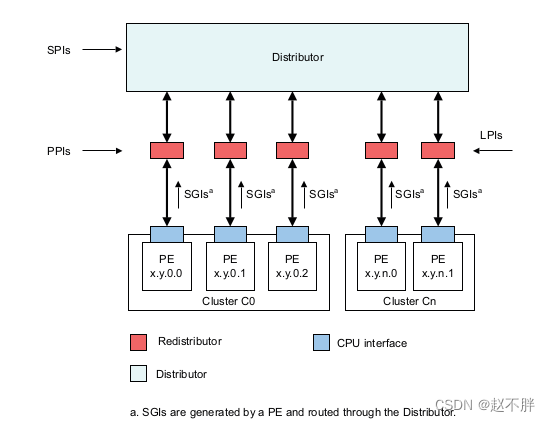

GICv3体系结构由一组逻辑组件组成:

- A Distributor.

- A Redistributor for each PE that is supported.

- A CPU interface for each PE that is supported.

- Interrupt Translation Service components (ITS), to support the optional translation of

events into LPIs.

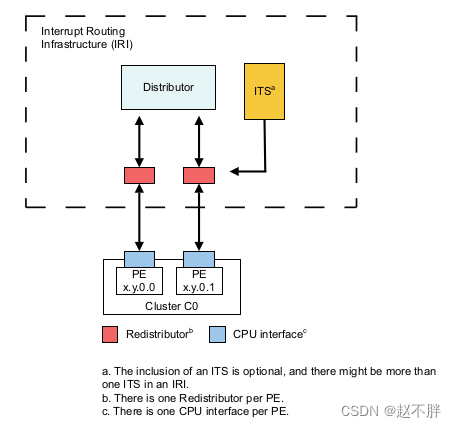

Distributor、Redistributor和ITS统称为IRI

CPU interface 在所有实现的异常级别处理物理中断如下:

- 转换为LPI的中断可选择通过ITS路由到Redistributor 和CPU interface.

- PPI直接从源路由到本地Redistributor。

- SPIs通过Distributor路由到目标Redistributor和相关的CPU interface。

- SGI由软件通过CPU interface和Redistributor生成。然后,它们通过 Distributor到一个或多个目标Redistributor和相关联的CPU interfaces。

在GICv3中,ITS是一个可选组件,它将事件转换为物理LPI。

- 通过访问Redistributors中的寄存器支持直接LPI。

- LPI支持由ITS提供。

一个实现只能支持其中一种方法。

在GICv4中,必须包含至少一个ITS,以支持虚拟LPI的直接注入。

包含ITS的实现中的GI:

不包含ITS且支持直接LPI的实现中的GIC:

Distributor

Distributor执行中断优先级排序,并将SPI和SGI分发到连接到系统中PE的Redistributors和CPU interfaces。Distributor寄存器由GICD_前缀标识。

GICD_CTLR为以下各项提供全局设置:

- 启用affinity routing

- 禁用security

- 启用Secure and Non-secure Group 1中断.

- 启用Group 0中断

对于SPIs,Redistributors提供了一个编程接口,用于:

- 启用或禁用SPI。

- 设置每个SPI的优先级。

- 每个SPI的路由信息。

- 将每个SPI设置为电平敏感或边缘触发。

- 生成基于消息的SPI。

- 将每个SPI分配给中断组。

- 控制SPI的pending和actiive状态。

Interrupt translation service, ITS

ITS是GICv3体系结构中的一种可选硬件机制,它将LPI路由到适当的Redistributor。软件使用命令队列配置ITS。内存中与ITS关联的表结构将与设备关联的EventID转换为PE的挂起INTID。

ITS在GICv4中不是可选的,所有GICv4的实现必须至少包含一个ITS。

Redistributor

Redistributor是IRI的一部分,连接到PE的CPU interface。Redistributor使用内存中的数据结构保存所有物理LPI的控制、优先级和pending信息。Redistributor中的两个寄存器指向这些数据结构:

- GICR_PROPBASER.

- GICR_PENDBASER.

在GICv4中,Redistributor还包括用于处理虚拟LPI的寄存器,这些虚拟LPI由ITS转发到Redistributer并直接转发到VM,而不涉及管理程序。这被称为将虚拟中断直接注入VM。

在GICv4中,Redistributor使用内存中保存的数据结构共同托管所有虚拟LPI的控制、优先级和pending信息。两个寄存器在Redistributor中指向以下数据结构:

- GICR_VPROPBASER.

- GICR_VPENDBASER.

在支持LPI但不包括ITS的实现中,GICR_*寄存器包含一个简单的内存映射接口,用于发送和控制物理LPI。

Redistributor为由GICR_前缀标识。 Redistributor为以下各项提供了编程接口:

- 识别、控制和配置支持的功能,以实现中断和中断路由。

- 启用或禁用SGI和PPI。

- 设置SGI和PPI的优先级。

- 将每个PPI设置为水平敏感或边缘触发。

- 将每个SGI和PPI分配给中断组。

- 控制SGI和PPI的pending状态。

- 控制SGI和PPI的active状态。

- 所连接PE的电源管理支持。

- 在支持LPI的情况下,内存中支持相关中断属性及其pending状态的数据结构的基址控制。

在支持GICv4的情况下,内存中支持相关虚拟中断属性及其pending状态的数据结构的基址控制。

CPU interface

GIC体系结构支持CPU interface,该接口为系统中的PE提供寄存器接口。每个CPU interface提供一个编程接口,用于:

- 根据实施的安全状态,实现中断处理的一般控制和配置。

- Acknowledging 中断。

- 执行优先级下降。

- 中断停用。

- 为PE设置中断优先级掩码。

- 定义PE的抢占策略。

- 确定PE的最高优先级pending中断。

CPU interface有几个组件:

- 允许软件的监督级别控制物理中断的处理的组件。与此相关的寄存器由ICC_前缀标识。

- 允许软件的监督级别控制虚拟中断的处理的组件。与此相关的寄存器由ICV_前缀标识。

- 允许hypervisor控制pending中断设置的组件。与此相关的寄存器由ICH_前缀标识。

在EL2处可访问的系统寄存器用于控制PE的活动、挂起、活动和挂起虚拟中断列表,这些寄存器由ICH_前缀标识。

287

287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?