目录

目录

目录

CSR寄存器模块

八个控制状态寄存器(csr):

假设mode的值为0直接模式,则全部的异常响应时处理器均跳转到base值指示的pc地址 。

Riscv架构定义异常的返回地址由机器模式异常CSR寄存器mepc保存。在进入异常时候,硬件将自动更新mepc寄存器的值为当前遇到异常的指令PC值(即当前程序的中止执行点)。该寄存器的值将做为异常的返回地址,在异常结束后,可以使用它保存的pc值返回以前中止执行的程序点。注意:mepc虽然被自动更新,但它是可读可写的,软件能够直接读写该寄存器的值。

对于狭义的中断和狭义的异常而言,RiscV架构定义其返回地址,稍有差别。

出现中断时候,中断返回地址mepc的值被更新为下一条还没有执行的指令。

出现异常时候,中断返回地址mepc的值被更新为当前发生异常的指令pc。注意:若是异常是有ecall和ebreak产生,因为mepc的值被更新为ecall或者ebreak指令本身的PC。所以,在异常返回时候,若是直接使用mepc保存的pc值做为返回地址,则会再次进入异常,造成死循环。正确的作法是在异常处理程序中软件改变mepc指向下一条指令,因为如今ecall/ebreak(c.ebreak)是4字节(2字节)指令,所以更改设定mepc=mepc+4(或+2)便可.

Riscv架构规定,进入异常时候,机器模式异常缘由寄存器mcause被同时更新,以反映当前的异常种类,软件能够经过读此寄存器查询形成异常的具体缘由。

mcause寄存器格式以下,其中最高位为Interrupt位,为1表示是中断,不然为异常,低31位(对于RV32)为异常编号域。

9. mcycle和mcycleh(Machine Cycle)riscv架构定义了一个64位的时钟周期计数器,用于反映处理器成功执行了多少个时钟周期。只要处理器处于执行状态,此计数器便会自增计数,其自增的频率由处理器硬件实现自定义。mcycle寄存器反映了该计数器低32位的值,mcycleh寄存器反映了该计数器高32位的值。

ex模块读(组合逻辑)写(时序逻辑):

判断为scr寄存器操作指令时,对应读写scr寄存器。

clint模块读(组合逻辑)写(时序逻辑)操作:

异常发生时:

clint中断仲裁控制模块

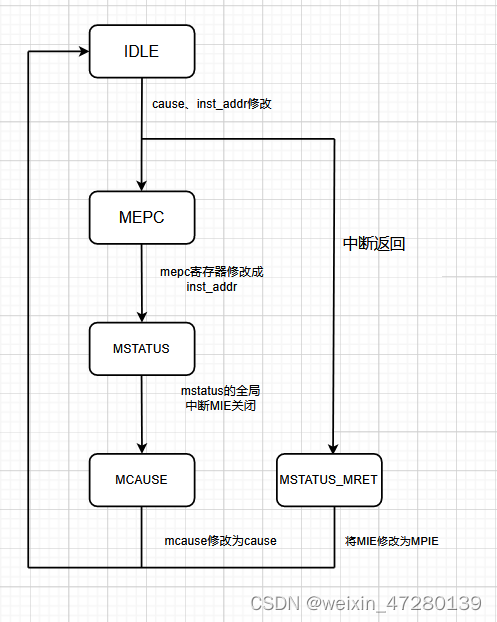

5个写csr寄存器状态定义

S_CSR_IDLE

S_CSR_MSTATUS 写mstatus

S_CSR_MEPC

S_CSR_MSTATUS_MRET 写mstatus(中断返回时修改MIE为MPIE)

S_CSR_MCAUSE

4个写csr寄存器状态定义

S_INT_IDLE

S_INT_MRET 中断返回

S_INT_SYNC_ASSERT 同步中断

S_INT_ASYNC_ASSERT 异步中断

同步中断(异常),异步中断

同步中断:是指由于 CPU 内部事件所引起的中断,如程序出错(非法指令、地址越界)。异常是由于执行了现行指令所引起的。由于系统调用引起的中断属于异常。而中断则是由于系统中某事件引起的,该事件与现行指令无关。

异步中断: 是指由于外部设备事件所引起的中断,如通常的定时器中断等;

整体流程

int_state中断状态 组合逻辑 :

当中断发生时判断是同步异步还是中断返回,修改成对应标志。

csr_state CSR状态控制时序逻辑 :

1.IDLE:在发生同步中断或异步中断时csr_state 由IDLE修改为MEPC同时修改inst_addr(中断返回时的地址)和cause(中断原因),若如果中断标志时中断返回则修改为MSTATUS_MRET

2.MEPC:将mepc寄存器修改为inst_addr,MEPC修改成MSTATUS

3.MSTATUS:MIE全局中断关闭,MSTATUS修改MCAUSE

4.MCAUSE:将mcause寄存器修改为cause,MCAUSE修改成IDLE,发出中断进入信号int_assert_o,中断地址修改为csr_mtvec(新的pc地址),在ex中判断中断发生后将jump_addr_o修改为csr_mtvec(组合逻辑)最终给pc。

5.MSTATUS_MRET:MIE赋值为MPIE,MSTATUS_MRET修改成IDLE, 发出中断进入信号int_assert_o,中断地址修改为csr_mepc(中断返回地址),在ex中判断中断发生后将jump_addr_o修改为csr_mepc(组合逻辑)最终给pc。

243

243

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?