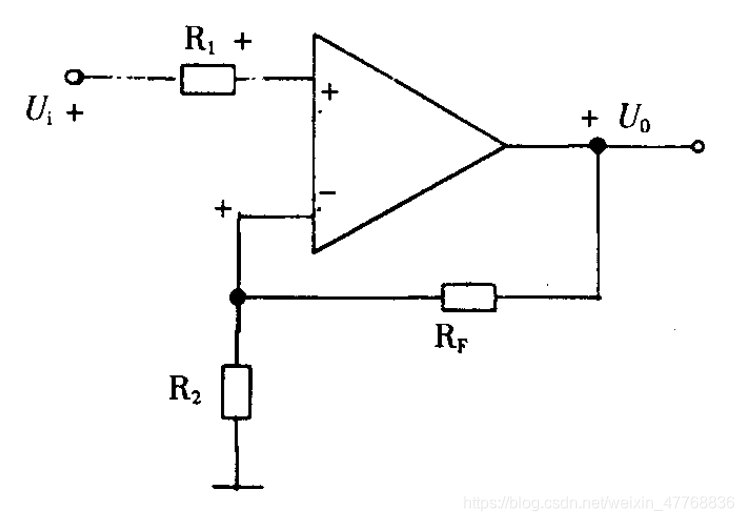

同相放大器电路的定义:信号从运放同相端输入,输出信号的一部分通过反馈电阻接到运放的反相输入端,构成负反馈。同相运放反相端通过电阻接地(或接基准电压,其中基准电压等于电源电压的一半)所构成的电路。

同相放大器电路的特性:

1、输入阻抗很高,为兆欧级。所以对微弱小信号的放大来说,同相放大器电路是不错的选择。

2、输出阻抗极小,为数欧或十几欧姆。有一定的带负载能力。

3、电压放大倍数,同相放大器的电压放大倍数等于反馈电阻阻值除以运放反相端接地(或接基准电压)的电阻阻值再加1。

4、输出信号的相位与输入信号相同。

同相放大器的作用:

1、用于小信号的放大。由于同相放大器具有极大的输入阻抗,因此可以最大程度的再现信号源信号。同时也具有极大的放大倍数。可以对信号进行调节。

2、用作电压跟随器。在同相放大器中,将输出电压全部反馈到反相输入端,就构成了电压跟随器。此时的输出电压与输入电压完全一样。类似于晶体管放大电路中的共集电极放大电路(射极跟随器),但是性能远优于由晶体三极管构成的共集电极放大电路。

3、用作有源滤波器。通过在运放同相端串并接电阻电容或电感,可以构成有源滤波器,从频率复杂的信号中,选择出所需特定频率的信号。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?