Q:本期开始我们分期介绍常用的时序逻辑电路----有限状态机(FSM,Finite State Machine)。

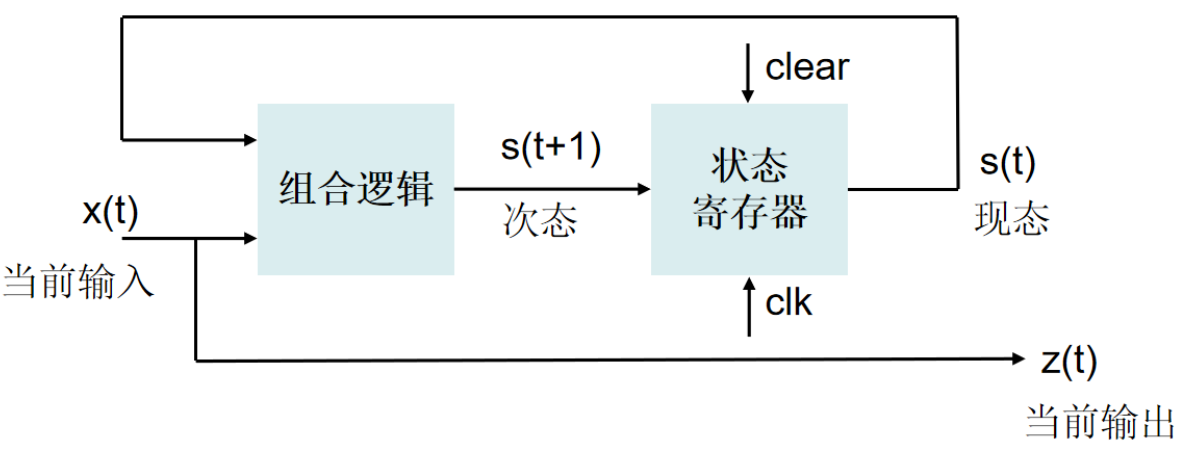

A:前面我们设计实现的触发器、计数器等都可以看作是功能固定的状态机。一个FSM的硬件实现包含一个组合逻辑电路和一个寄存器。FSM的“现态”存储在寄存器中,组合电路利用“当前输入”和储存的“现态”计算出“次态”,也计算出FSM的输出。

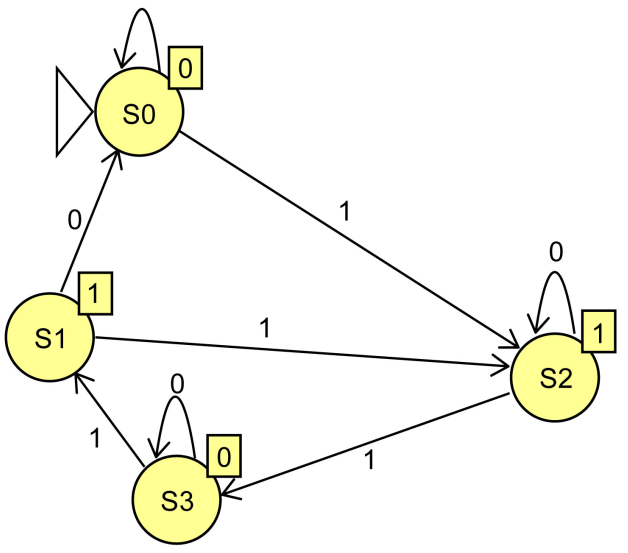

通常使用状态图描述状态机,并根据状态图设计符合要求的电路。状态图由一个向量图表示,顶点(或者节点)代表FSM状态,边缘(或弧线)表示从一种状态到另一种状态的转移。

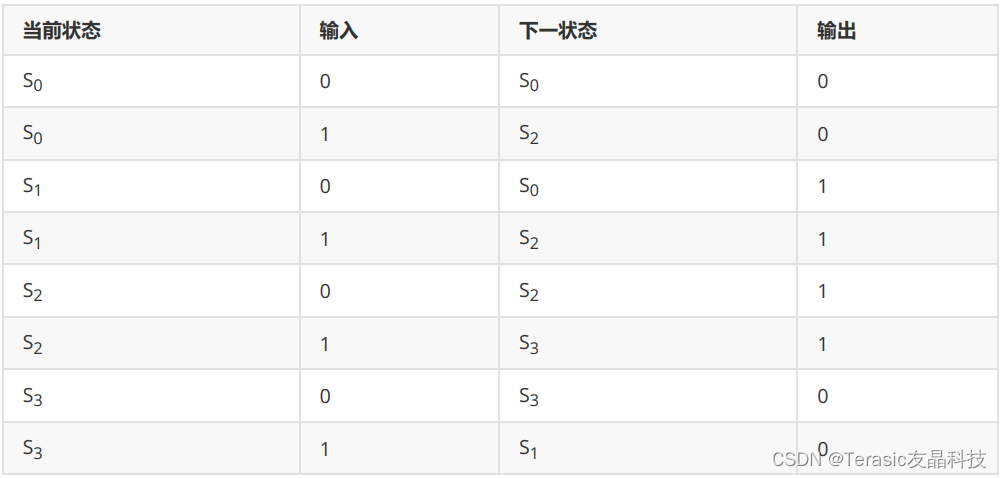

一个FSM也可以通过状态转换表来表示,与以上状态图对应的FSM状态转换表。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?