Q:上一篇我们实现的4线-2线普通编码器在实际应用中会存在一个问题:如果中有2个或2个以上的取值同时为1,输出编码会出现混乱。本篇我们再来学习设计4线-2线优先编码器解决这个问题。

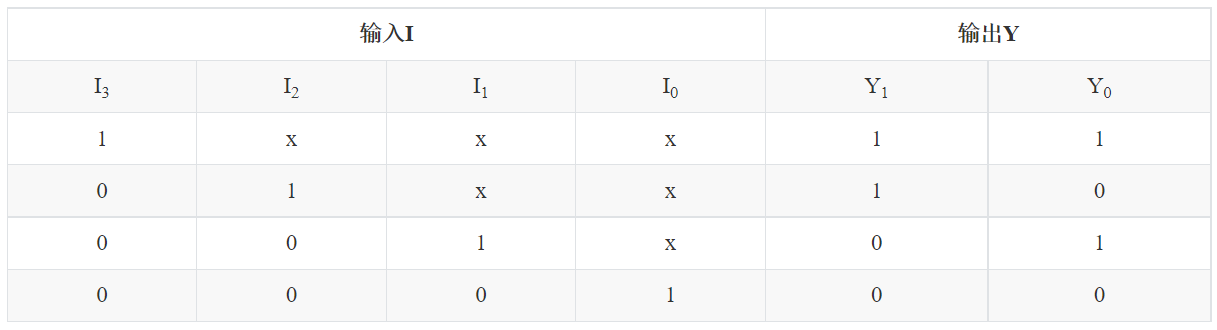

A:基本原理:规定操作先后顺序,即优先级别。4个输入的优先级别的高低次序依次为

、

、

、

。优先编码器允许2个以上的输入同时为1,但只对优先级别高的输入进行编码 。4线-2线优先编码器的真值表:

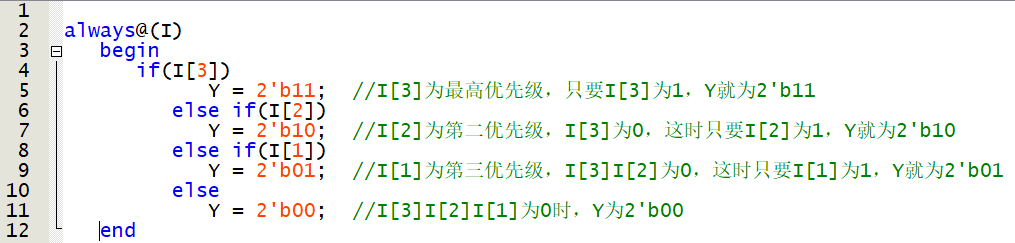

用Verilog过程结构always表示部分代码:

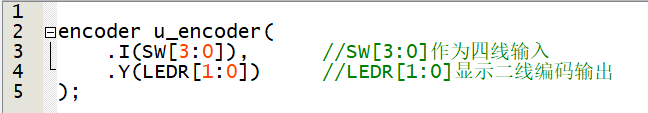

同样使用DE2-115开发板的SW[3:0]作为输入I(),LEDR[1:0]显示Y(

)的输出值,在顶层.v文件中例化4线-2线优先编码器。

643

643

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?