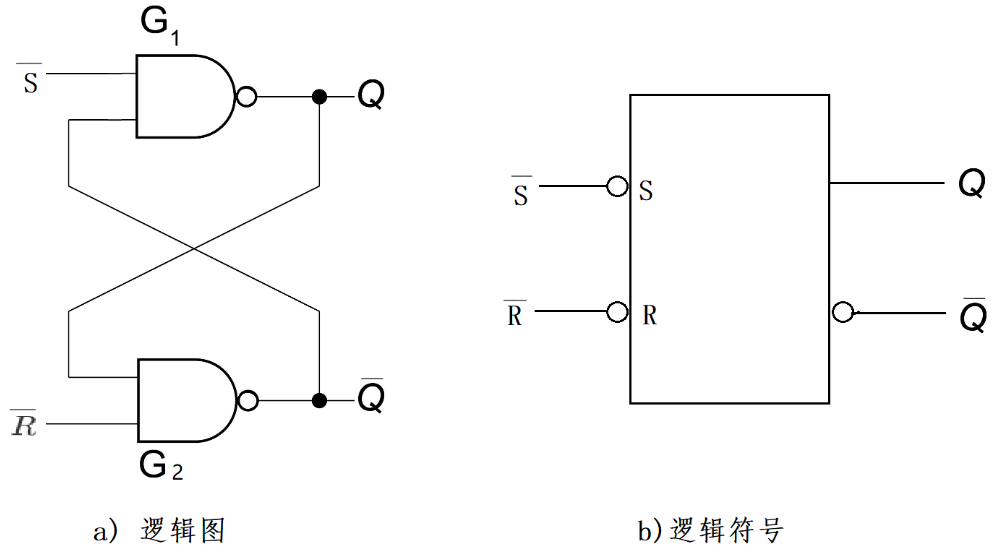

Q:本期开始我们来设计实现时序逻辑电路,首先来设计由与非门构成的基本RS锁存器。

A:基本RS锁存器工作原理:锁存器的2个输入端均为低电平有效,一般情况下,2个输入端均为1时输出状态维持不变,只有需要改变锁存器的状态时才改变:

当,

时,锁存器进入置位状态,即Q=1。 此时,即使输入回到

状态,仍维持Q=1不变;当

,

时,锁存器进入复位状态,即Q=0;当输入回到

状态,仍维持Q=0不变。

当时,将迫使

, 但当输入回到

状态, 则无法确认锁存器回到1状态还是0状态。 在实际应用时,锁存器的

,

应该满足

的约束条件。

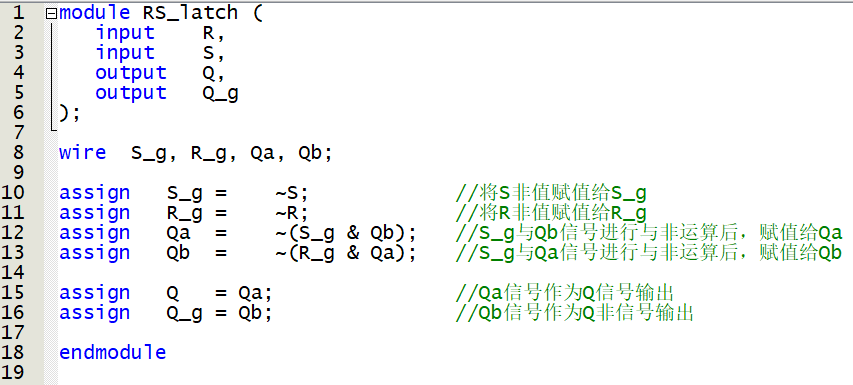

部分Verilog HDL代码:

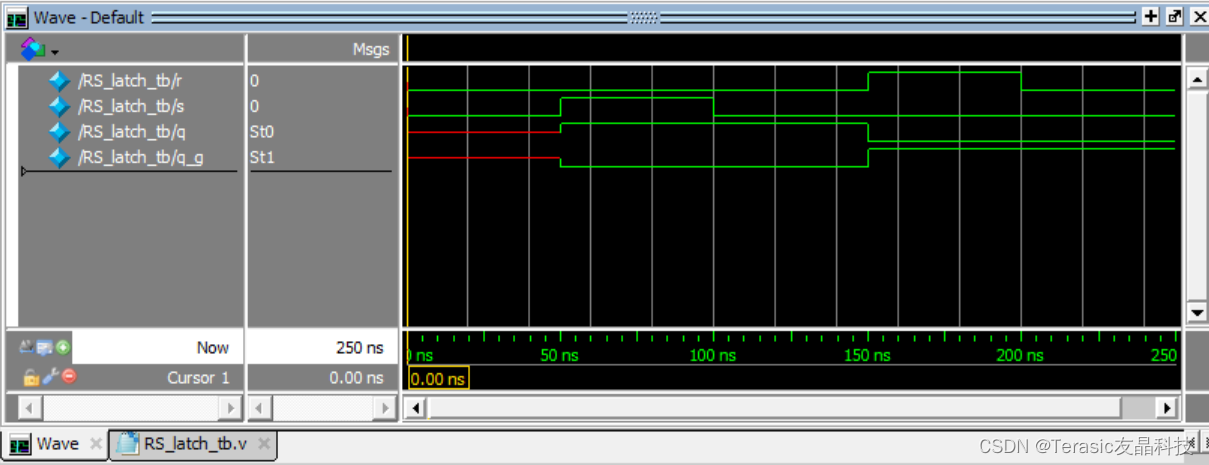

使用DE2-115开发板的SW[1:0]做为2个输入端;LEDR[1:0]显示输出状态。ModelSim仿真结果:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?