一、输入输出串口

包含两个输入信号:系统时钟(sys_clk_100MHz)以及复位信号(sys_rst),一个输出信号:led_out。

二、大致原理

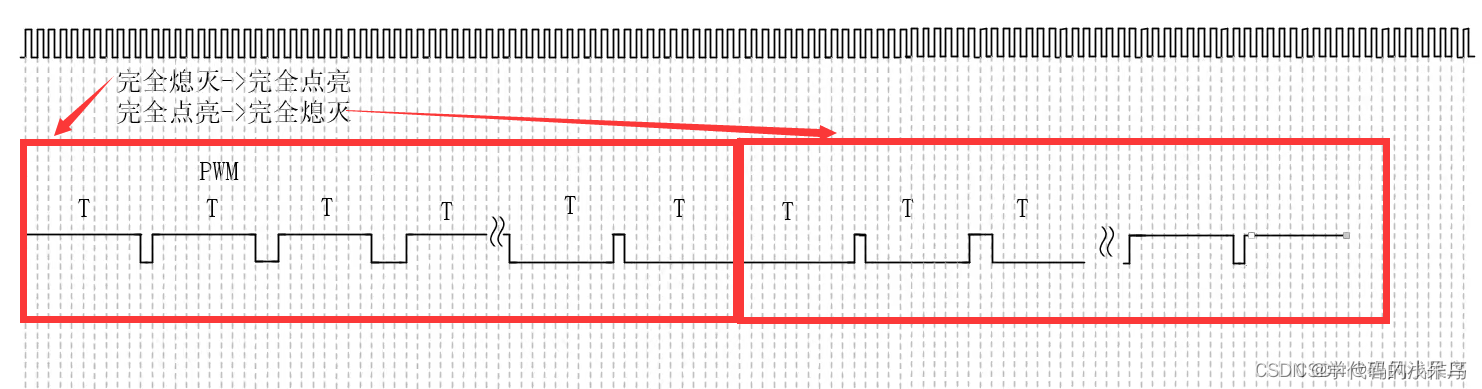

通过PWN来控制呼吸灯的亮、灭程度

前一周期为:完全熄灭 ——> 完全点亮

后一周期为:完全点亮 ——> 完全熄灭

三、代码部分

1、top代码

1-1、设置常量用于计数1us、1ms、1s

parameter CNT_1US = 16'd99,//100MHZ时钟周期的基础上计数满999就是1us

parameter CNT_1MS = 16'd999,//在CNT_1US的基础上计数满999就是1ms

parameter CNT_1S = 16'd999//在CNT_1MS的基础上计数满999就是1s1-2-1、100MHZ时钟周期的基础上计数满999就是1us

always@(posedge sys_clk_100MHz)// 100MHZ时钟周期的基础上计数满999就是1us

if(sys_rst == 1'b1)begin

cnt_1us <= 16'd0;

end

else if(cnt_1us == CNT_1US)begin

cnt_1us <= 16'd0;

end

else begin

cnt_1us <= cnt_1us + 16'd1;

end1-2-2、在CNT_1US的基础上计数满999就是1ms

always@(posedge sys_clk_100MHz)//在CNT_1US的基础上计数满999就是1ms

if(sys_rst == 1'b1)begin

cnt_1ms <= 16'd0;

end

else if((cnt_1ms == CNT_1MS) && (cnt_1us == CNT_1US))begin

cnt_1ms <= 16'd0;

end

else if (cnt_1us == CNT_1US)begin

cnt_1ms <= cnt_1ms + 16'd1;

end

else begin

cnt_1ms <= cnt_1ms;

end1-2-3、在CNT_1MS的基础上计数满999就是1s

always@(posedge sys_clk_100MHz)//在CNT_1MS的基础上计数满999就是1s

if(sys_rst == 1'b1)begin

cnt_1s <= 16'd0;

end

else if((cnt_1s == CNT_1S) &&(cnt_1ms == CNT_1MS) && (cnt_1us == CNT_1US))begin

cnt_1s <= 16'd0;

end

else if ((cnt_1ms == CNT_1MS) && (cnt_1us == CNT_1US))begin

cnt_1s <= cnt_1s + 16'd1;

end

else begin

cnt_1s <= cnt_1s;

end1-2-4、计数达到1s后led状态变化

always@(posedge sys_clk_100MHz)//计数达到1s后led状态变化

if(sys_rst == 1'b1)begin

cnt_en <= 1'b0;

end

else if((cnt_1s == CNT_1S) &&(cnt_1ms == CNT_1MS) && (cnt_1us == CNT_1US))begin

cnt_en <= ~cnt_en;

end

else begin

cnt_en <= cnt_en;

end1-2-5、当cnt_1ms的计数小于等于cnt_1s的计数时led_out处于高电平

always@(posedge sys_clk_100MHz)//当cnt_1ms的计数小于等于cnt_1s的计数时led_out处于高电平

if(sys_rst == 1'b1)begin

led_out <= 1'b1;

end

else if(cnt_1ms <= cnt_1s)begin

led_out <= cnt_en;

end

else begin

led_out <= ~cnt_en;

end1-2、仿真代码

`timescale 1ns / 1ns

module top_tb(

);

reg sys_clk_100MHz;

reg sys_rst;

wire led_out;

top

#(

.CNT_1US(16'd4),

.CNT_1MS(16'd9),

.CNT_1S(16'd9)//为了更加直观的体现出来呼吸灯的效果

)

u0

(

.sys_clk_100MHz(sys_clk_100MHz),

.sys_rst(sys_rst),

.led_out(led_out)

);

initial begin

sys_clk_100MHz = 1'b0;

sys_rst = 1'b1;

#20 sys_rst = 1'b0;

end

always #5 sys_clk_100MHz = ~sys_clk_100MHz;

endmodule

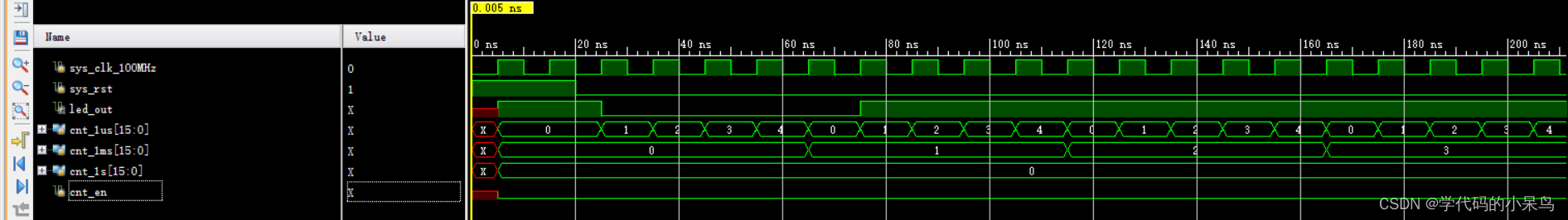

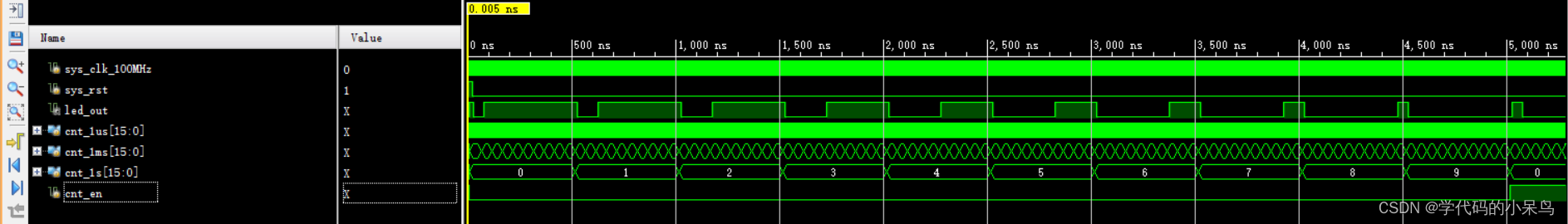

1-3、仿真结果

156

156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?