问题

对一个32bit数,捕捉输入信号每一位的下降沿。“捕捉”是指在同步复位信号到来之前,该位将保持高电平。

因此,输出信号每一位的表现与SR锁存器类似,若复位和下降沿到来两个事件同时发生,则复位有优先级。

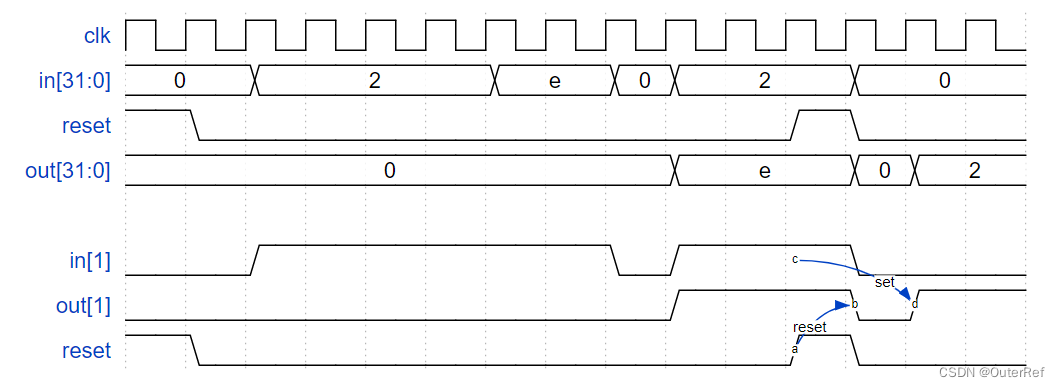

下图是一个例子:

模块声明

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

解题思路

- 要记忆上次clk上升沿的结果,可用移位寄存器。

- 注意同步复位信号

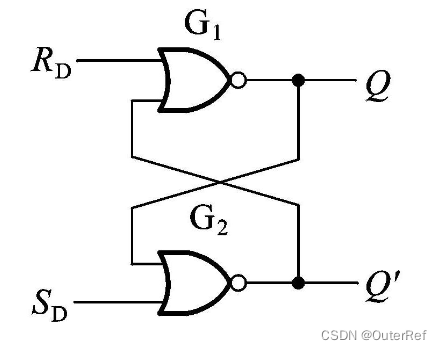

- 捕捉(capture)的行为和SR锁存器类似,如下图。只需将同步的reset作为R,输入下降沿到来的信号作为S,输出即为Q(不需要用到Q’,不用担心不稳定状态对Q和Q’对称性的破坏)。

代码

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] q, last_in;

reg reset_q;

wire [31:0] o1, o2, nedge;

always @(posedge clk) begin

reset_q <= reset;

q <= in;

last_in <= q;

end

// NOR SR latch

assign nedge = ~q & last_in;

assign o1 = ~(nedge|o2);

assign o2 = ~({32{reset_q}}|o1); // Note that reset is a 1 bit signal

assign out = o2;

endmodule

补充

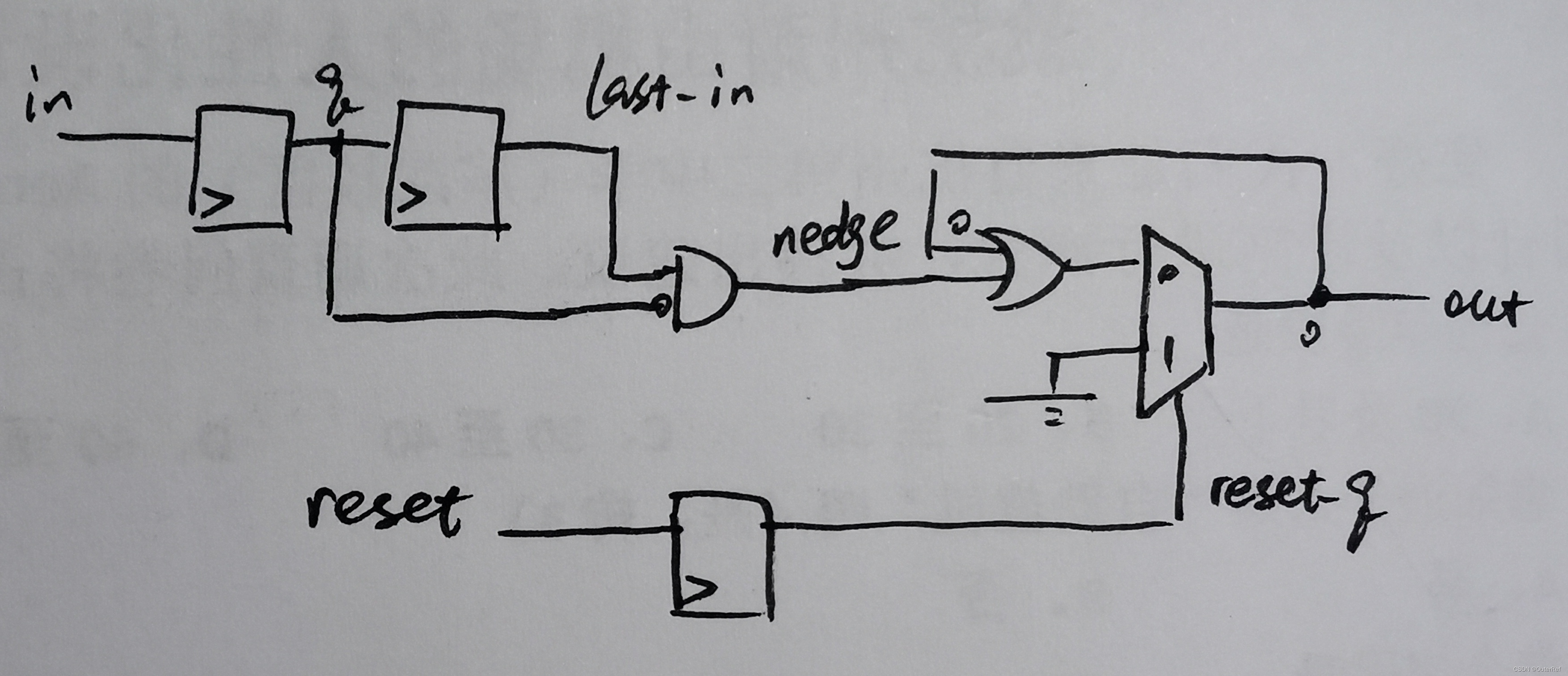

一开始没注意到题目中对SR锁存器的提示,构想的电路如下图,也是可以通过的。

2184

2184

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?