目录

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现

1. 前言

在之前的博客当中,已经实现了802.11a当中数据域的一系列处理,最终得到了数据域的时域波形。相较于数据域,signal域的处理很类似并且更简单。

2.硬件实现

·signal域的数据不需要进行加扰和删余操作,因此实现起来比较简单。

·signal域的数据不需要进行二级交织,只需一级交织。

·signal域的数据采用的是BPSK的调制方式,占据一个OFDM符号。

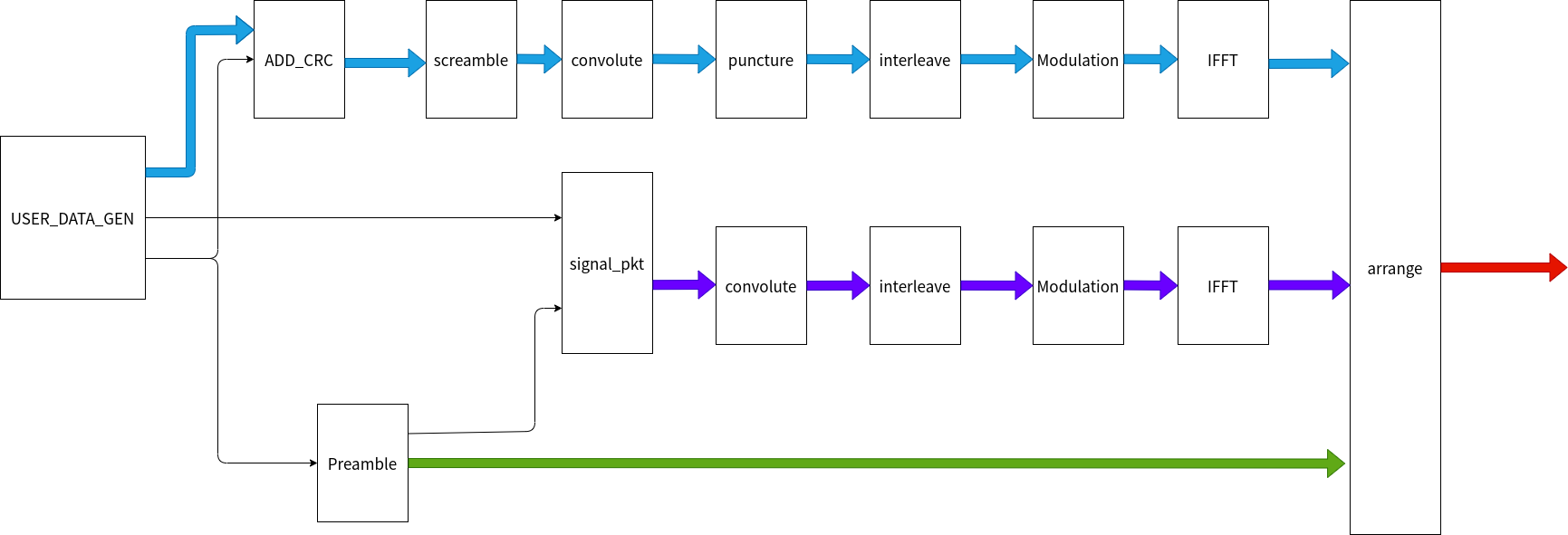

下图的紫色部分,显示了signal域数据的处理过程。

OFDM发射模块

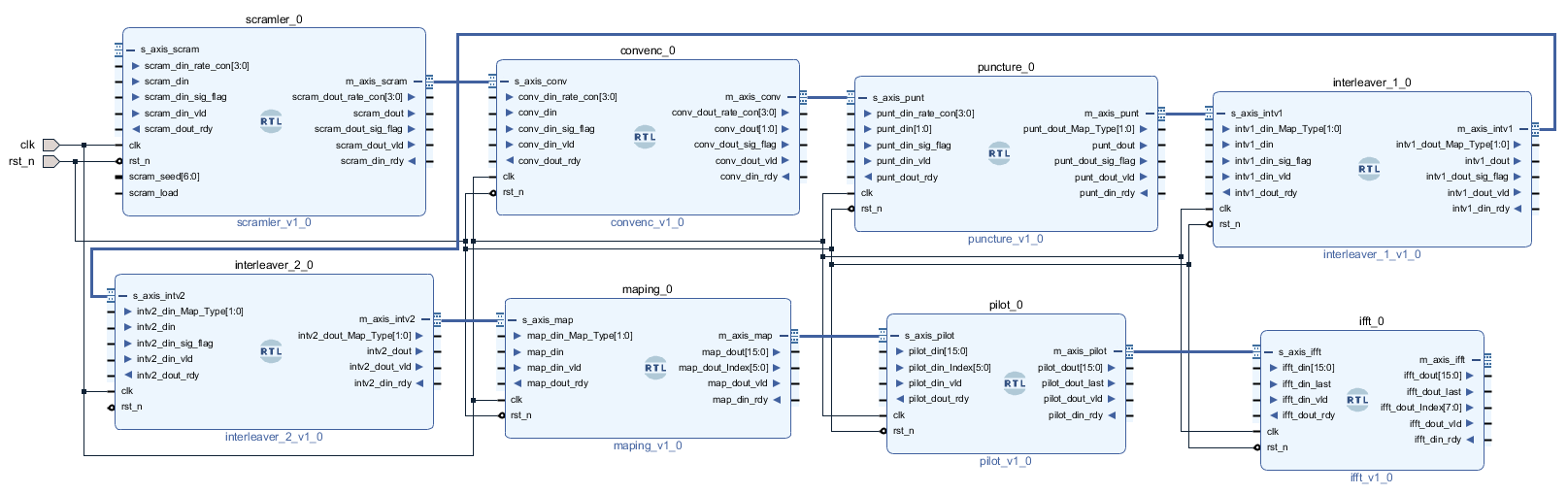

signal域数首先会根据格式产生一帧数据,然后这个数据再依次经过1/2卷积编码,一级交织,BPSK调制,IFFT转换以及添加循环前缀之后,最终得到signal域的时域波形。和data域的区别是不进行扰码,删余和二级交织,所示设计上,在data域处理流程中添加Signal_Flag为Signal符号标志信号,屏蔽这些模块即可实现signal域数剧处理。如下图所示:

添加Signal_Flag后的打他域处理电路图

3.verilog代码

以扰码模块为例进行,添加Signal_Flag为Signal符号标志信号,如下所示:

`timescale 1ns / 1ps

///

//扰码多项式 s(x) = x^7 + x^4 + 1

///

module scramler(

input clk ,

input rst_n ,

input [6:0] scram_seed , //扰码器初始状态

input scram_load ,

input scram_din ,

input scram_din_vld ,

input scram_din_rdy ,

input scram_din_sig_flag ,

input [3:0] scram_din_rate_con ,

output reg scram_dout ,

output reg scram_dout_vld ,

output scram_dout_rdy ,

output reg scram_dout_sig_flag ,

output reg [3:0] scram_dout_rate_con

);

reg [6:0] shift_reg ;

wire scram_en ;

assign scram_dout_rdy = scram_din_rdy ;

assign scram_en = scram_dout_rdy & scram_din_vld ;

always@(posedge clk or negedge rst_n ) begin

if(!rst_n) begin

shift_reg <= 0;

scram_dout <= 0;

scram_dout_vld <= 0;

scram_dout_sig_flag <= 0;

scram_dout_rate_con <= 4'b1011;

end

else if( scram_load ) begin

shift_reg <= scram_seed;

scram_dout_vld <= 0;

end

else if( scram_en) begin

if(~scram_din_sig_flag)begin

scram_dout <= shift_reg[6] + shift_reg[3] + scram_din; //s(x) = x^7 + x^4 + 1

scram_dout_vld <= 1;

shift_reg <= {shift_reg[5:0],(shift_reg[6]+shift_reg[3])};

end

else begin

scram_dout <= scram_din;

scram_dout_vld <= 1;

end

scram_dout_sig_flag <= scram_din_sig_flag;

scram_dout_rate_con <= scram_din_rate_con;

end

else if(scram_dout_vld & scram_din_rdy)begin //下游接受完毕,没有新数据进来,vld拉低

scram_dout_vld <= 0;

end

end

endmodule

在scram_din_sig_flag = 1时,不启动扰码模块直接将输入进行输出。同时还添加了scram_din_rate_con信号,用于接收调制方式和数据速率。

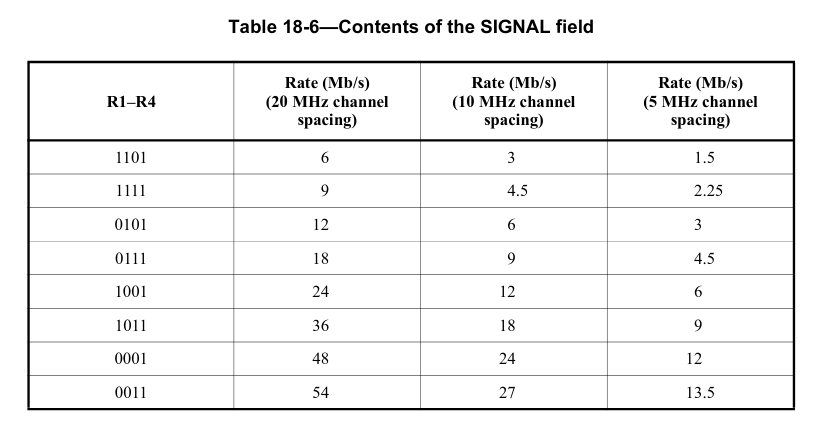

这里只展示了扰码模块的修改,其他模块修改也是一样的。Signal域中的信息比特的处理过程与Data域相同,只是标准规定其只能采用BPSK调制而不能用更加复杂的调制方式,编码方式为1/2码率的卷积编码,不再进行删余操作,以尽可能保证可靠传输。这样Signal域就可以得到6Mb/s的信息传输速率,这是IEEE802.11a中所规定的最低速率,同时也是最为可靠的传输方式,以确保Signal域信息的正确接收。

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现

1243

1243

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?