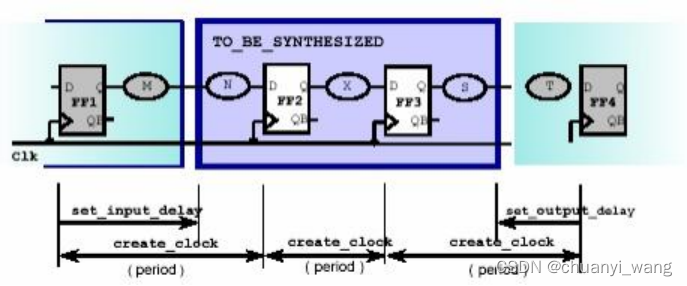

在上一节 时序和面积一节钟,我们讨论了一些简单的时序约束,如定义时钟,设置模块 的输入输出延时等等(如上图),但是这些时序约束都是简单的约束,离较大规模芯片的实 际工作条件还有一定的差距,比如时钟信号只有一个,并且周期严格遵守给定的值。在这一节里,我们着重讨论时钟约束的下面几个问题——

- 非理想的单时钟网络

- 同步多时钟网络

- 异步多时钟网络

- 多周期路径

6.1 非理想的单时钟系统

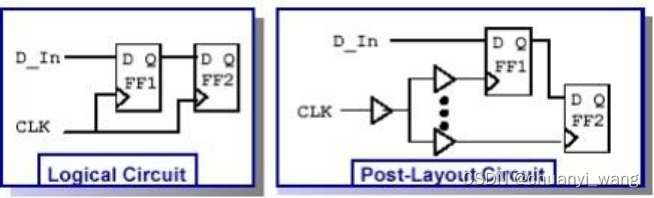

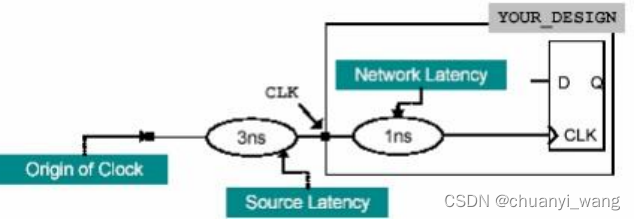

前面提到过,在定义时钟之后,都要给该时钟设置一个 dont_touch ,这是告诉 DC 不要 给时钟网络作综合,因为综合时钟网络需要考虑单元的实际物理位置,这是前端的逻辑综合目 前不能完成的工作。如上图所示,实际的时钟网络也称为时钟树,它在时钟的各条路径上产 生大小不一的 buffer , 目的是为了保证时钟到达每个触发器的延时尽量相等。

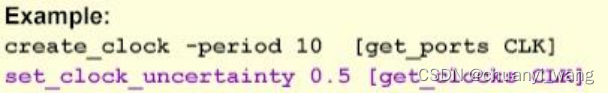

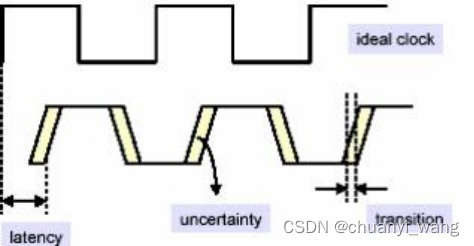

虽然 DC 无法最终综合时钟树,但是我们可以加入一些约束让此时的时钟更加接近实际 的工作情况。例如 实际的时钟达到各个触发器的时间不是一样的,它们之间有一个偏差, 称为时钟偏差(Clock Skew) ,为了反映这个偏差,我们在综合的时候可以用一个命令来模拟它,即 set_clock_uncertainty ,下面是一个例子——

假设时钟周期是 10ns ,FF2 的建立时间为 0.2ns ,预先估计时钟偏差为 0.5ns ,从 FF1 触 发的数据必须在一个周期之内到达 FF2 ,当引入时钟偏差以后,所谓的一个周期就不再是 10ns ,而可能最短为 10-0.5=9.5ns ,再减去 0.2 的建立时间,实际留给 X 路径的延时最大只 能有 9.3ns

。

除了时钟偏差(Clock Skew)之外,还有两个命令值得注意,这就是 set_clock_latency ,和 set_propagated_clock ,如下图所示——

一般而言 , 时钟都是由一个专门的模块(Clock_gen) 来生成的 ,这 里称为时钟源(ClockSource) ,时钟产生之后,必定要经过一段网络延时才能到达被综合的模块,这段延时称为 时钟源延时(Source Latency) ,到达模块的端口后,要到达内部的触发器,也要经过一定的延 时,这个延时称为网络延时(Network Latency) 。这 别通过set_clock_latency –source 和set_clock_latency 来描述。另外,set_propagated_clock 主要用在布局之后(post-layout)的综合 上,意思是说,此时的网络延时已经可以由时钟树上的 buffer 确切的推断出来。

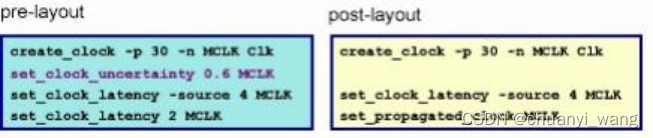

布局之前和布局之后描述时钟的命令对比如下图——

在布局前正因为没有 buffer ,才需要用网络延时和时钟偏移来模拟布局后的情况。

6. 2同步多时钟网络

上图是一个同步多时钟网络,中间的模块是我们要综合的模块,内部只有一个 CLKC, 但是输入和输出都是由不同周期的时钟控制的,也就是说,它们属于不同的路径组(Path Group) ,但是这些时钟 CLKA-CLKE 都是从一个时钟分频得到的,因此称为同步多时钟。

观察被综合模块的输入端口,它同时受两个时钟的约束,由于它们周期不同,所以 CLKA 触发的信号到达 FF2 的时间也不是固定的。

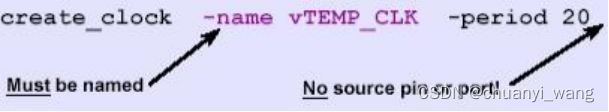

对于这样的时钟网络,我们需要用到虚拟时钟的概念(Virtual Clock) 。对上图要综合的 模块而言,除了 CLKC 之外的其他时钟都可以称为虚拟时钟,它们有如下要求——

- 在顶层模块之内的其他模块内定义的时钟

- 在当前的被综合模块(current_design)内不包含虚拟时钟驱动的触发器

- 作为当前模块的输入输出延时参考

定义虚拟时钟和定义时钟的命令差不多,只是不要指定虚拟时钟的端口或者管脚,另外 必须指定时钟的名字——

如上述语句指定了一个周期为 20ns 的虚拟时钟 vTEMP_CLK。

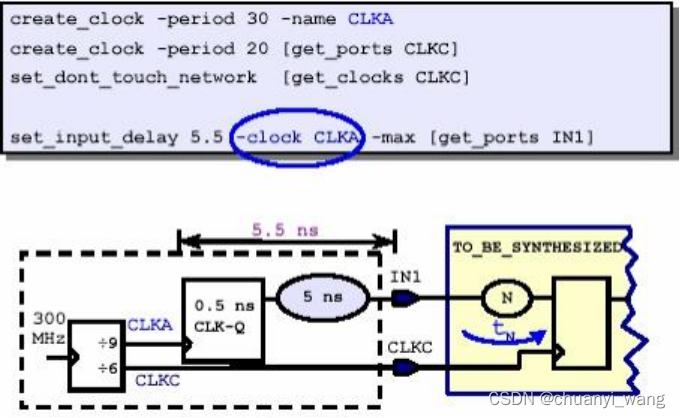

定义了虚拟时钟之后 , 我们就可以描述图 86 的 电路 时序 了 , 先设定输入延 时 (set_input_delay) ,从图中看出,CLKA 和CLKC 的周期分别为 30ns 和 20ns ,假设 IN1 端口 的输入延时为 5.5ns ,可以设定如下——

值得注意的就是先定义虚拟时钟 CLKA ,然后在 set_input_delay 的驱动时钟开关中选择 CLKA 。在设定完输入延时之后,Design Compler 就会在 CLKA 和 CLKC 的所有情况中找到 其中最短的周期,作为对这段路径的约束——

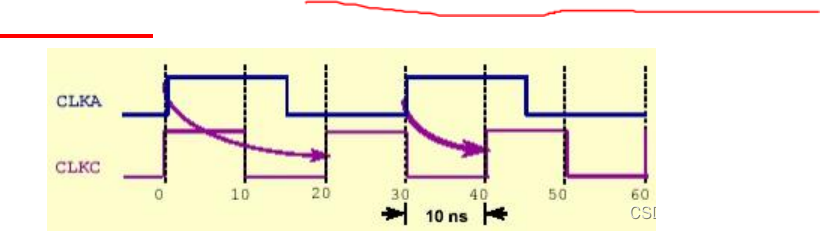

寻找最小周期的过程如下:先计算 CLKA 和 CLKC 的最小公约数(30 和 20 的公约数) 为 60ns ,即两个 CLKA 的周期,然后分别以这两个上升沿为触发沿,计算此时的最短捕捉(被 CLKC 接收)的时间,最后对比这两个时间,取其中最小的一个。如下图计算出的最短捕捉 时间为 10ns ,因此留下给路径 N 的延时为——

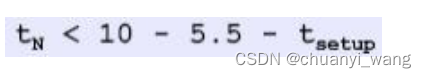

按照上面同样的方法,我们也可以得出图 86 的输出延时(set_output_delay) ,如下图所示

值得注意的是:这里的输出同时驱动两个虚拟时钟电路 CLKD 和 CLKE ,因此描述第 二个延时的时候需要加入-add_delay 的开关,否则将覆盖前一条路径的约束。

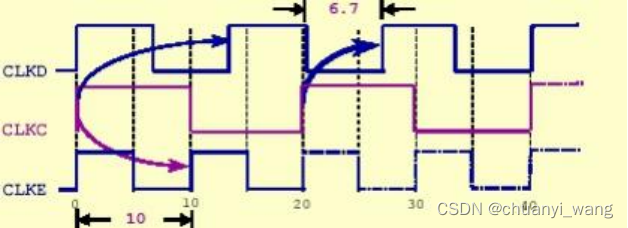

这里的各时钟波形关系如下所示——

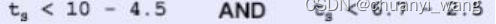

可见,CLKC 到 CLKD 的最小捕捉时间为 6.7ns ,到 CLKE 的最小捕捉周期为 10ns 。因 此输出最小周期为 6.7ns 和 10ns ,对应的输出电路的延时必须满足下面的条件

从前面的推导过程可以看出,DC 是在各个相关时钟周期的最小公约数的基础上计算最 小输入/输出时间的,因此我们在定义时钟的时候尽量选用整数,不要加上小数点(比如 20ns 和 30. 1ns) ,避免不必要的麻烦。

6. 3 异步多时钟网络

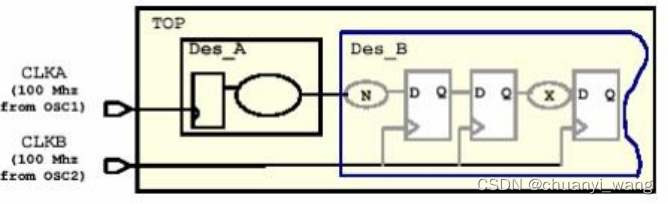

异步多时钟网络和同步多时钟网络的结构类似,只是它的各个时钟 CLKA-CLKE 不是 从同一个时钟源中分频产生的,而可能是不同的两个晶振,如下图所示——

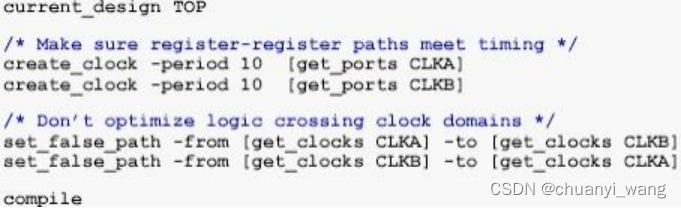

由于是不同的晶振产生的时钟,它们之间的就不存在最小公约数的关系,但是在默认情 况下,DC 并不知道,它会认为它们是同步的时钟网络而尽量去找两个时钟之间的最小捕捉 时间,不但浪费了时间而且会产生出不符合要求的电路。在这种情况下,我们需要告诉 DC 不要管两个时钟之间路径的时序,这里需要用到一个命令——set_false_path。

False Path (伪路径)是指电路中的一些不需要考虑时序约束的路径,它一般出现在异 步逻辑之中。上面的例子设置伪路径的语句如下——

这样,所有的从 CLKA 到 CLKB 和 CLKB 到 CLKA 的路径都被认为是伪路径。

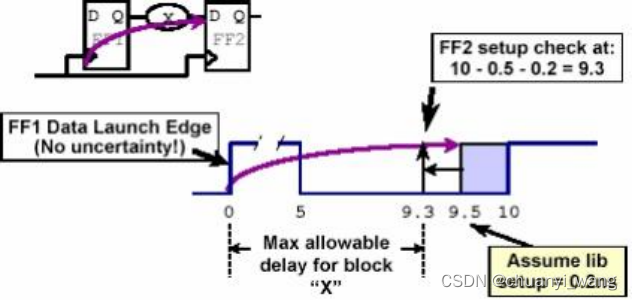

6.4 多周期路径

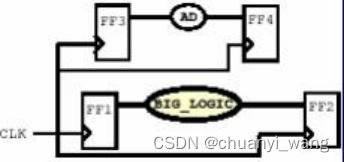

在前面的讨论中,我们默认所有组合路径的延时都是一个周期 ,然而实际电路中也可能存在超过一个周期的路径,如下图所示——

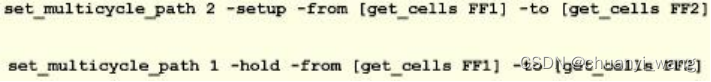

在 FF1 和 FF2 之前,存在一个BIG_LOGIC ,假设我们允许它的延时在两个周期之内, 那么因该怎样把这个信息告诉 Design Compiler 呢?这里就需要用到 DC 的一个设置多周期 路径的命令——set_multicycle_path

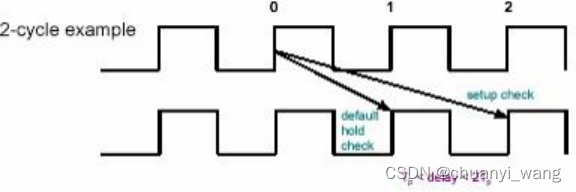

第一个语句说明建立时间是在 FF1 触发后的第二个周期后检查,第二个语句说明保持 时间在 FF1 触发后的第一个周期检查。可得此时的波形图如下——

352

352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?