预备知识

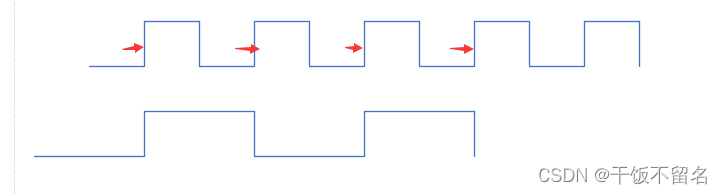

(1 计数器分频

reg类型理解为D触发器,使用D触发器让电平改变实现二分频率。

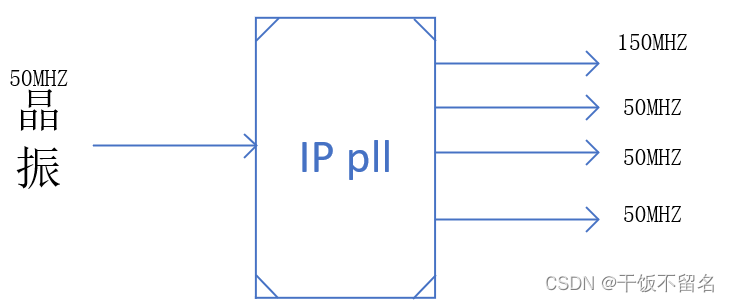

(2 PLL理解

FPGA自身没时钟,靠外部的时钟。pll就是可以把时钟进行分频并且可以有多个输出。

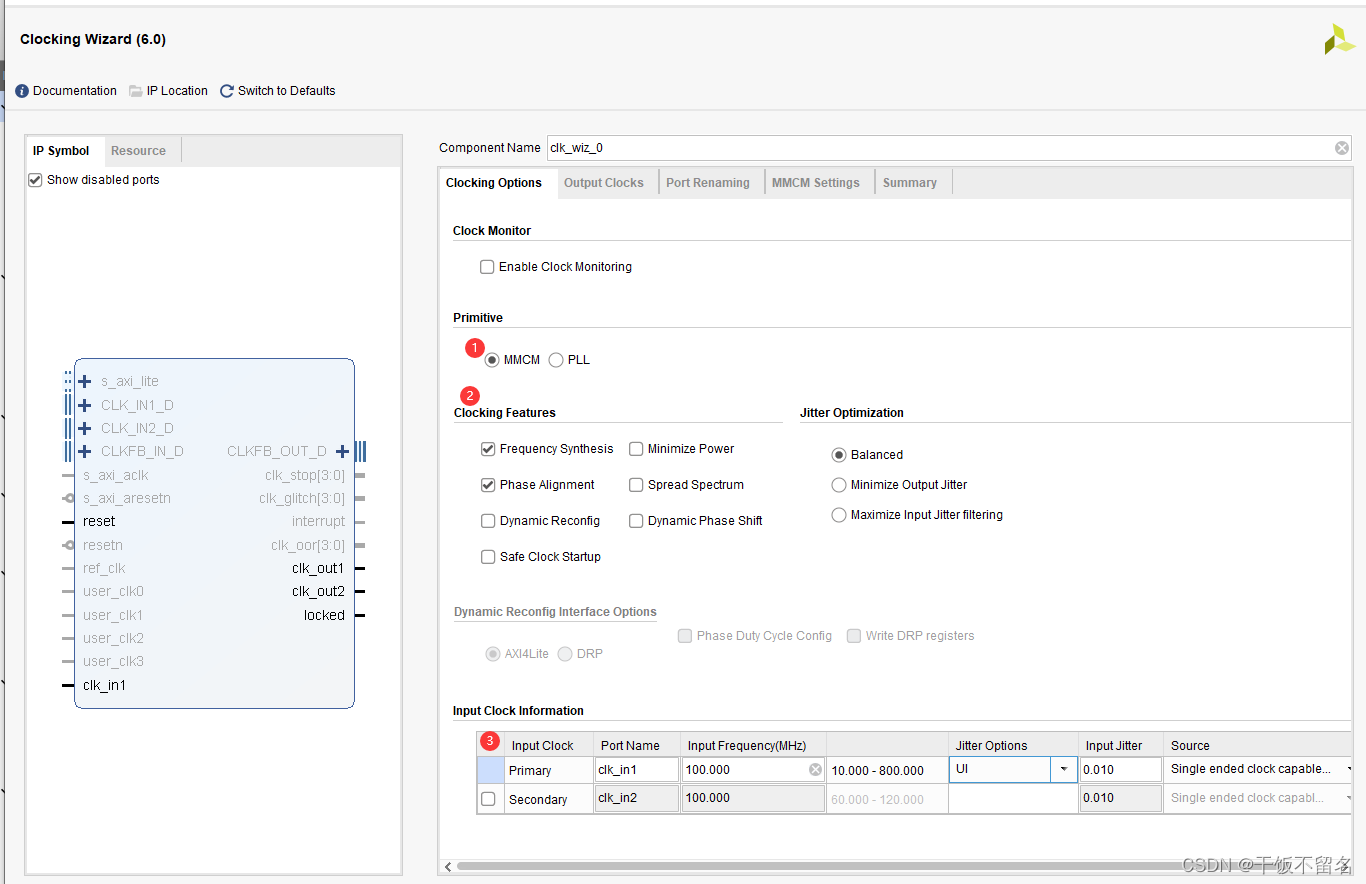

(3 PLL详细说明

这里①MMCM 和PLL 没啥区别功能都一样。MMCM比较先进

②默认

③看自己板卡的时钟是多少写多少

①选择输入的时钟第一个100,后续跟的100是实际的输出,有一定的范围

后续的50 50理解为高电平多久 低电平多久 一般都55开

②复位必须关闭,第一种直接这里关闭,第二种给他赋值,Active High 直接赋值0让它失效

(4 细节

①程序编写不用除法就不用除法 >>右移(除法),<<(左移)乘法。

②~取反符号00 11,!是逻辑运算输出1 0,不用这个控制多个信号

③led分高低电平点亮

设计思想

(1 使得晶振的频率降低,板卡提供的是50MHZ,通过pll降低到5MHZ,因为pll输出范围有限。再写一个降低频率的程序,降低为1MHZ。采用从低向上的设计思想。

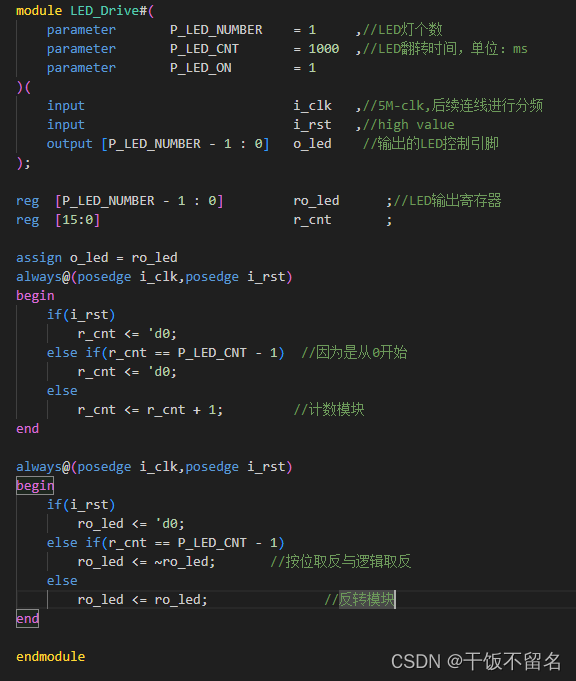

①

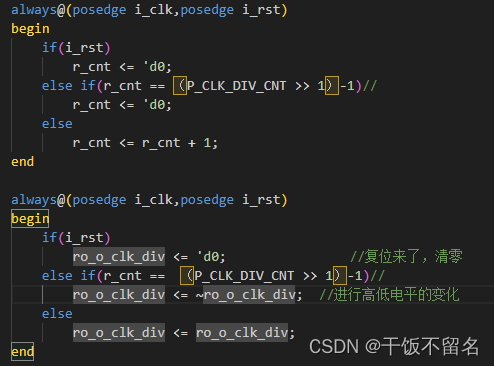

计数器原理,计数到预定的值清零,同时使得led进行反转。这里采用parameter是为了模板反复用。

②

P_CLK_DIV_CNT :定义为进行几次分频

分频可以理解为led的灭 明 这里是高低电平的反转都一样的道理。

复位来了就清零。计数到了清零同时进行反转。其他情况保持不变。

先写时钟再写高低电平的变化。这里可以理解为固定的格式方便以后套用。

2181

2181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?