*此文章主要讲述guardring(保护环)工作机制,以及如何实现对latch up(闩锁效应)的正确防护。

1

. MOS管的寄生

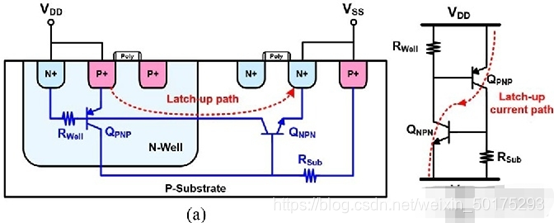

首先我们应该了解到,在NMOS与PMOS器件中,NMOS管的P-sub,N+以及Nwell可以寄生出一个横向的npn管,同理PMOS管的Nwell,P+以及P-sub可以寄生出一个纵向的pnp管,NMOS中的N+作为npn的发射极,PMOS中的P+作为pnp的发射极。当P-sub中的N+注入电子时,电子会经过P-sub(电子在P-sub中为少数载流子)的扩散到达P-sub与Nwell的交界处,在外部电压的作用下流向Nwell,最终流向Nwell中的P+,导致寄生成pnpn的结构。

如下图:

这里是引用

2. PNPN导通

在QPNP与QNPN的基区分别与VDD,VSS存在一个非零的电阻,Rwell与Rsub,这样我们可以发现纵向QPNP的增益在几百倍,而横向QNPN的增益在几十倍。当无外界干扰时,寄生的三极管都处于截至状态,不会有latch up产生。

但是当电路经历一下变化时,寄生QNPN的基极有电流注入,就会引起连锁反应,两个三极管会导通形成一同由VDD到VSS的低阻通路,在VDD抽取很大的电流。

Latch up产生原因

- 当I/O信号发生变化时,变化的范围超过VDD,VSS的范围,此时由大电流产生时。

- 当电路刚刚工作时,Nwell与P-sub寄生电容产生足够大的电流。

- 发生ESD时,可能会在保护电路中引入一部分电流到Nwell与P-sub中。

- 在Power附近,当负载过大时,power的突然变化

消除Latch up的几种方法

:

- 使用guardring,N+ring围绕pmos接VDD,P+ring围绕nmos接VSS,必要的地方加两层guardring。

- 衬底接触孔以及n阱接触孔间隔都应与Source比较小,使其接触电阻最小,减小Rwell以及Rsub的寄生。

- 版图布局时,nmos尽量靠近GND,pmos尽量靠近VDD。

- 选择合适的掺杂浓度和分布以及版图的设计规则,确保寄生电阻和三极管的电流都很小。

我们着重了解一下guardring放置。

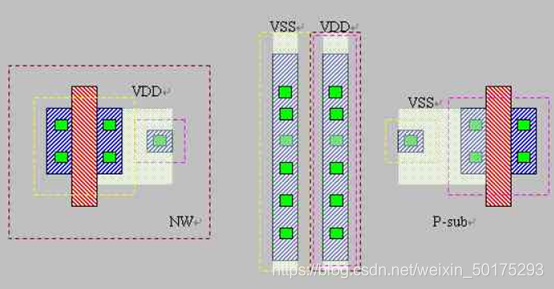

如下图,是典型的防止guarding的版图结构:

左边是Nwell,pmos和N+ well contact。右边是P-sub,nmos和P+ sub contact。中间就是防止的guardring

如上面讲到,例如N+中的电子经过P-sub的扩散会到达P-sub与Nwell的交界处,最终到达Nwell中的P+才会形成闩锁效应,如果我们能在电子进入Nwell之前收集起来,并泄放掉就不会引起Latch up,即在nmos周围加P+ring并电源。Nwell中P+中的空穴同样此类方法,在pmos周围加N+ringj接地收集空穴。

而保护环主要分为多数载流子保护环和少数载流子保护环(多数与少数是相对而言的)

上面说的P+ring与N+ring其实都是少数载流子保护环,不知道都没有注意到,其实Nwell contact与sub contact能够起到多数载流子保护环的作用。

4215

4215

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?