📢:如果你也对机器人、人工智能感兴趣,看来我们志同道合✨

📢:不妨浏览一下我的博客主页【https://blog.csdn.net/weixin_51244852】

📢:文章若有幸对你有帮助,可点赞 👍 收藏 ⭐不迷路🙉

📢:内容若有错误,敬请留言 📝指正!原创文,转载请注明出处

文章目录

一、前言

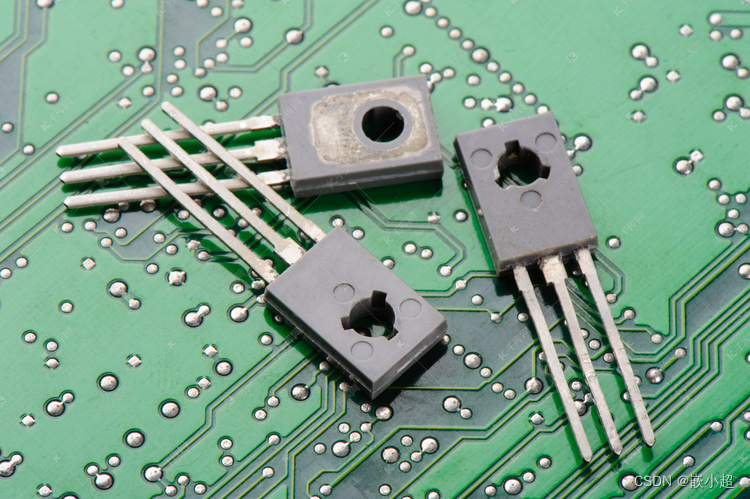

1.1 晶体管的诞生

晶体管的发明是由三位科学家共同完成的,他们是美国贝尔实验室的威廉·肖克利(William Shockley)、约翰·巴丁(John Bardeen)和沃尔特·布拉顿(Walter Brattain)。

他们于1947年在贝尔实验室首次成功制造出了工作的晶体管原型。

1.2 为什么要发明晶体管

取代早期电子管:在晶体管出现之前,电子设备中主要使用的是体积庞大、功耗高的电子管(例如三极管、真空管),它们需要较高的电压和功率来工作,同时也很容易损坏。晶体管的出现使得电子设备变得更小巧、便携,同时功耗更低。

总体来说,晶体管的发明改变了电子设备的面貌,从而推动了电子技术的快速发展。它取代了体积庞大的电子管,提供了更小巧、高效、稳定的电子组件,为计算机、通信、无线技术等领域的进步奠定了基础。

1.3 晶体管为什么又叫MOS管

晶体管之所以被称为MOS管,是因为其中的场效应晶体管(Field-Effect Transistor,FET)使用了金属-氧化物-半导体(Metal-Oxide-Semiconductor,MOS)结构。

MOS结构是一种用于制造场效应晶体管的技术。它包括一个绝缘层(氧化物)和一个金属导体电极,覆盖在半导体材料上。绝缘层通常是二氧化硅(SiO2)或高介电常数的材料。金属导体通常是铝(Al)或铜(Cu)。

在MOS结构中,半导体材料被分成了两个区域:沟道(Channel)和掺杂的源极(Source)与漏极(Drain)区域。沟道位于绝缘层下方,可以由P型或N型半导体材料构成。

当在沟道下面的绝缘层上加上一个电压时,绝缘层中的电场会影响沟道中的电荷分布。这种电场控制电流流动的特性使得MOS结构中的场效应晶体管能够实现电流的调节和放大。

由于MOS结构的重要性和普遍性,包括金属-氧化物-半导体结构的场效应晶体管在称呼上被简称为MOS管。它是一种关键的半导体器件,在现代集成电路中广泛应用,驱动了数字电子技术的快速发展。

二、专业概念

✍量子力学隧道效应

隧道效应指的是量子力学中的一种现象,当粒子穿过势垒时,即使其能量低于势垒高度,仍有一定的概率穿越势垒。

经典物理学认为,粒子在没有足够能量时是无法克服势垒的,而只有当粒子的能量高于势垒的高度时,才能通过势垒。然而,量子力学的隧道效应表明,即使粒子的能量低于势垒的高度,仍然存在一定的概率穿过势垒。

在闪存存储器中,量子力学隧道效应被用于通过隧道氧化物层实现浮栅电荷的存储和擦除。通过控制电场和隧道电流,可以对浮栅中的电荷进行精确的读取和写入,实现非易失性的数据存储。

✍沟道channel

在半导体器件中,沟道(Channel)指的是晶体管中连接源极和漏极的区域,用于控制电流流动的通道。主要有两种类型的沟道:N沟道和P沟道,分别用于N型和P型MOS晶体管。

在MOS(Metal-Oxide-Semiconductor)结构的晶体管中,沟道是位于绝缘层(通常是二氧化硅)之下的半导体层,被控制电压作用下形成导电通道。晶体管通常有源极、漏极和栅极三个电极。

对于N沟道MOS(NMOS)晶体管,沟道是由N型半导体(通常是硅)组成的。当栅极电压高于阈值电压时,沟道形成连通源极和漏极的导电通道,允许电子在沟道中自由流动。

对于P沟道MOS(PMOS)晶体管,沟道是由P型半导体组成的。当栅极电压低于阈值电压时,沟道形成连通源极和漏极的导电通道,允许空穴在沟道中自由流动。

通过对栅极电压的控制,可以控制沟道的导电性质,从而控制源极和漏极之间的电流流动。通过改变栅极电压,可以改变沟道的导电性和电流的大小。这使得晶体管能够执行开关和放大功能,是现代集成电路中非常重要的元件。

总结起来,沟道是晶体管中连接源极和漏极的区域,用于控制电流流动的通道。根据晶体管类型,可以有N沟道和P沟道,分别用于N型和P型MOS晶体管。通过对栅极电压的控制,可以控制晶体管的导电性质和电流流动。这是集成电路中重要的开关和放大元件。

✍阈值电压

阈值电压是MOS管关断的最低电压值,随着时间的推移,此电压值会产生偏移,需要进行调整。

MOS管的阈值电压等于背栅(backgate)和源极(source)接在一起时形成沟道(channel)需要的栅极(gate)对source偏置电压。如果栅极对源极偏置电压小于阈值电压,就没有沟道(channel)

阈值电压(Threshold Voltage)是指场效应晶体管(FET)中的一个重要参数,它表示在控制极(通常是栅极)的电压达到某个特定值时,晶体管开始导通或截止的阈值电压值。

对于 N 型场效应晶体管(N-channel FET),阈值电压是指在栅极和源极之间的电压,当栅极电压大于该阈值电压时,晶体管开始导电,允许电流从源极流向漏极。如果栅极电压低于阈值电压,晶体管截止,电流无法流过。

对于 P 型场效应晶体管(P-channel FET),阈值电压也是指在栅极和源极之间的电压,但与 N 型晶体管不同的是,P 型晶体管的阈值电压一般为负值。当栅极电压小于该阈值电压的绝对值时,晶体管开始导电,允许电流从漏极流向源极。如果栅极电压高于阈值电压的绝对值,晶体管截止。

阈值电压的具体值取决于晶体管的制造工艺和设计参数,并且可能会有一定的变化范围。对于不同型号和厂家的晶体管,阈值电压可能会有所差异。

阈值电压在场效应晶体管的工作和应用中非常重要。通过控制栅极电压与阈值电压之间的差异,可以实现晶体管的开关操作和信号放大。阈值电压也影响着晶体管的工作特性,如导通电阻、功耗和响应速度等。因此,对于设计和使用场效应晶体管的电路来说,准确了解和控制阈值电压是很关键的。

✍电荷陷阱

电荷陷阱(Charge Traps)是一种在半导体材料中存在的微观结构,能够捕获和储存电荷。

电荷陷阱通常是由材料中的缺陷或杂质引起的。它们可以是氧化物层中的氧空位、晶格缺陷或其他杂质离子。这些缺陷能够捕获和保留电子或空穴,将电荷储存在陷阱中,并在需要时释放电荷。

在非易失性存储器中,例如闪存,电荷陷阱被用来储存数据。在擦除和编程操作中,电荷被注入或移除到这些陷阱中,以表示数据的0和1状态。由于电荷在陷阱中的存储是非破坏性的,这种存储器可以保持数据即使在断电的情况下。

另外,电荷陷阱在一些半导体器件中也发挥重要的作用。例如,在深亚微米技术中的金氧半场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)中,引入电荷陷阱能够改善电子隧穿效应和减少子阱效应,提高器件性能和可靠性。

总之,电荷陷阱是半导体材料中的一种微观结构,能够捕获和储存电荷。它们在非易失性存储器和半导体器件中具有重要的应用,对设备的性能和功能起到关键作用。

✍bit line (BL)

在DRAM中,位线负责将数据传输到和从存储单元。DRAM阵列中的每个存储单元都连接到一对位线,分别称为真位线(BLT)和补充位线(BLC)。在读操作中,通过感测电路对存储单元电容中的存储电荷进行检测和放大,并将结果通过位线传输到存储控制器进行处理。在写操作中,存储控制器通过位线发送信号,以相应地充电或放电存储单元电容。

在闪存存储器中,位线起到类似的作用。它与浮栅晶体管相连接,负责将数据以电荷方式存储。在读操作中,浮栅中的存储电荷决定逻辑状态,并通过位线的电流流动进行检测。在写操作中,控制栅电压或位线电压被调整以改变存储在浮栅中的电荷,从而实现数据编程或擦除。

位线的设计和优化对存储器的性能至关重要,它们会影响速度、功耗和抗干扰等因素。为了增强位线在存储器系统中的操作和可靠性,采用了位线预充电、感测放大和差分传输等技术。

总之,位线是半导体存储器中的一个基础部件,作为存储单元与存储控制器或感测放大器之间的数据传输路径。其正常运行对于实现高效和可靠的数据存储和检索至关重要。

✍source line

在DRAM中,Source line是用于对存储单元进行读取和写入操作的电压供应线。每个存储单元都有一个对应的Source line,用于提供所需的电压来操作该存储单元。Source line通常与位线(Bit line)相连,并共同组成存储单元的存取单元电路。

在读操作中,Source line被预充电至一个特定的电压值。当选中特定存储单元进行读取时,Bit line的电压会根据该存储单元的状态(存储电荷)发生变化,Bit line上的电压变化会引起Source line上的电压变化。通过比较Source line上的电压变化,可以确定存储单元的状态(逻辑“1”或逻辑“0”)。

在写操作中,写入数据被放置在Bit line上,并将Bit line的电压变化传递到相应的Source line上。这样,写入数据的电压就被传递到选中的存储单元中,从而实现了数据的写入。

Source line设计的优化对于DRAM的性能和稳定性非常重要。它们的设计需要考虑功耗、噪声干扰等因素,以确保可靠的读取和写入操作。

总结而言,Source line是DRAM中用于读取和写入操作的电压供应线路。它们与Bit line一起构成存储单元的存取单元电路,用于传递电压信号以完成数据读取和写入。

✍Wordline

在SRAM中,Wordline是用于选中存储单元进行读写操作的线路。每个存储单元都有一个与之对应的Wordline。当Wordline被激活或使能时,相关的存储单元将被连接到读写电路,可以进行数据的读取和写入操作。Wordline的使能与否决定了哪些存储单元可以被访问。

在DRAM中,Wordline也扮演着类似的角色。每个存储单元都与一个特定的行(row)绑定,而每一行都有一个对应的Wordline。通过选中特定的Wordline,将确保只有与该Wordline相关联的存储单元可以被操作,例如读取或写入数据。

Wordline信号的生成和控制在存储器系统的电路中起着关键作用。它们需要精确的时间控制和电平控制,以确保正确地选中目标存储单元,并保持稳定的操作。

综上所述,Wordline是半导体存储器系统中用于选中存储单元进行读写操作的线路。它在SRAM和DRAM中起到关键的作用,用于决定可以被访问的存储区域,并传递相应的操作信号。

✍Source 源极和Drain 漏极

在场效应晶体管(Field-Effect Transistor,简称FET)中,源极(Source)和漏极(Drain)是两个重要的电极。

源极(Source)是场效应晶体管中的一个电极,它在工作时具有两个主要功能。首先,它是电子或电荷的来源,提供输入信号或电荷以激活晶体管的工作。其次,源极也是晶体管的电流输出端,通过源极流出的电流携带着信号或能量。

漏极(Drain)是场效应晶体管的另一个电极,位于源极的另一侧。漏极接收源极流出的电流,并将其引走,从而控制晶体管的输出电流。漏极处的电压和电流通过控制源极电流的大小来调节晶体管的放大和开关能力。

在N型场效应晶体管中,源极和漏极都是栅极(Gate)电压控制下的N区域。当栅极电压偏向源极时,形成一个导电通道,电流可以从源极流向漏极。当栅极电压与源极间的电位差(门源电压)超过一定阈值时,晶体管开始导通,即处于开启状态,允许电流流动。相反,当门源电压低于阈值电压时,晶体管处于截止状态,电流无法通过。

在P型场效应晶体管中,源极和漏极都是栅极电压控制下的P区域。其工作原理与N型场效应晶体管相反,但基本概念和功能相同。

总结而言,源极和漏极是场效应晶体管中的两个电极,分别负责输入信号或电荷,并控制输出电流。它们在晶体管的工作中起着重要的作用,根据其电势差和控制信号的变化,控制晶体管的通断和放大特性。

✍P型和N型晶体管

P型半导体材料和N型半导体材料是半导体材料中两种常见的类型。

P型半导体材料中,掺杂了少量的三价元素(如硼、铝等)。这些掺杂物会向半导体晶格中引入缺电子的空位,称为空穴。因为空穴在P型半导体中移动,所以也称为正电荷载流子。在P型半导体中,空穴是主要的载流子。

N型半导体材料中,掺杂了少量的五价元素(如磷、砷等)。这些掺杂物会提供额外的自由电子,使得半导体材料中存在自由电子的浓度增加。在N型半导体中,自由电子是主要的载流子。

P型和N型半导体材料的载流子类型相反,这是由于掺杂的不同元素导致了阴阳离子的形成。在P型半导体中,空穴是少数载流子,自由电子很少。而在N型半导体中,自由电子是主要的载流子,空穴很少。

通过将P型和N型半导体材料相互接触,形成P-N结,可以构建出各种半导体器件,如二极管、晶体管等。P-N结的形成使得半导体器件具有特定的电学特性,可以用于控制电流流动和信号放大等应用。

总之,P型和N型半导体材料的差异在于掺杂的不同元素和导致的载流子类型,它们在半导体器件的制造和工作原理中起着重要的作用。

✍衬底

衬底(Substrate)是半导体器件制造过程中的关键元素之一。它是构成芯片的基础材料,通常是将其他层次的组件和电路结构构建在其上的平坦硅片或其他半导体材料上。

MOS下面的衬底又叫nwell和pwell,是因为它们的极性不同,nwell是n型晶体管的衬底,pwell是p型晶体管的衬底。nwell和pwell的区别在于,nwell是由n型半导体材料制成的,而pwell是由p型半导体材料制成的。

在集成电路制造过程中,衬底扮演着多个重要的角色:

1. 支撑层:衬底提供了一个坚固的基础平台,以便在其上构建更多的电子元件和结构。它具有足够的机械强度和平坦度,以支持后续的加工步骤。

2. 晶体生长:对于许多半导体器件,衬底可以作为晶体生长的基底。通过在衬底上进行适当的化学处理和热处理,可以在其表面上形成单晶或多晶晶体结构,用于制造晶体管、二极管等器件。

3. 衬底接地:在许多电子器件中,衬底通常与接地(Ground)相连,起到电路中的参考点和屏蔽作用。这对于保持电路的稳定性和抑制噪声干扰非常重要。

4. 绝缘层分隔:对于某些器件,衬底上的绝缘层(如二氧化硅)可以用于隔离不同区域的电路结构,以避免电子器件之间的干扰和短路。

需要注意的是,衬底的材料与特定的制造工艺和应用有关。在典型的硅基集成电路中,硅衬底是常见的,而在一些特殊的应用中,如复合材料和大规模集成电路中,可能会采用其他材料作为衬底。

总而言之,衬底是半导体器件制造中的基础平台,提供支撑、晶体生长、接地和隔离功能。它在构建芯片的不同层次和组件时扮演着至关重要的角色。

994

994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?