(EDA工具未完待续)

(EDA工具未完待续)

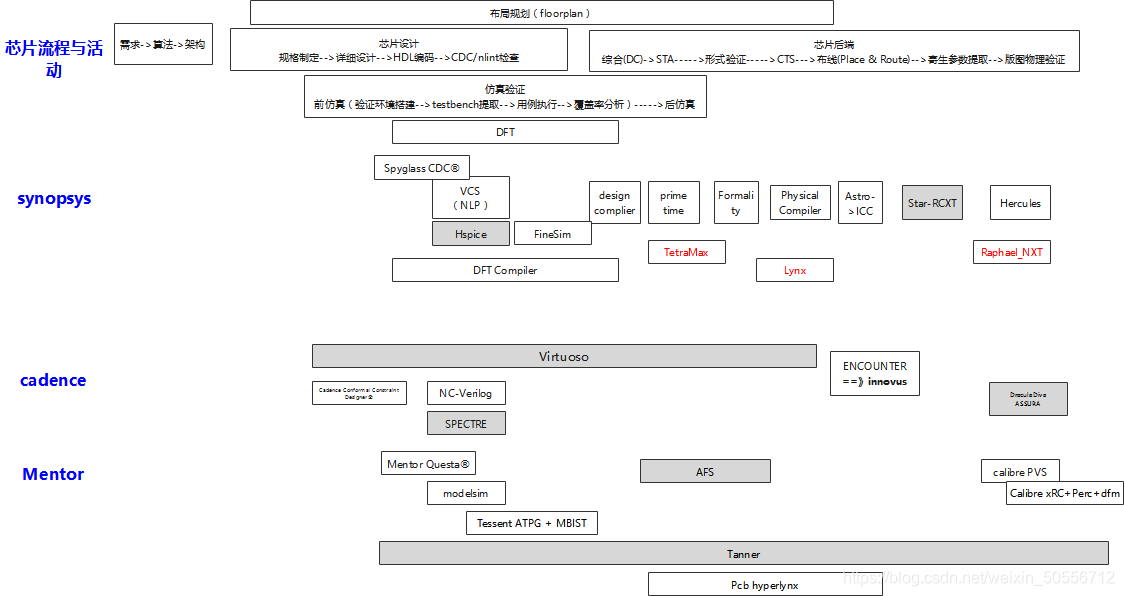

Synopsys:

1、spyglass:CDC相关工具。CDC,跨时钟域设计,是设计工作中很重要的技术点。

2、VCS工具:verilog仿真工具。

3、design complier-NXT:综合工具。综合需要具备的知识:综合概念和流程、库文件类别、时序约束的基本知识,多时钟与复杂设计约束、DC Ultra综合技巧、SPG flow,DC工具进行综合基本操作、编写综合约束文件、综合结果的时序和congestion分析等贯穿综合全流程的实践技能。详情请见:https://mp.weixin.qq.com/s/0vO763XfCSoSqt-gloegpA

4、Prime Time:静态时序分析工具和SI工具。静态时序分析(Static Timing Analysis,STA)是流片成功的关键环节,验证设计在时序上的正确性。STA过程中设计环境和时序约束的设定、时序结果的分析和问题解决都需要设计工程师具有专门的知识和技能。同时,集成电路设计进入了超深亚微米领域,金属层增加、线宽减小,串扰延迟、噪声等信号完整性问题(SI)对工程师的时序分析能力和水平要求越来越高,在一些大的芯片设计企业

本文介绍了芯片开发流程中三大EDA厂商Synopsys、Cadence和Mentor的主要工具,包括静态时序分析、布局布线、等价性验证、模拟仿真等方面,为芯片设计工程师提供关键工具信息。

本文介绍了芯片开发流程中三大EDA厂商Synopsys、Cadence和Mentor的主要工具,包括静态时序分析、布局布线、等价性验证、模拟仿真等方面,为芯片设计工程师提供关键工具信息。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

944

944

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?