PL端开发工具:VIVADO 2017.4

PS端开发工具:Xilinx SDK 2017.4

ZYNQ器件:XC7Z020-2CLG400I

说明:在使用ZYNQ时进行寄存器读写时主要的思路还是分配一段地址空间来进行控制,通过在SDK中对该段地址的读写操作来控制PL端的IO输入输出。

一、创建Block Design 图形化设计

在之前ZYNQ详细设计之VIVADO相关操作有关于boclk design(bd)的设计流程,这里说一下关于BRAM的相关设计。

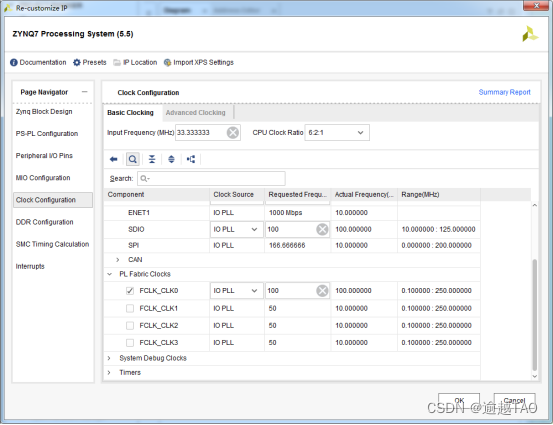

在本次的设计中只需要使用CLK0就行。

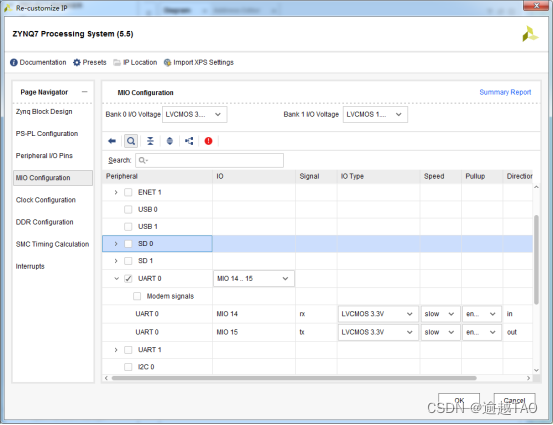

PS端接口使用UART 0用于打印信息就可以了,这里串口的引脚需要根据自己板子上面的引脚来分配,我的板子这里使用的引脚是MIO 14和MIO 15。

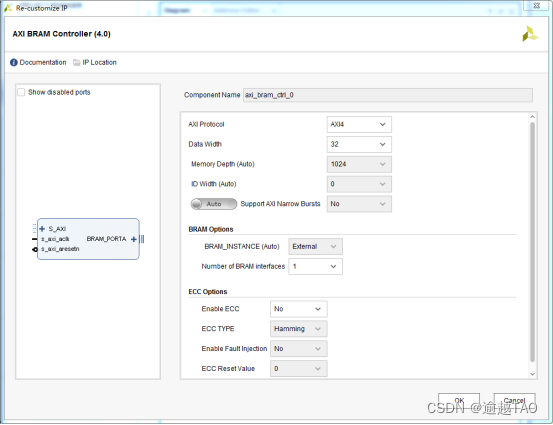

ZYNQ相关设置完成后添加AXI BRAM Contrller进行设置,添加好后双击进行设置,在Number of BRAM interfaces中使用1个接口即可,数据位宽选择32,内存深度根据使用的内存大小自动生成,在修改Address Editor中内存大小后变化,这里简单使用,只需要深度1024即可;

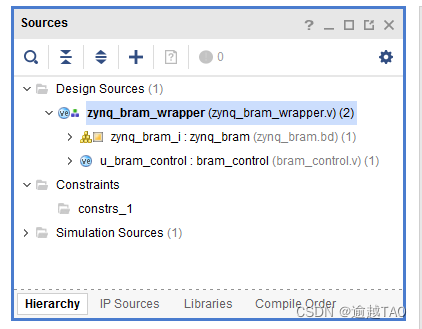

然后自动连接会将ZYNQ和BRAM通过一个连接器(AXI SmartConnect)连接起来,然后选中BRAM_PORTA接口将其引出,完成后验证设计,保存后就完成了bd的相关设计。选中bd工程右键选择Greate HDL Wrapper。

二、工程例化和PL端设计

根据BRAM接口的相关控制时序,将BRAM引出的相关接口进行例化到一个单独的module中进行分配内存地址来进行地址映射。

这里在bram_control设计当中添加Ila来观察相关控制时序和对应寄存器的值。

设计完成后生成bit文件,导出硬件信息,打开sdk进行设计。

三、PS端读写BRAM内存

打开SDK后可以先看一下硬件信息和地址是不是和设置一致,一致后开始创建工程,这里简单的BRAM控制我们可以直接使用自带的memory tests程序进行测试。

3.1、测试程序

下面是BRAM的测试程序:

#include <stdio.h>

#include "xil_printf.h"

#include "xil_cache.h"

#define MAX_PKT_LEN 8

#define NUMBER_OF_TRANSFERS 8

#define TEST_START_VALUE 1

#define TX_BUFFER_BASE 0x40000000

#define RX_BUFFER_BASE 0x40000000

volatile u32 success;

int i;

int Index;

u32 *TxBufferPtr=(u32 *)TX_BUFFER_BASE;

u32 *RxBufferPtr=(u32 *)RX_BUFFER_BASE;

u32 Value;

int main()

{

xil_printf("\r\n----BRAM Controller Test----\r\n");

xil_printf("PKT_EN = %d\r\n",MAX_PKT_LEN);

for(i = 0; i < NUMBER_OF_TRANSFERS;i++)

// while(1)

{

Value = TEST_START_VALUE + (i & 0xff);

for(Index = 0; Index < MAX_PKT_LEN; Index++)

{

TxBufferPtr[Index] = Value;

// TxBufferPtr[4] = 5;

// xil_printf("write data TxBufferPtr[%d]=%0x,addr=%0x\r\n",Index,TxBufferPtr[Index],&(TxBufferPtr[Index]));

Value = (Value + 1) & 0xFFFFFFFFF;

}

u32 a = 0;

for(Index = 0; Index < MAX_PKT_LEN; Index++)

{

// xil_printf("read back RxBufferPtr[%d]=%0x\r\n",Index,RxBufferPtr[Index]);

a = RxBufferPtr[Index];

}

}

xil_printf("\r\n----BRAM Controller Test done----\r\n");

return 0;

}

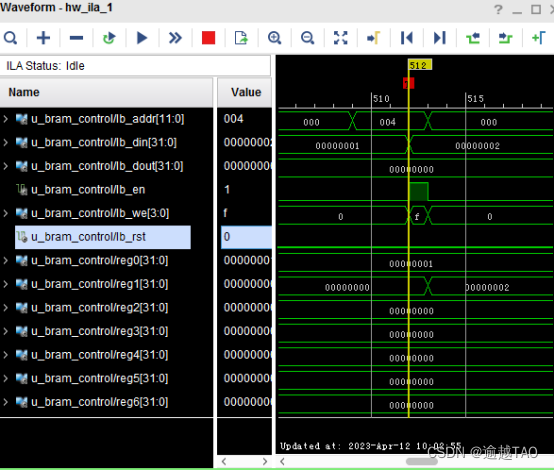

3.2、BRAM写时序

TxBufferPtr传输缓存(PS -> PL),将pl端分配的基地址0x40000000赋给缓存指针初值,操作该缓存地址即可往PL端对应地址中写入数据;如下图所示,当TxBufferPtr[1] = 2时,相当于向addr = 1中写入data = 2,对应向PL端addr = 0x4000_0004中写入data = 2,对应向BRAM的lb_addr = 0x004中写入lb_din = 2。

在测试代码前面打上断点,观察BRAM的写时序,下图是向addr = 1写入data = 2时抓取到BRAM时序图:

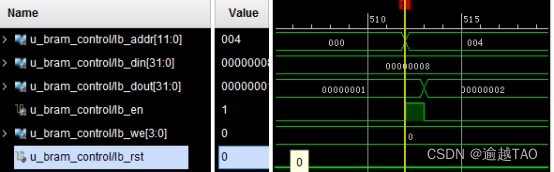

3.3、BRAM读时序

RxBufferPtr接收缓存(PS <- PL),将pl端分配的初始地址0x40000000赋给缓存指针初值,操作该缓存地址即读出PL端对应地址中的数据;如下图所示,当RxBufferPtr[1]=2时,相当于向addr =1中读数据,对应向PL端addr = 0x4000_0004中读数据,对应向BRAM的lb_addr = 0x004中读数据,可以看到读出的数据lb_dout = 2;

在测试代码前面打上断点,观察BRAM的读时序,下图是读出addr = 1的数据data = 2时抓取到BRAM时序图:

下图是串口打印的信息,可以看到通过串口打印出来接收的数据也是RxBufferPtr[1] = 2;

上面是在程序中打断点,单次运行,可以不打断点,连续读写进行测试,经过测试连续读或者连续写一次会占用28个周期(1个周期10ns)。

总结:以上就是关于BRAM的内存映射,可以通过BRAM来进行寄存器控制,从而控制PL端IO端口,控制外部芯片。有什么问题欢迎交流。

477

477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?