ZYNQ基础模块串口的意义

ZYNQ的配置介绍

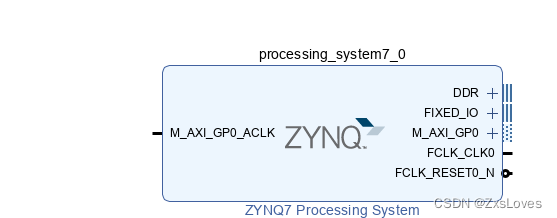

如此纯粹的引脚显示

DDR 用来接DDR FIXED_IO 主要用来调试

现在一步一步配置出PS与PL端想沟通的zynq核

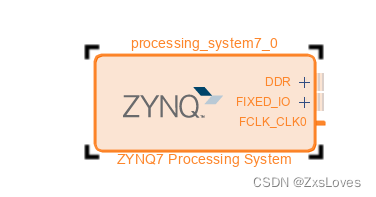

第一步给PL端添加一个时钟

因为 PS 与 PL端的时钟晶振不一样 我们可以通过一个PLL 来帮助我们生成想要实现的PL端时钟

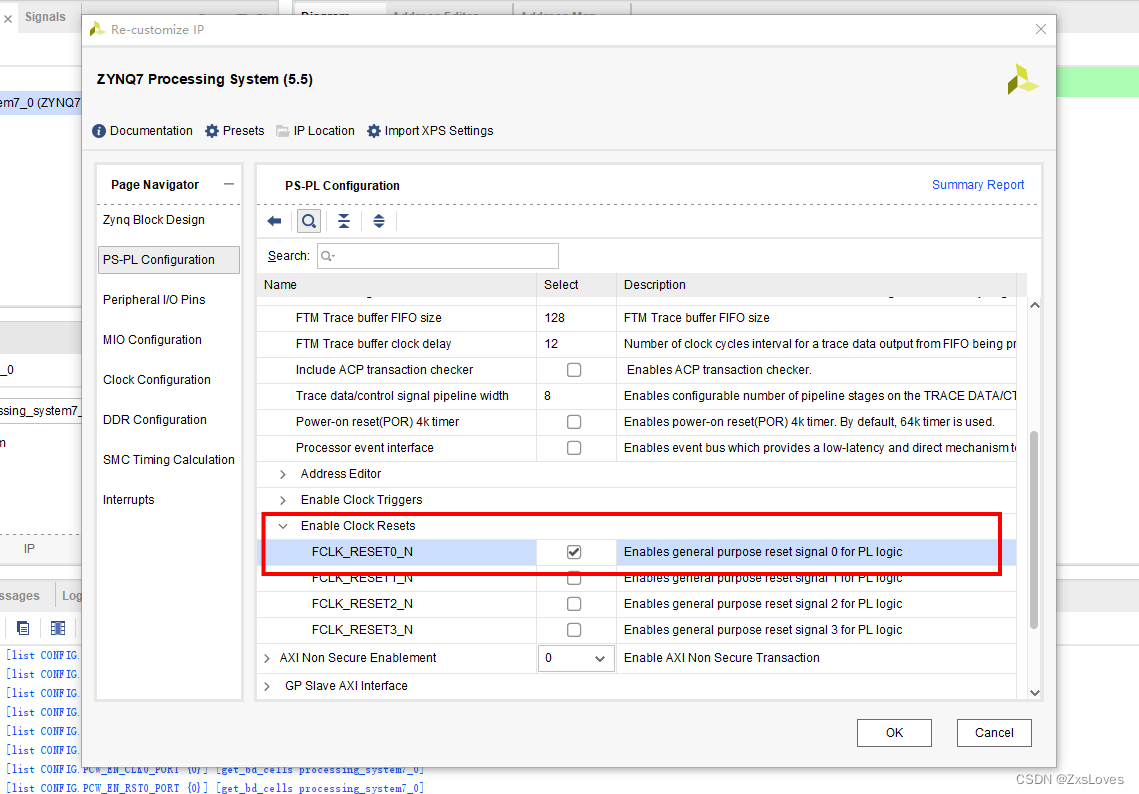

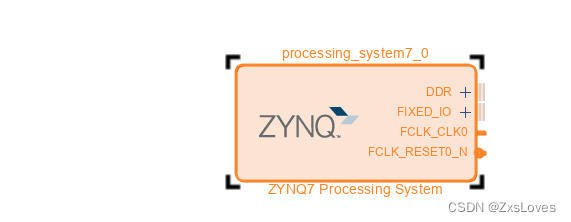

第二步 给PL端添加一个复位引脚

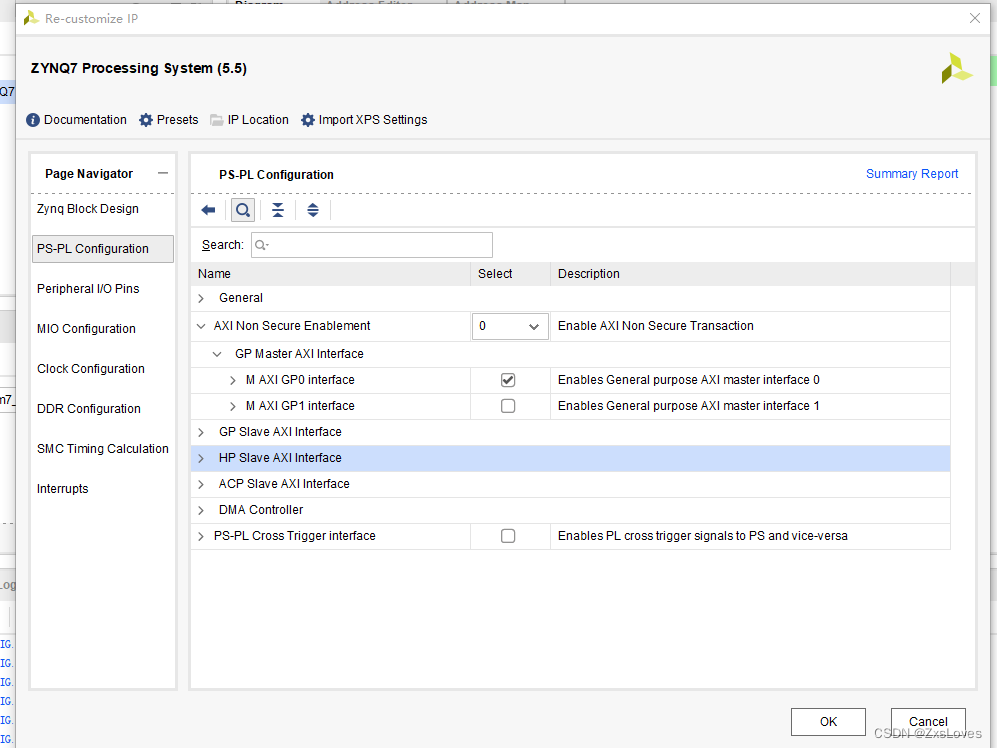

接下来添加 GP接口 用来传输控制信息

GP用来 PS作主机

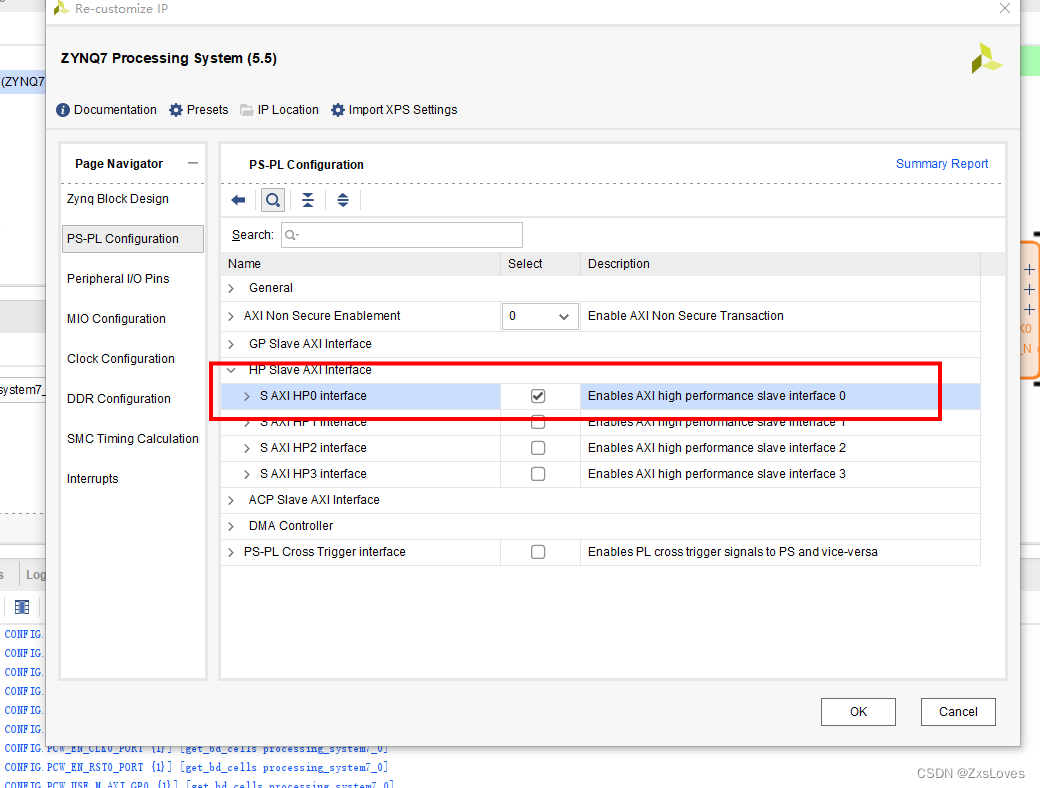

接下来 添加 PS 与PL互动的数据接口

S_AXI_HP0_FIFO_CTRL 是 Zynq UltraScale+ MPSoC 的 AXI High Performance (HP) Slave Interface 的 FIFO 控制寄存器接口。在这个接口中,S_AXI_HP0 表示第一个高性能 AXI 接口。

以下是该接口的一般含义:

- S_AXI_HP0:

AXI High Performance 接口的第一个实例。这是一个高性能的 AXI 总线接口,通常用于连接处理系统 (PS) 和可编程逻辑 (PL) 中的高性能外设或内存控制器。 - FIFO_CTRL:

FIFO 控制寄存器接口,用于控制和配置与该 AXI 接口相关的 FIFO。

这个接口允许对 FIFO 进行一些配置,如深度、中断使能等。通过配置这些参数,可以优化 AXI 总线与 FIFO 之间的数据传输。详细的配置和功能取决于具体的硬件设计和应用需求。

在使用这个接口时,设计者通常需要参考相关的技术文档和数据手册,以了解具体的寄存器配置和接口使用方法。

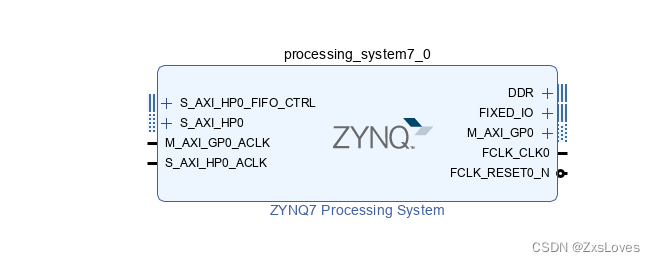

完成这是基础zynq串口的含义与配置

8403

8403

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?