乒乓操作的思想

乒乓操作主要是为了处理,输入时钟和输出时钟不匹配的问题,也可以算跨时钟处理

对于乒乓操作我主要参考了野火的文档,以及下面这篇文章彻底弄懂乒乓操作与并行化_快,快去救列宁!的博客-CSDN博客_乒乓buffer

下面开始进入正文

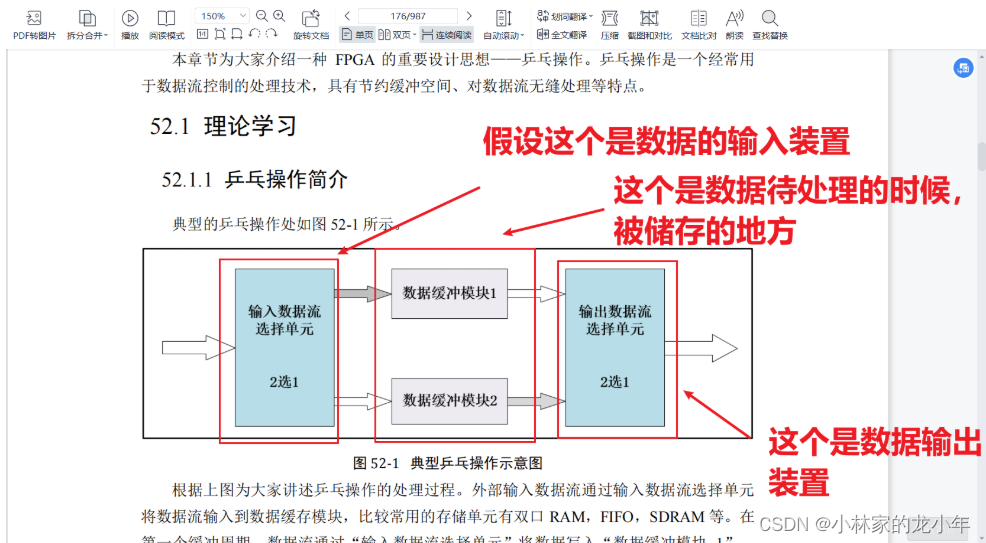

比如假如我现在要处理一系列的数据,数据的输入时钟是100M,但是输出数据的时钟受外部的设备限制,只能有50M时钟,那么也就是说,在相同的时间内,输入了100个数据,而此时我们只能输出50个数据的处理结果,那么只会导致未处理的数据越来越多。那么怎么处理这样的问题呢?这个时候就需要采用乒乓思想了,如下

那么怎么处理这个问题呢?我们采用下面的思路

这就是所谓的面积换速度,那么我们也就是用了两块RAM(也就是两个存数据的队列),实现了跨时钟的处理

对于Verilog代码,由于我调用了RAM的ip核,所以可能会出现调用不成功的现象,所以直接采用看波形,如下

可以看到当8位宽的数据源源不断地输入的时候,16位宽的数据在两个队列之间源源不断的输出,而且是交替输出

如果想自己看波形的话,直接去用野火的代码也可以,网站如下。是第43个项目

ebf_ep4ce10_pro_tutorial_code: 配套代码《FPGA Verilog开发实战指南——基于Altera EP4CE10》

下面讲一种比较特殊的乒乓思想

1729

1729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?