最近想写一篇关于ZYNQ快速入门的文章,而由于ZYNQ的精髓实质上是如何建立ARM和FPGA之间的联系,所以准备先写一篇关于AXI协议快速入门的文章来打一下基础,也是顺便让我回忆一下AXI协议。

本篇文章包含的主要内容是AXI协议的基础知识,以及如何在vivado中快速调用AXI协议,来进行ARM和FPGA之间的联系。

一、AXI协议的基础知识

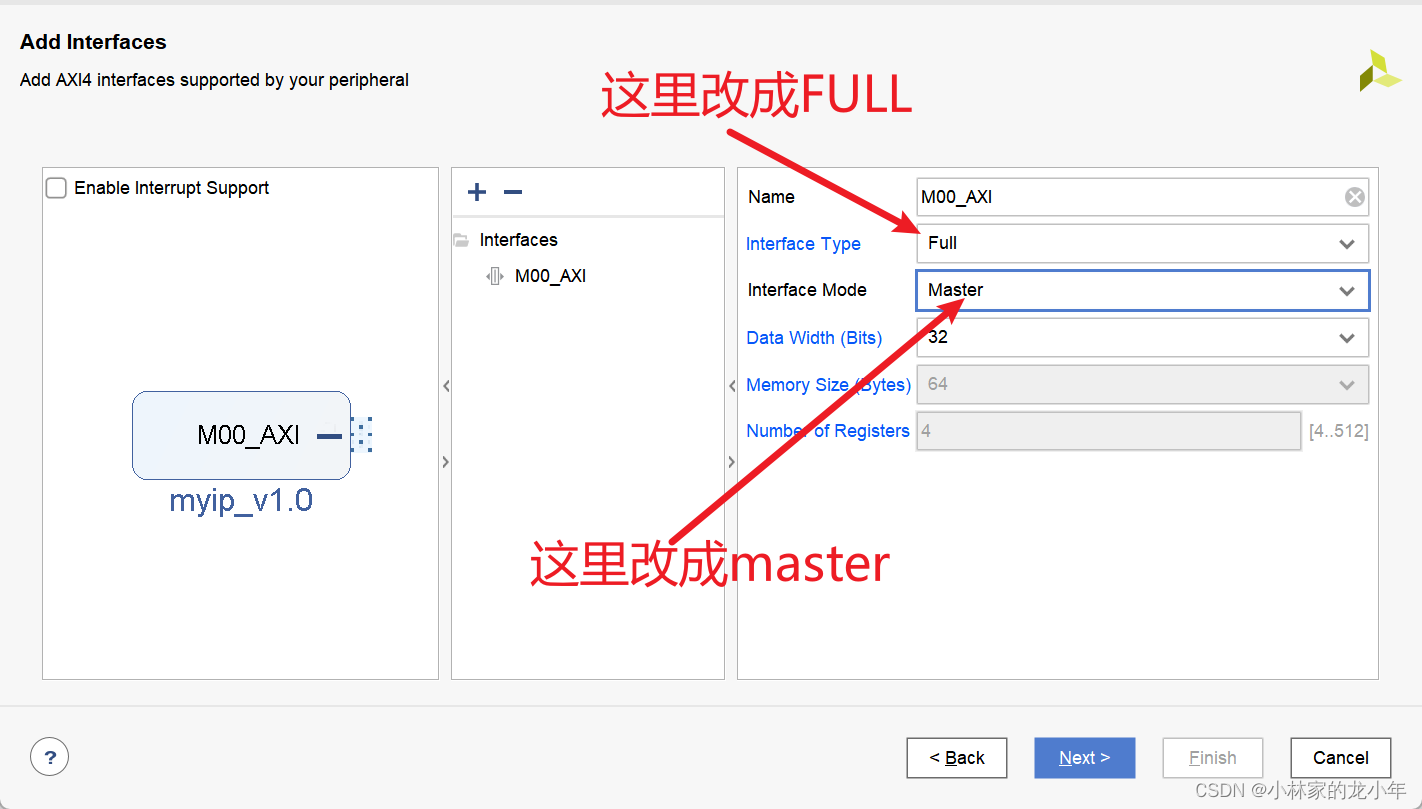

AXI协议主要包括三种类型,分别是AXI-full、AXI-stream以及AXI-lite协议,其中AXI-full协议的接口最为复杂,也是在平常工作中用的最多的协议。而AXI-stream协议的接口没有AXI-stream的多,主要用于视频流的场景下。AXI-lite则经常用于非常少量的数据传输,用的不多。通常我们可以用ram来比作AXI-full协议,而fifo则可以比作AXI-stream协议,这样理解的就比较形象。本文主要一AXI-full协议为主,如果想要理解AXI-stream协议,我的建议是可以看看ARM公司对AXI-stream协议的数据手册。

对于用过ZYNQ开发的人应该知道,带AXI接口的ip核往往会因为他庞大的接口数量让人望而却步,心想我只是想建立ARM和FPGA之间的数据通信,怎么这AXI协议这么复杂,我还怎么进行数据通信,就如下图一样。

上图的右边就是完整的AXI-full接口,看起来都觉得尼玛怎么这么多。但其实这么多接口中有很多是取固定取值,真正使用的接口数量是没有很多的,在本文讲到AXI协议应用的时候,其实我们会发现XILINX公司自己都会对AXI-full协议进行简化,把重要的接口提取出来,所以我们不用慌。

虽然AXI-full有如此多的接口,但其实ARM公司已经将AXI-full协议中的接口进行了分类,如下:

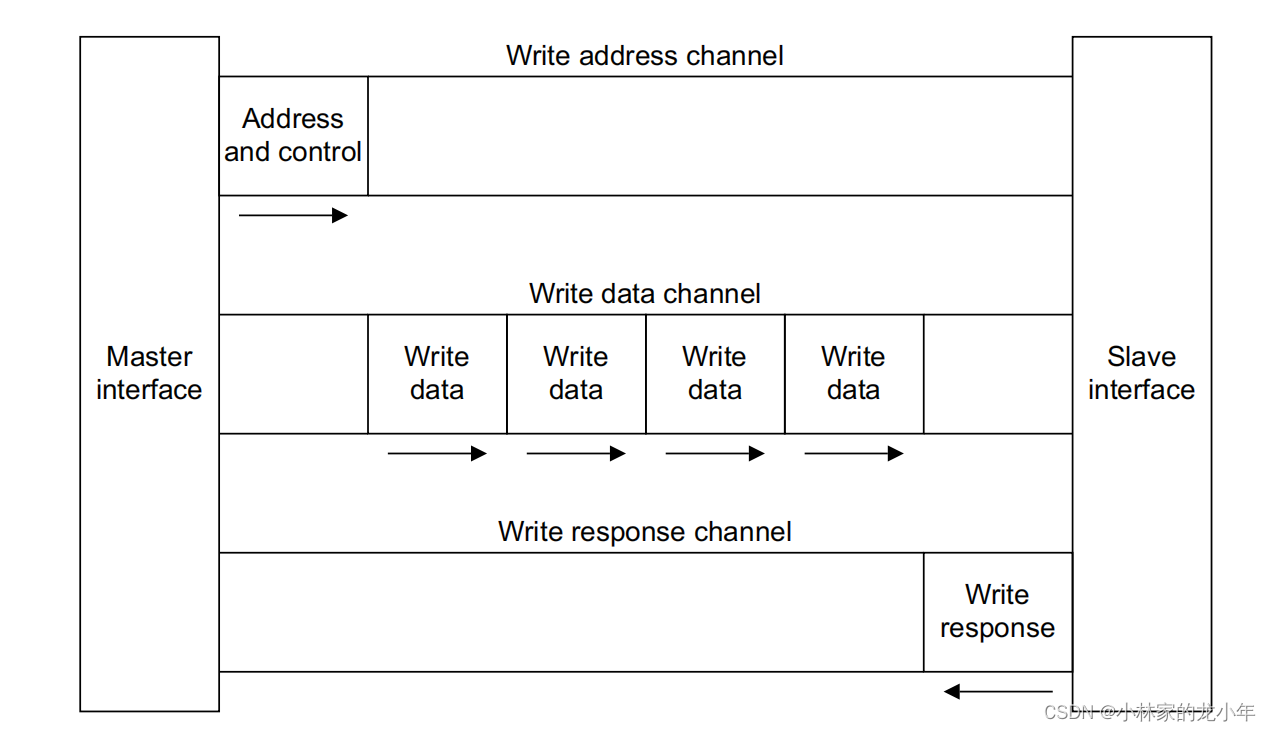

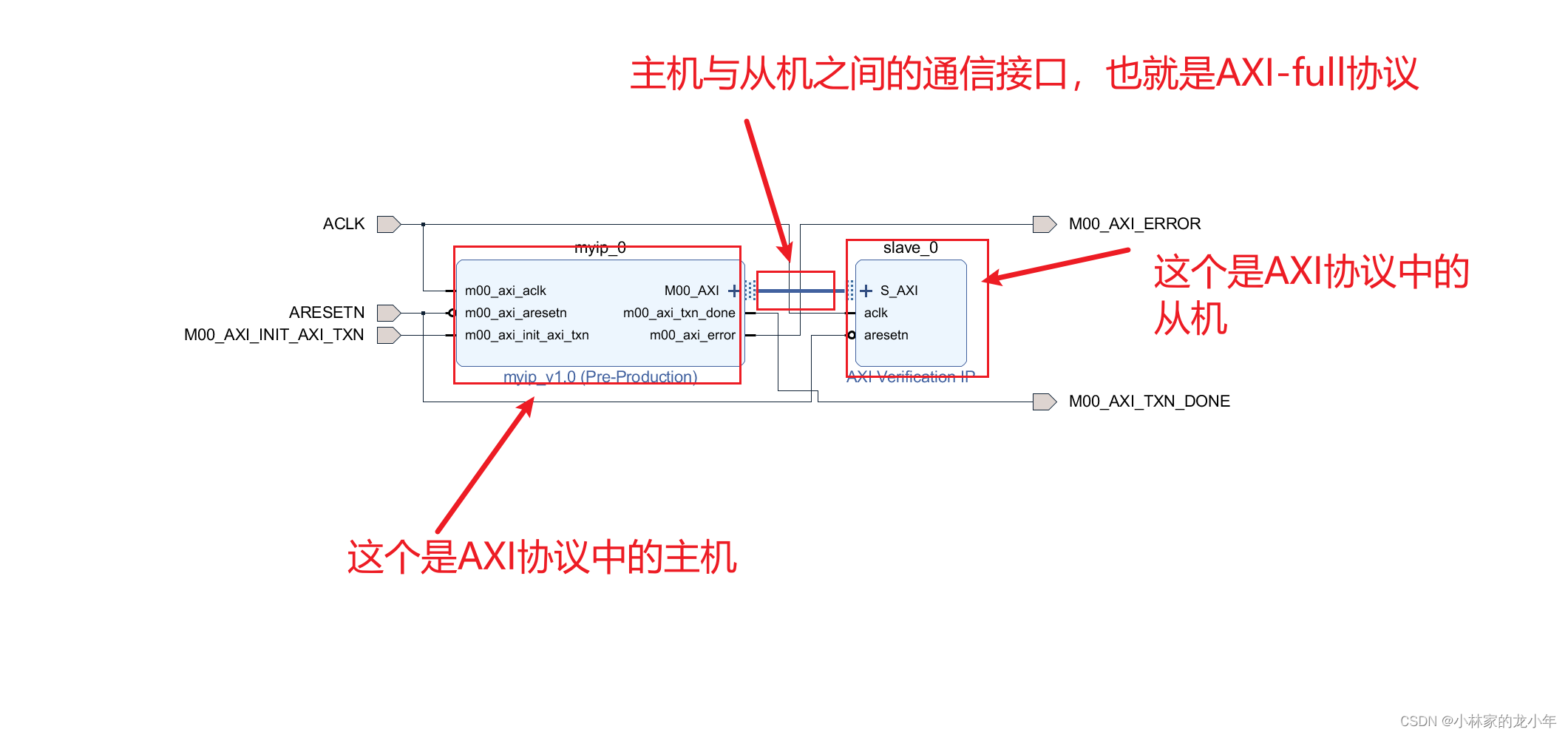

在AXI-full协议中,我们认为是一个主机对一个从机使用AXI-full协议进行数据通信,主机可以对从机进行写入数据,主机也可以对从机进行数据读出,其中我们称主机为Master,从机为Slave,上图就是展示主机对从机进行数据写入。可以看到主机要对从机进行数据写入的话,一共需要三种类型的接口,分别为写地址通道,写数据通道,以及写响应通道。当主机要对从机进行数据写入,首先是主机将要写入的地址告诉从机,然后接下来就是把写入的数据写入从机,最后从机会告诉主机是否接受到数据。这样大体上来看其实AXI-full协议也就没有这么复杂了,不就是和用ram一样吗,只不过是多了一个写响应通道。

然后我们来看看主机对从机进行数据读出,如下:

主机要对从机进行数据读出,首先是告诉从机要读哪个地址的数据,随后从机就把对应地址的数据进行读出供主机使用。那么之所以读出数据比写出数据少一个响应的通道,是因为在读出数据时主机没有义务告诉从机我已经接受了你的全部数据,而在写入数据从机是有义务告诉主机我有没有接受你的全部数据。

在理解了AXI-full协议的大框架之后,接下来就需要将这5个通道一一拆开,看看里面的具体时序是什么。在这里我们以ARM公司对AXI-full协议的数据手册为准,来具体介绍AXI-full协议的具体时序。

写地址通道

首先我们来讲讲写地址通道,他的具体接口介绍如下:

在上图中包含了写地址通道的所有接口,可以看到AXI协议的写地址通道的接口比ram的写地址通道的接口是要复杂的多,在ram中写地址可能就是一个信号address,但AXI协议的写地址信号却有14个之多,但其实这14个中并不是每个都很重要,重要的接口已在上面用黄色重点突出,一共有6个信号,下面我们也只介绍这6个信号。

第一个信号是AWADDR,该信号是给出主机要给从机的哪个地址进行写入数据。从上图可以看出ARM公司对AWADDR的描述是The write address gives the address of the first transfer in a write burst transaction,也就是该信号是给出一次写突发传输的首个传输数据的地址。其中写突发传输的意思就是,比如我给ram要写入一串数据,我规定这串数据我不会写一个数据就变一次地址,我觉得这样太麻烦,我的想法是,我4个数据为一组进行写入,在这4个数据传输的过程中我的地址信号一直不变,直到我这4个数据写完,我就把我的地址信号加4就可以,这样就不用我写一个数据就变一次地址。在AXI-full协议中我们常用的也是突发模式,也就是写完一串数据之后再变地址,其中AWADDR每次显示的都是一次突发传输中的第一个数据的地址。

第二个信号是AWLEN,ARM公司对其的描述是The burst length gives the exact number of transfers in a burst,也就是给出了一次突发传输要传输多少个数据。在数据手册中,还有这样的一段话需要注意:

也就是实际突发数据传输长度,是AWLEN + 1,也就是如果AWLEN为15的话,那么一次突发传输中实际传输的数据个数是16个。

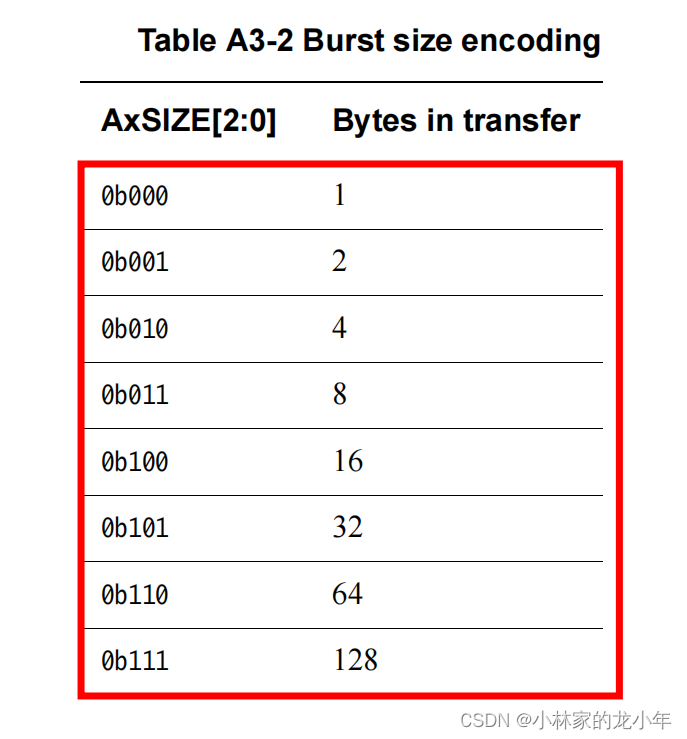

第三个信号是AWSIZE,AWSIZE容易和AWLEN信号搞混,AWSIZE信号说的是在一次突发中的传输数据长度是多少。可以这样去理解AWSIZE和AWLEN之间的关系,假如AWLEN等于16,也就是说一次突发会传输16个数据,而AWSIZE指示的是这16个数据中的每个数据包含几个字节,比如AWSIZE等于4,就代表一个数据有4个字节,那么一次突发会传输16个数据,就代表一次突发会传输16*4 = 64个字节。在数据手册中,有这样一段话需要注意:

上面这个表的意思就是说,当AWSIZE等于2的时候,并不是代表一个数据只有2个字节,而是有4个字节。

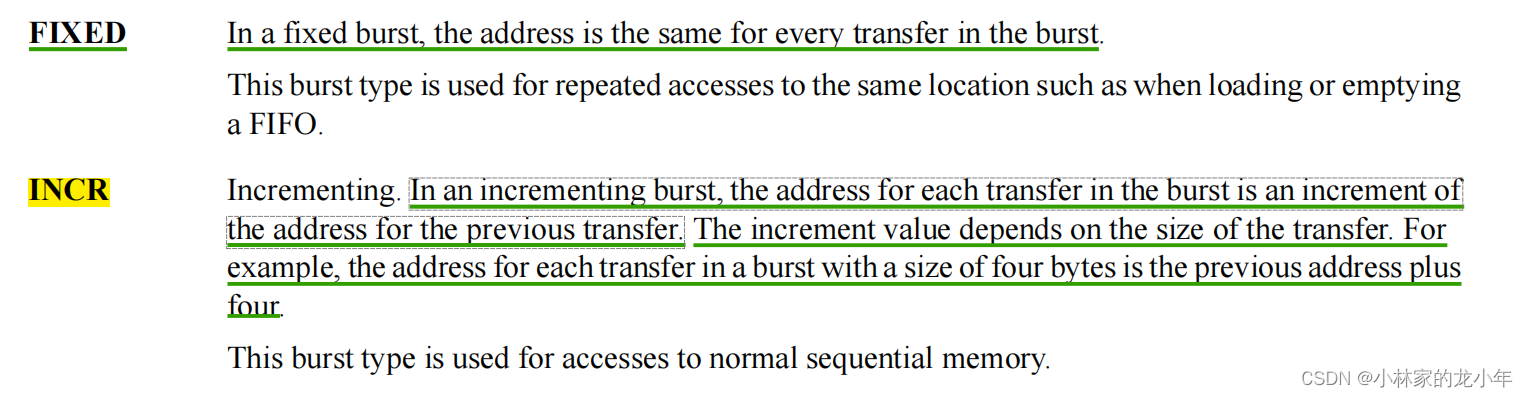

第四个信号是AWBURST,对于该信号,ARM公司是这样描述的:The burst type and the size information, determine how the address for each transfer within the burst is calculated.也就是说AWBURST信号实际上影响的是写地址的变化。在数据手册中,我们还需要注意这样一段话:

上图展现了AWBURST取不同的值时,AXI信号就会有不同的模式。其中FIXED模式指的是每次突发传输地址都不会发生改变,也就是说主机一直向从机的固定地址写入数据,而地址不会改变。而INCR模式指的是每次突发结束之后,地址都会自增,也就是我们常用的模式。当AWBURST为01时,代表INCR模式。

第五个信号是AWVALID,也就是写地址有效信号。对于AXI协议,他最大的特色就是握手,也就是在5个通道中都会有valid信号和ready信号,valid信号被发送数据的一方用于告诉接收数据的一方我现在发送的数据是有效的,而ready信号被接收数据的一方告诉发送数据的一方我已经准备好接收数据了。只有当valid和ready信号同时为高电平的时候,数据才能正常发送。在写地址通道中,由于主机是发送数据的一方,所以主机来发送AWVALID,而从机是接收数据的一方,所以从机来发送ready信号。

第六个信号是AWREADY,也就是写地址准备信号,在上文已经详细描述,不再赘述。

写数据通道

接下来介绍写数据信号,他的具体通信接口如下:

可以看到写数据通道的数据接口少了很多,下面一个个来介绍:

第一个是WDATA,也就是写数据信号,这个没什么好说的,就是传输写入的数据。

第二个是WSTRB,ARM公司对该信号的描述是This signal indicates which byte lanes hold valid data. There is one write strobe bit for each eight bits of the write data bus.意思是WSTRB指示了对于WDATA信号,哪些字节是有效的。比如说假设WDATA是32个Bit,也就是4个字节,那么如果WSTRB为4'b1111的话,就代表这4个字节全部有效。在实际运用中,我们也是默认WSTRB每个Bit位均为高。

第三个是WLAST,ARM公司对其的描述是The master must assert the WLAST signal while it is driving the final write transfer in the burst,也就是在每次突发传输的最后必须让WLAST为高电平。比如说我们每次突发传输16个数据,那么在传输第16个数据的时候WLAST必须为高电平。

第四个和第五个信号分别是WVALID和WREADY信号,这里就是由主机发送WVALID信号,由从机发送WREADY信号。

写响应通道

接下来介绍写响应通道,他的具体接口通信如下:

第一个信号是BRESP,ARM公司对其的描述是This signal indicates the status of the write transaction,也就是说BRESP显示的一次写入数据是否成功,BRESP是在一次突发传输数据之后,也就是传输完16个数据之后就会显示。在数据手册中,我们还需要注意这样一段话:

也就是说当BRESP为00的时候,就代表写入数据是成功的。

第二个和第三个信号是BVALID和BREADY信号,不再赘述。

读地址和读数据通道

对于读地址和读数据信号,和写地址写数据信号是一样的,在下面仅列出相关接口,不再赘述。

二、快速调用AXI协议

查看AXI的具体时序

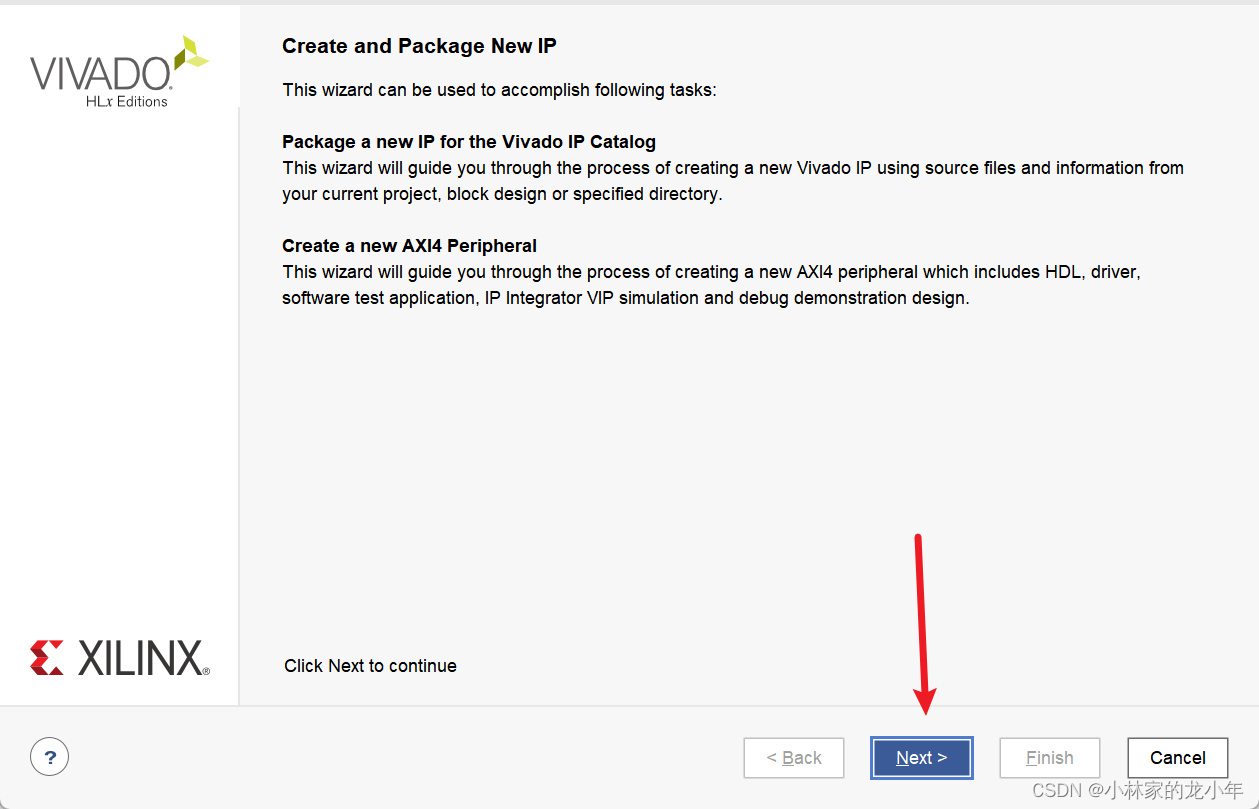

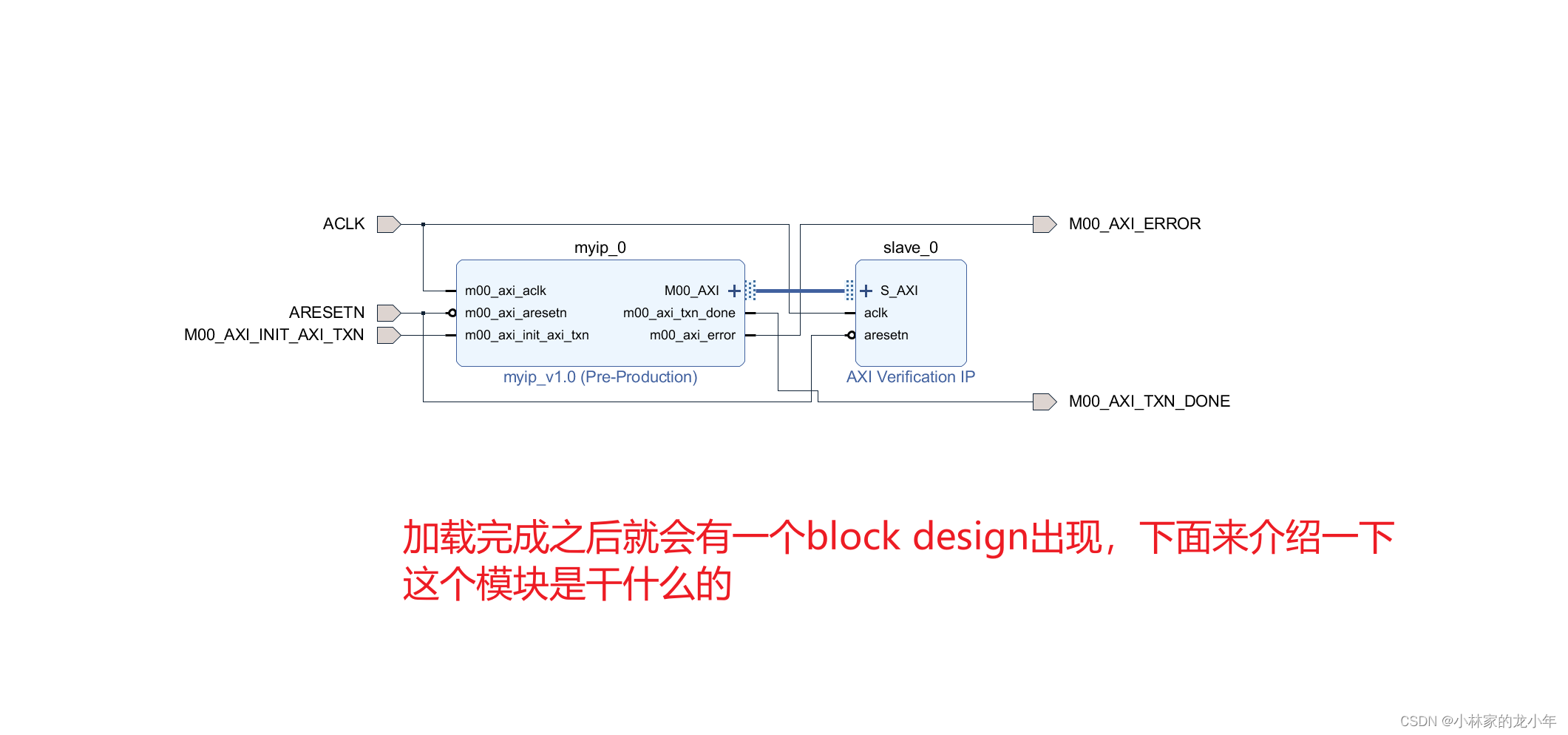

在讲完AXI-full协议的基础之后,接下来讲讲怎么在vivado中快速调用AXI协议,建立起ARM和FPGA之间的通信。首先来讲讲如何在vivado中查看AXI的具体时许:

那么对于想要具体去看AXI协议的时序是怎么样的同学,可以自己去看看仿真,可以结合我前面讲的AXI协议的基础知识去看,难度不是很大。

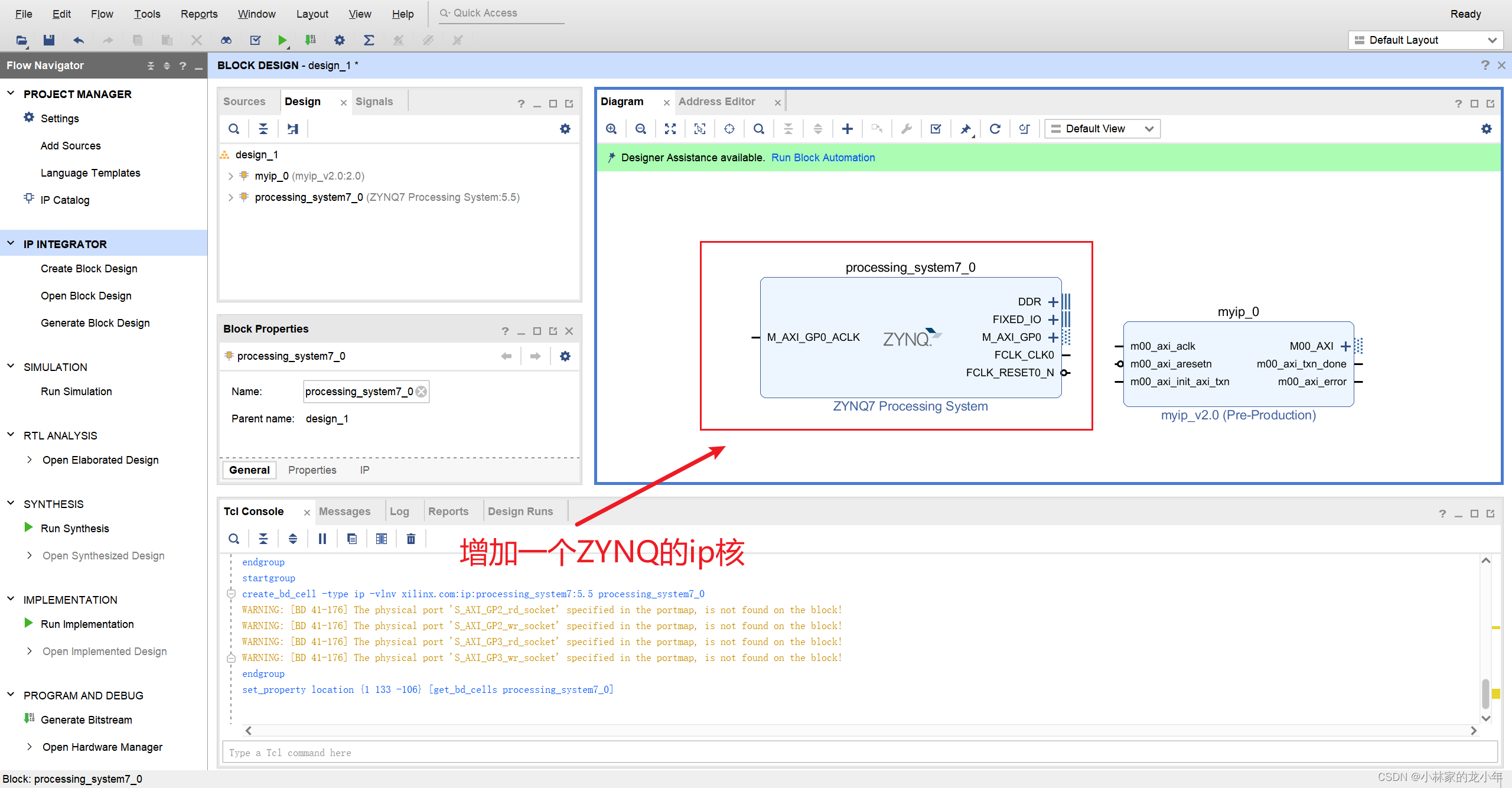

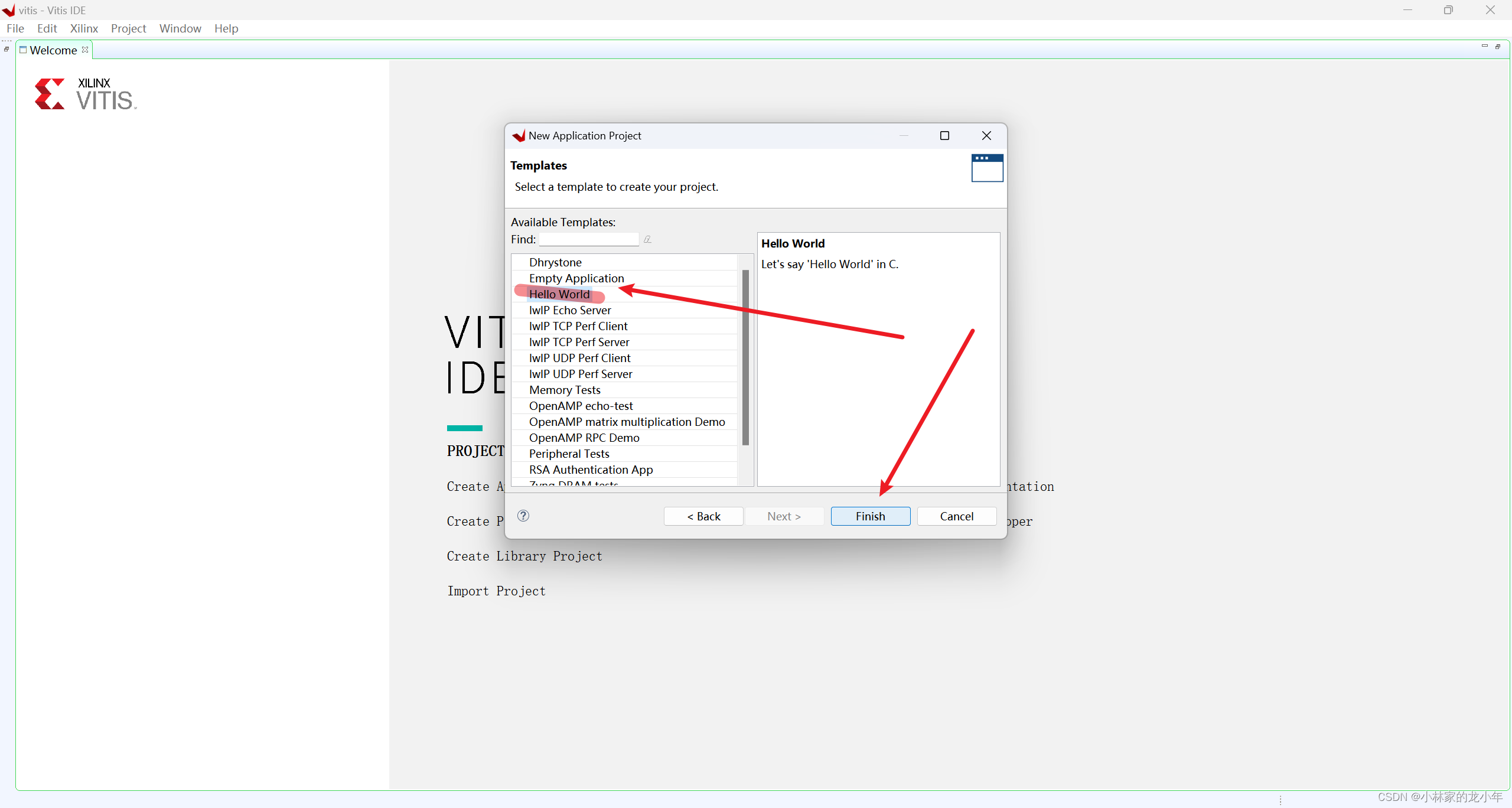

快速建立FPGA和ARM之间的数据通信

接下来重新建立一个项目,本项目的主要内容就是FPGA通过ARM往DDR内存的某一固定地址写入一定的内容,然后FPGA再通过ARM从DDR内存的相同地址中读取内容,如果写入的内容和读出的内容相同,则说明本次实验成功建立FPGA和ARM之间的数据通信

这里之所以要启用串口是为了后期方便打印信息

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

int main()

{

u32 MM2F_BASE_ADDR = 0x10000000;//确定FPG存放数据的地址

u32 *m2f = (u32 *)MM2F_BASE_ADDR;//定义m2f变量方便后面进行运算

int i = 0;

for(i=0;i<4096;i++){

printf("the %d is %d\n",i,m2f[i]);

}

return 0;

}本文写到这里有点烂尾,但不管了先发再说

2412

2412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?