哇 小丑竟是我自己!

我自己的文章与我自己的文章高度相似然后发不出来了。。。

所以说,这是一篇转载(狗头)

只好以图片的形式展示。。

下一个教程:

Vivado 2018.3入门教程(三):生成比特流文件+硬件连接.

想要完整的进行一个实验的话,可以参考这个教程!

FPGA实战(一)LED闪烁实验.

(3)逻辑编写(笔记都在注释里哦)

module led_twinkle2(

//这里面定义输入输出端口,如果刚才定义了这儿就会自动生成

);

//编写用户逻辑代码

endmodule//模块结束

下面开始编写逻辑

module led_twinkle2(

//这里面定义输入输出端口,如果刚才定义了这儿就会自动生成

input clk,

input rst_n,//_n是低电平有效

output [1:0] led//建议对齐

);

//编写用户逻辑代码

reg [25:0] cnt ;

//此处需要计算,50MHz的时钟频率,1s中就要计数50000000次,换算成二进制的位宽为26位

//(2)部分

assign led = (cnt < 26'd2500_0000)? 2'b01 : 2'b10 ;

//(1)计数器部分

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)//复位信号低电平有效的阶段

//当复位的时候,需要给计数器清零

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)//复位结束之后,就是进行计数

cnt <= cnt + 1'b1;//是b不是d,直接over

else //等于50000000的时候,

cnt <= 26'd0; //清零,重新开始计数

end

endmodule//模块结束

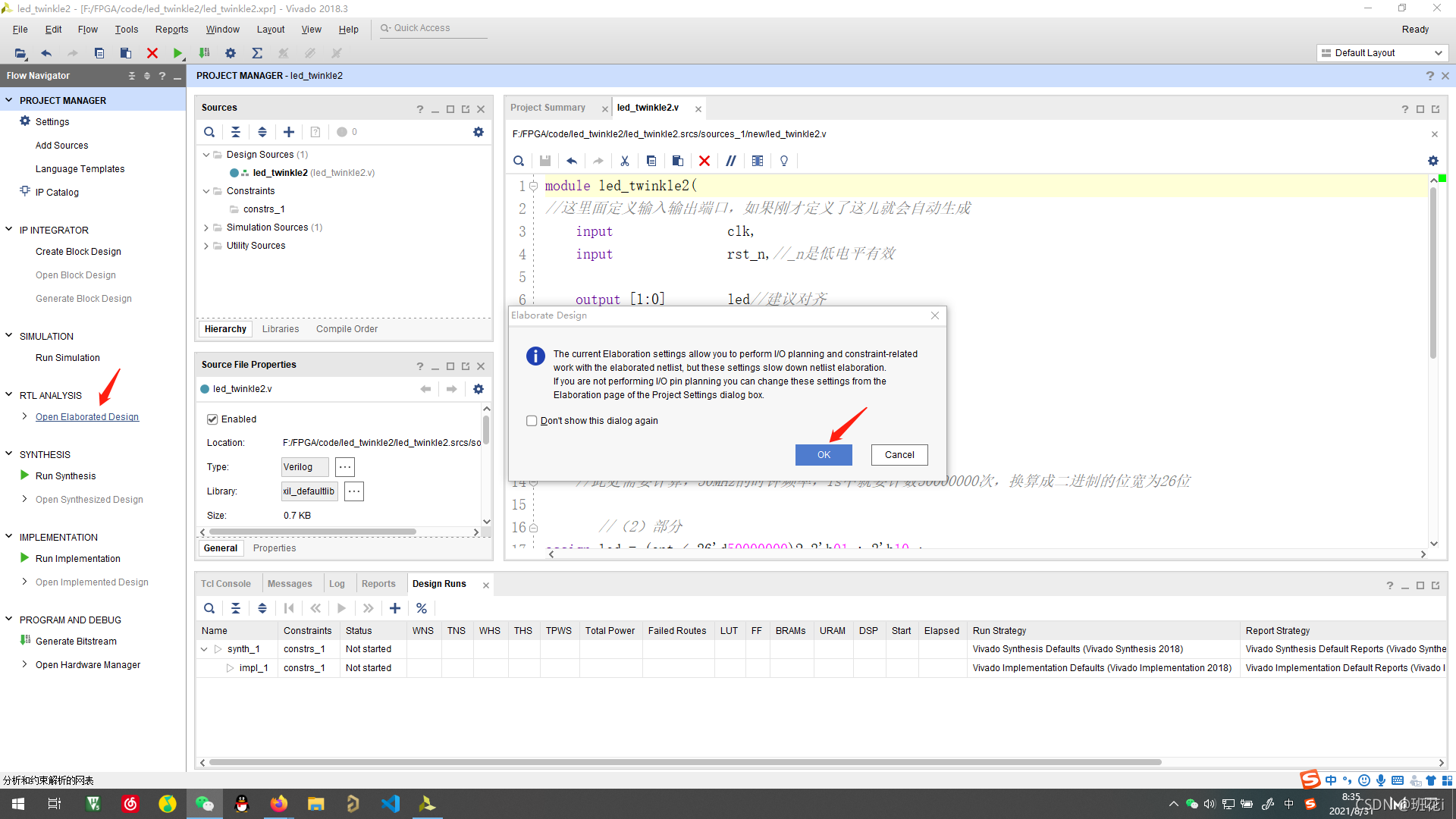

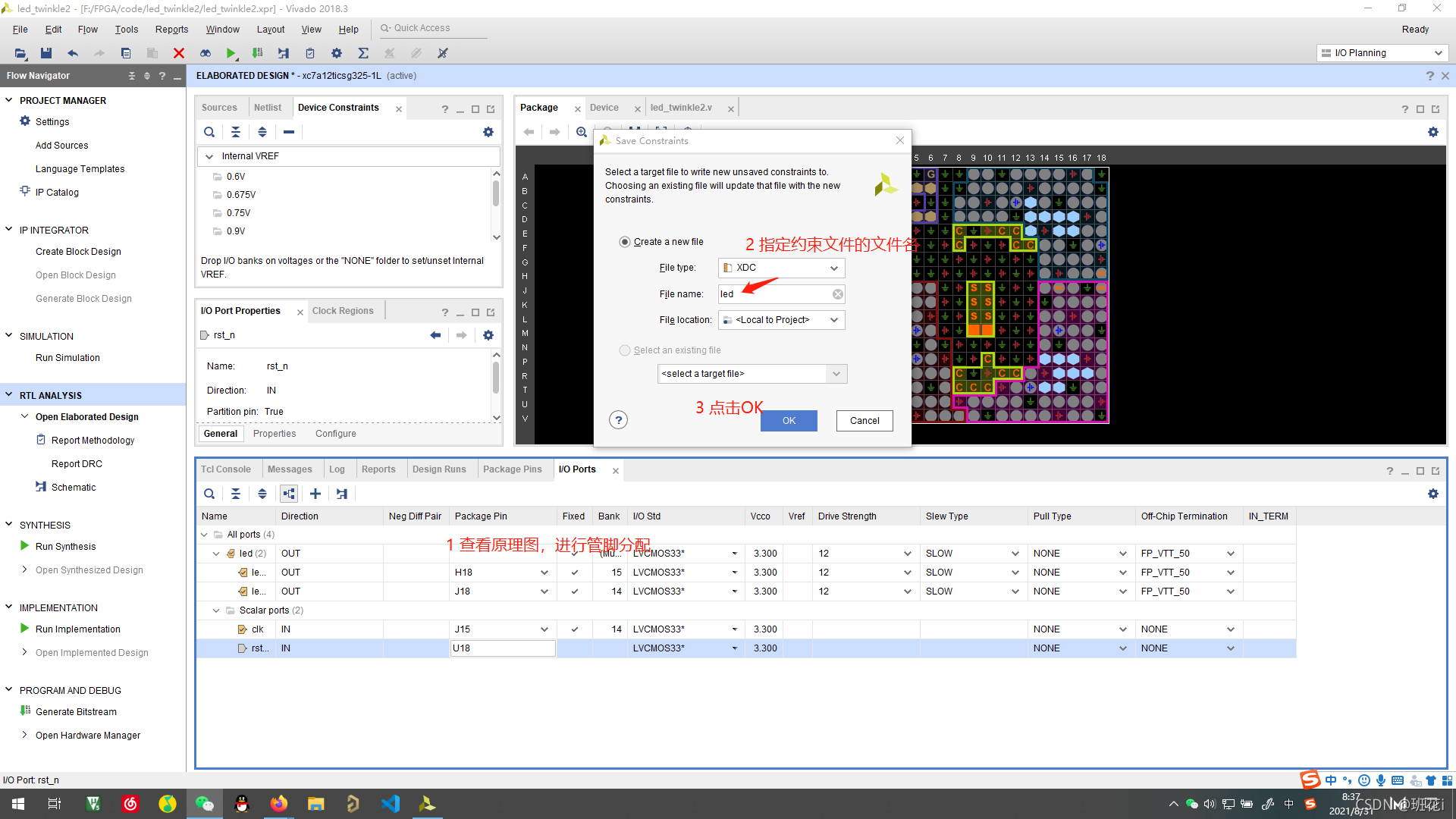

(4) 管脚IO分配(前面跳过了)

然后进行管脚分配(很重要的一个步骤!)

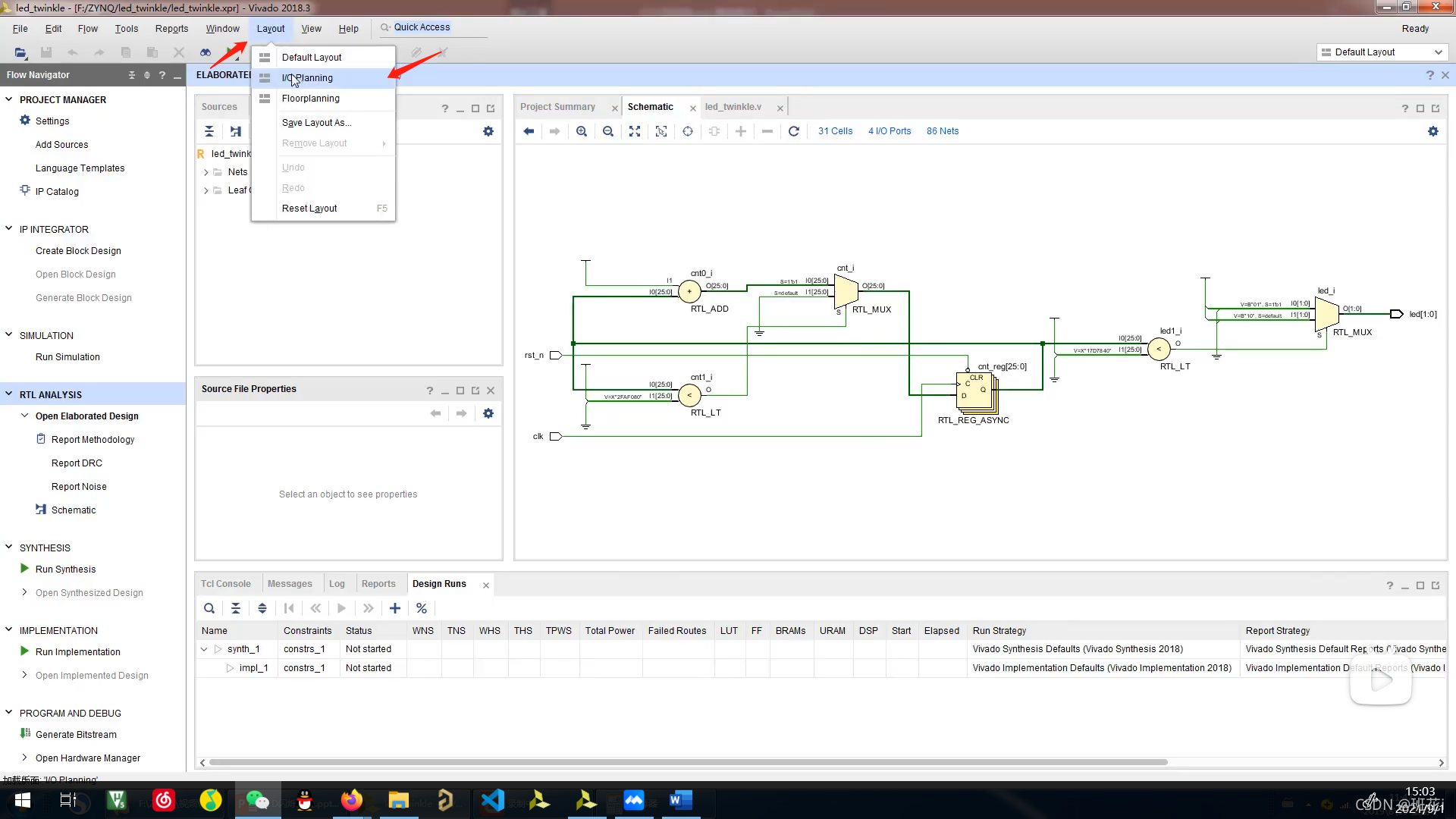

然后,管脚分配的页面需要我们手动去打开!

然后,管脚分配的页面需要我们手动去打开!

layout->IO planning

或者直接右上角(建议!!)

或者直接右上角(建议!!)

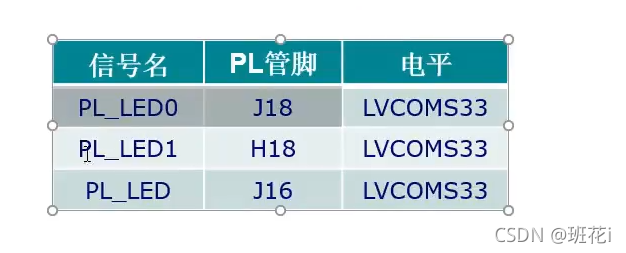

然后按照这个图来配置管脚

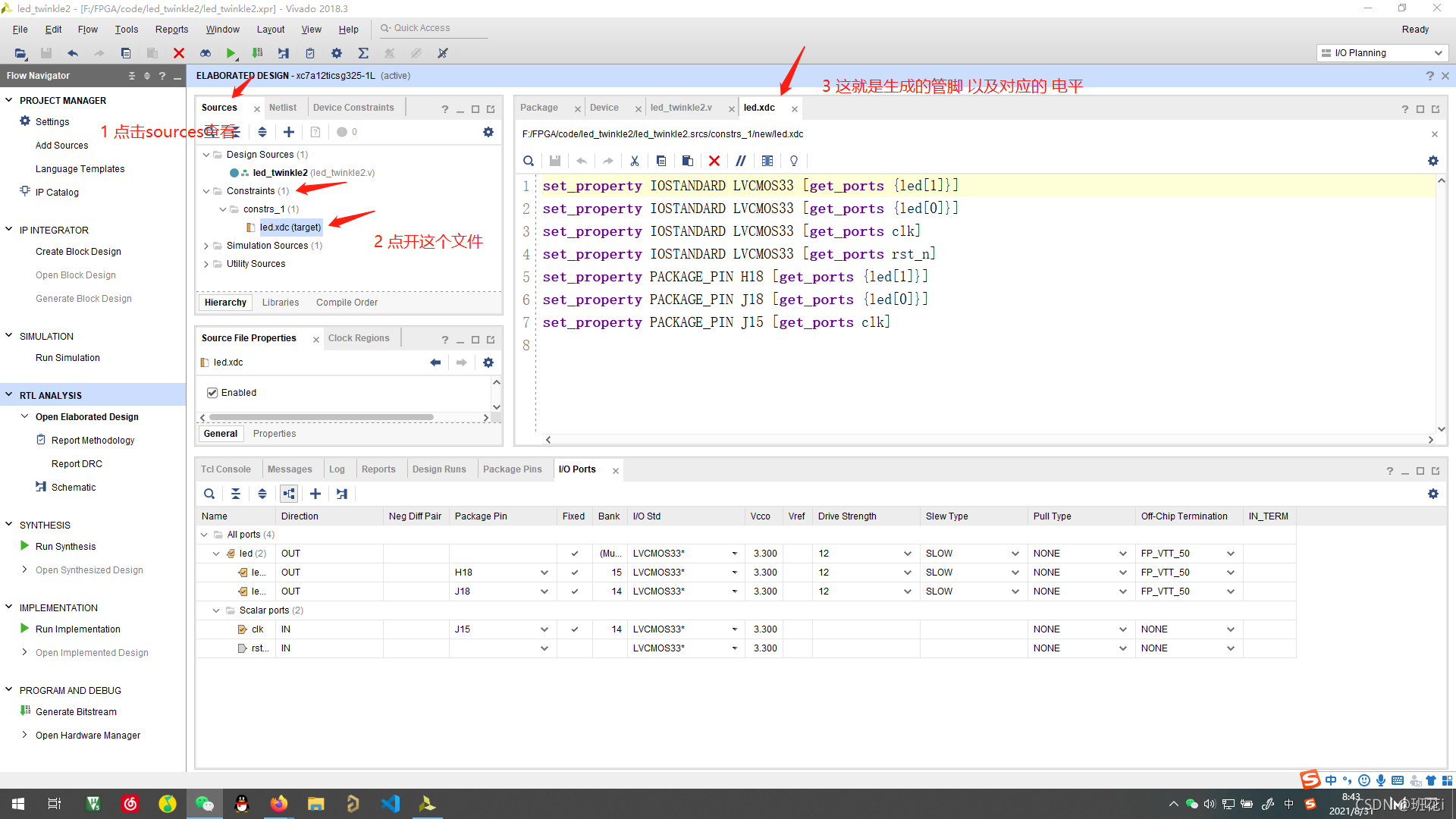

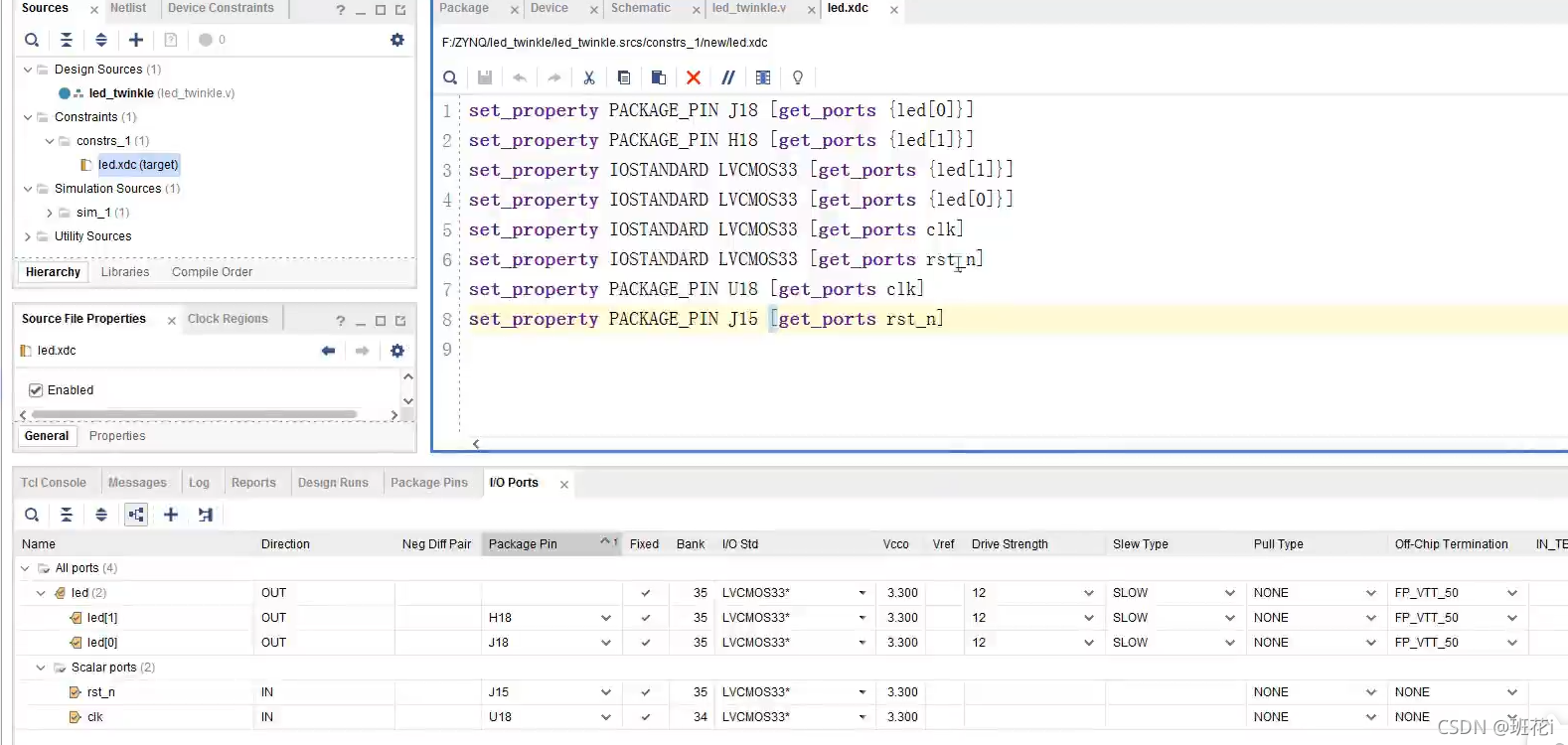

具体内容看下面这个图!上面那个图有点问题!我写在我的BUG里面了

具体内容看下面这个图!上面那个图有点问题!我写在我的BUG里面了

如果对于约束文件里的 管脚分配 不太明白的,可以看看我这个博客

如果对于约束文件里的 管脚分配 不太明白的,可以看看我这个博客

也就是J15 H18的选择

constraints约束文件.

1750

1750

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?