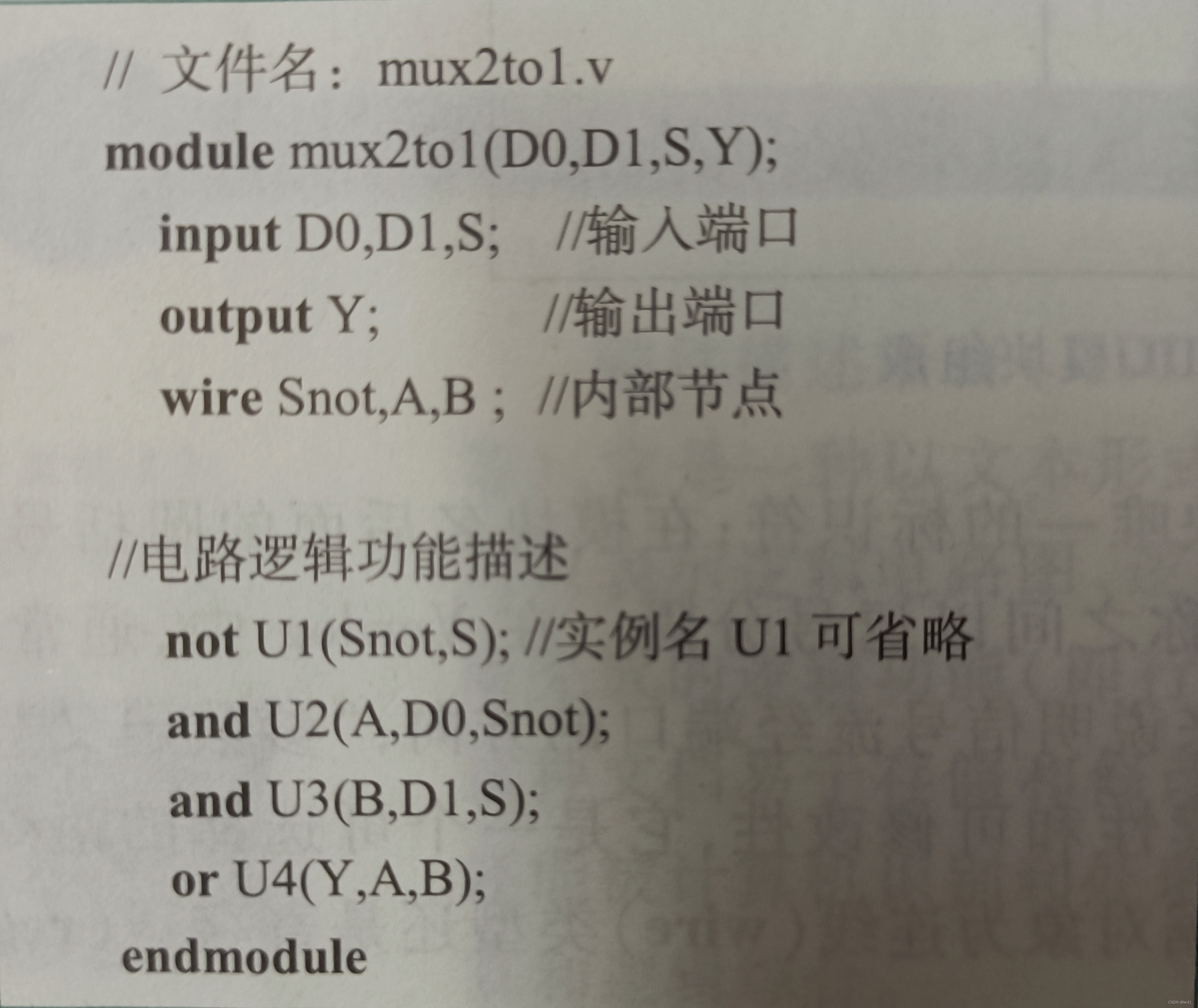

1:门级描述

这两种描述的时候,使用默认的wire即可。这两种描述方式,本质上都是直接使用逻辑门门级描述是显式地使用了门级原语数据流描述其实是隐式地使用门级原语,因为他是直接描述数据在寄存器直接的流动关系,本质上,还是在阐述逻辑门的使用。

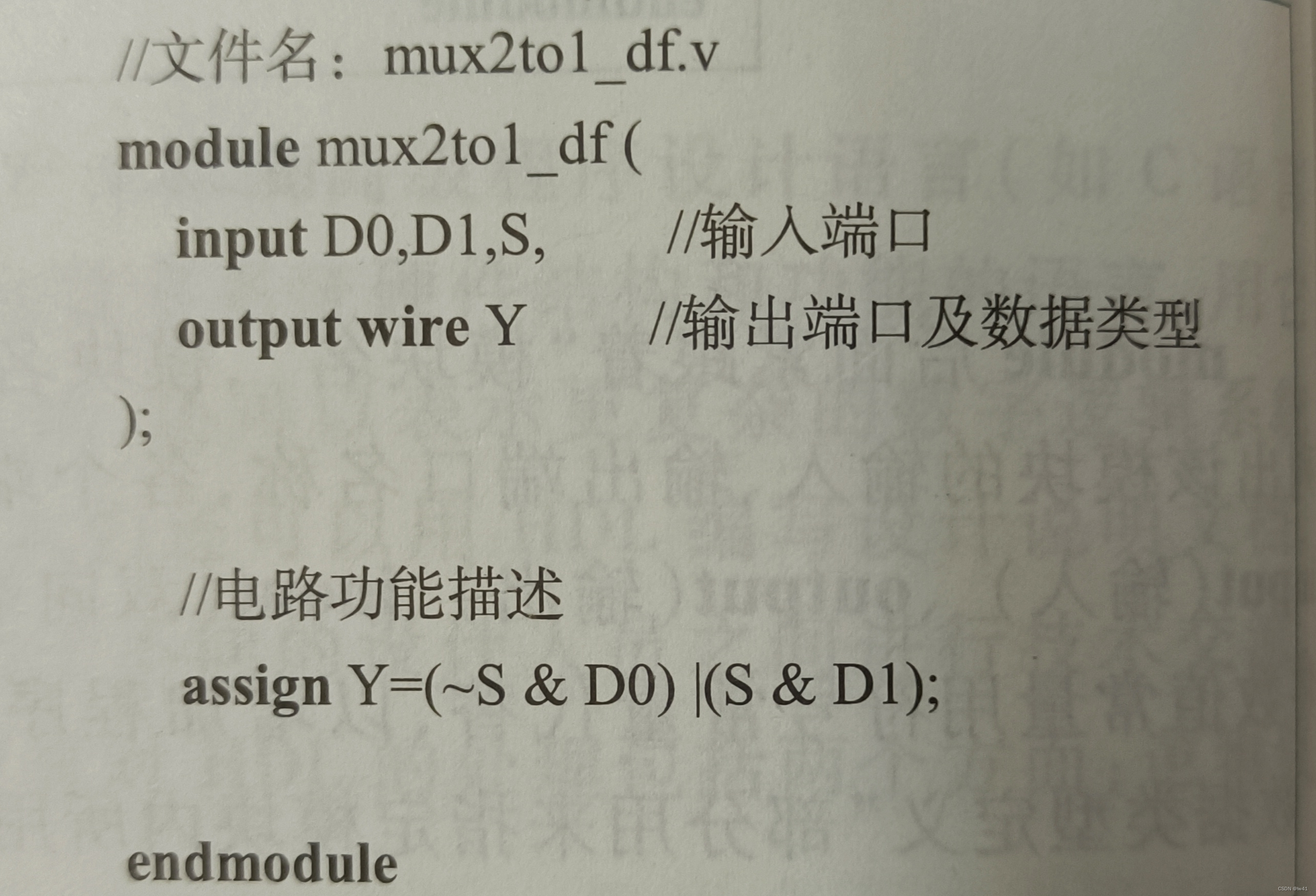

2:数据流描述:

数据流描述是以连续赋值语句为基石的描述方式,其左值必须是线网类型,右值无要求。

下面是逻辑功能的仿真与测试

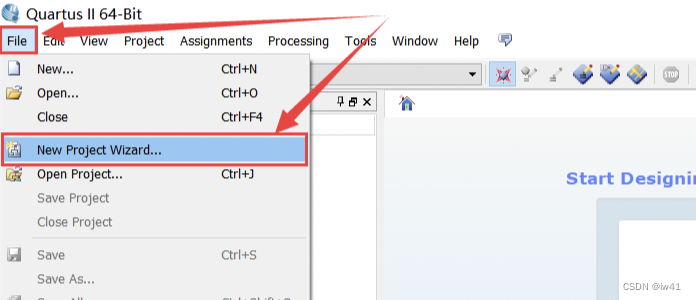

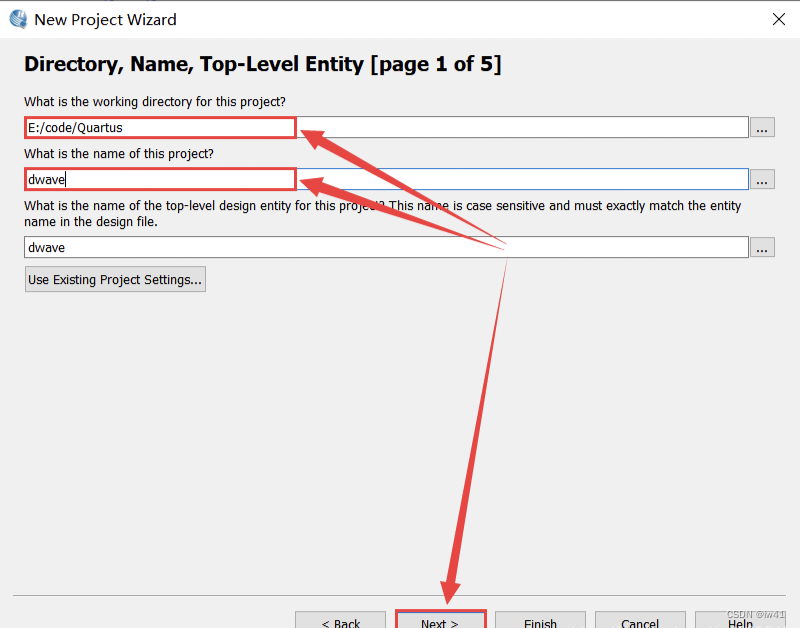

一:建立新项目:

1:【File】→【New Project Wizard

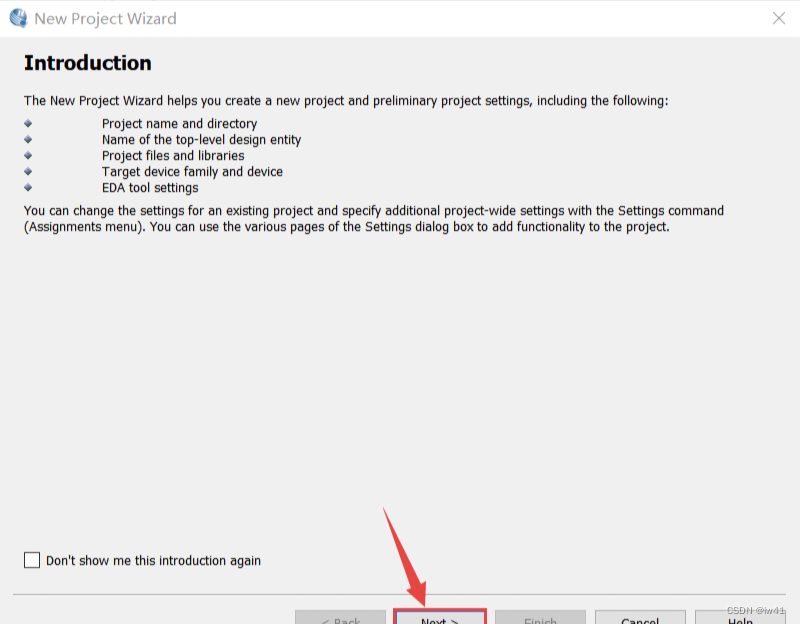

2:点击【Next >

)

3:选择工程保存路径及工程名,然后点击【Next >】。

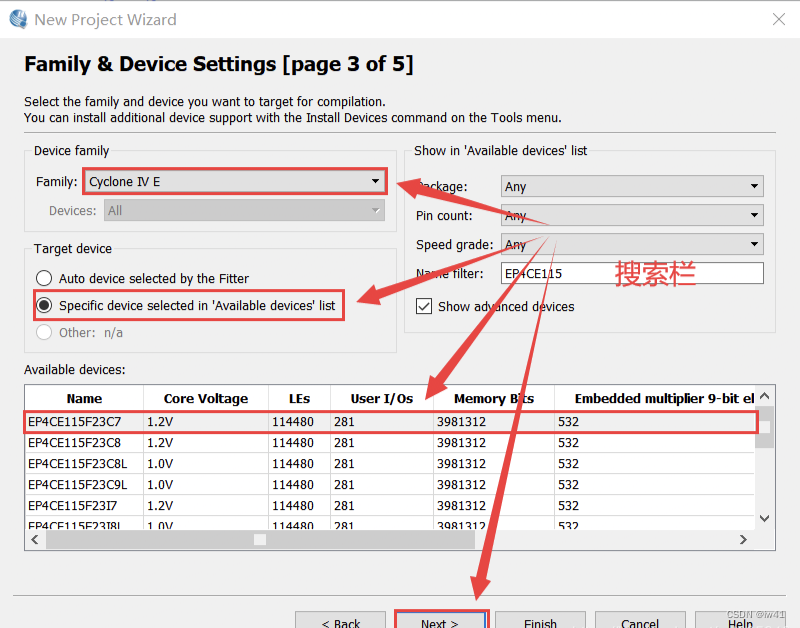

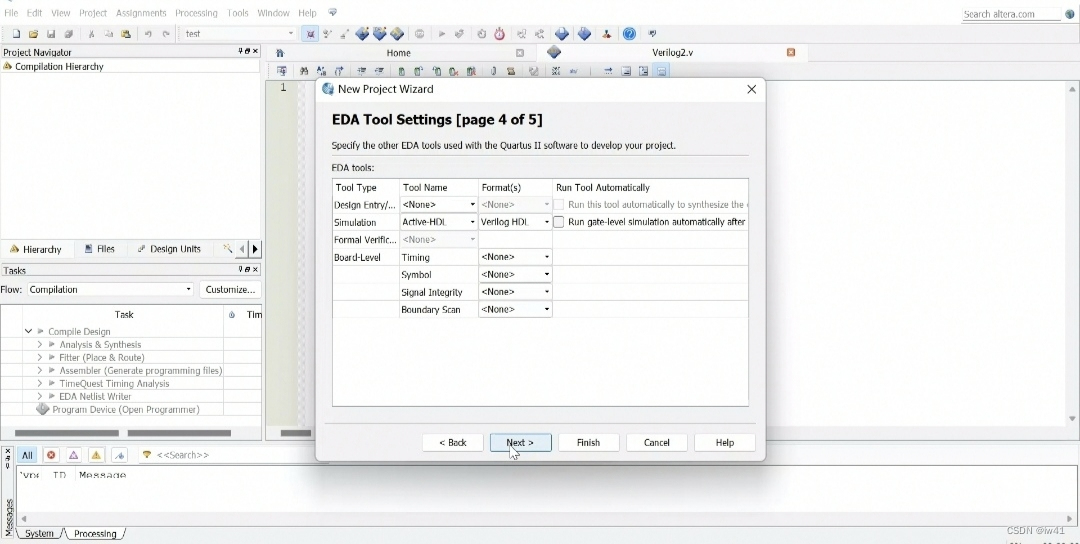

4:根据使用的 FPGA,进行选择芯片系列及类型,然后点击【Next >】。

设置如图后点击确定下一步。

二:全部设置完毕后开始对电路建模。

首先添加行为级描述代码如下

// module mux2_to_1, 选择器的代码,

module mux2_to_1(

IN0 , // input 1

IN1 , // input 2

SEL , // select

OUT ); // out data

parameter WL = 16; // 输入输出数据信号宽

input [WL-1:0] IN0, IN1;// 选择器的两个输入数据信号

input SEL; // 通道选通的控制信号

output[WL-1:0] OUT; // 选择器的输出数信号

reg [WL-1:0] OUT;

// 生成组合逻辑的代码

always @ (IN0 or IN1 or SEL) begin

if(SEL) // SEL为1 选择输入1

OUT = IN1;

else // SEL为0 选择输入0

OUT = IN0;

end

endmodule

// endmodule mux2_to_1

##最后输入完成后对代码进行调试。

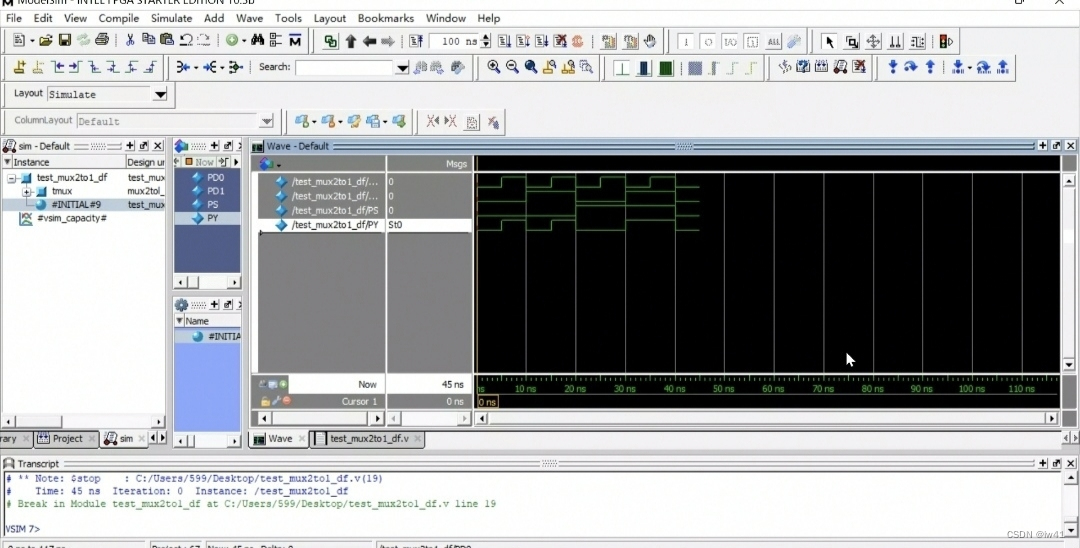

三:最后激励信号后添加完激励信号后选择“Processing”—“SimulatorTool”在“Simulation mode”中选择“Functional”再点击“Generate Functional Simulation Netl ist”。然后选择“Overwrite simulationinputfi le with simulation result”点击“Start”开始仿真。

四:最后得到的实验结果

在0~20ns期间,由于PS=0,所以输出PY与PD0相同,在20~40ns期间,PS=1,故输出PY与PD1相同。

5073

5073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?