题目

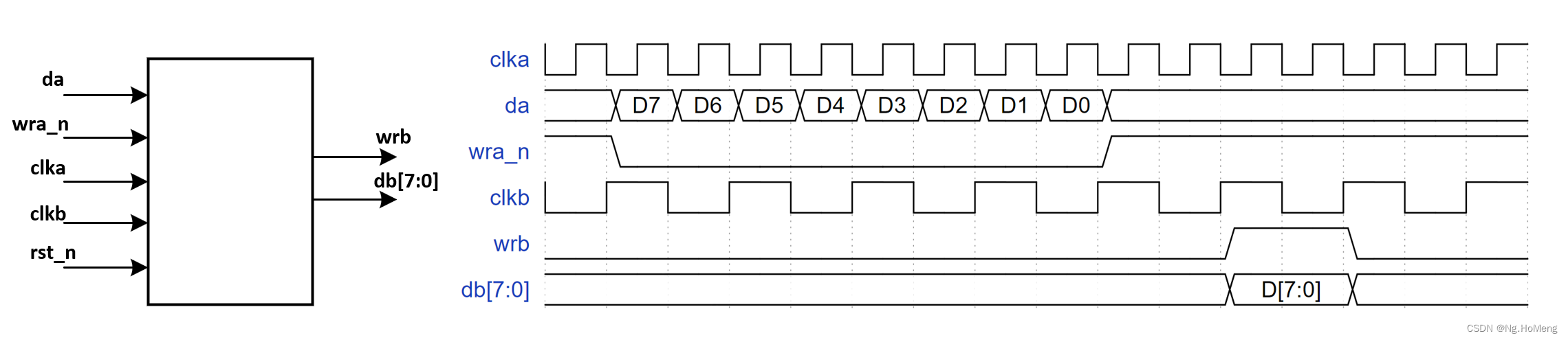

请用verilog设计一个接口转换电路,接口timing如下图所示,假设clka频率为clkb频率的一半(不同源。注意图中clock关系仅为示意),且两次有效访问(wra_n有效)的间隔时间足够长。

模块代码

module Interface_Conversion(

// System Signal

input rst_n ,

// Clka

input clka ,

input da ,

input wra_n ,

// Clkb

input clkb ,

output wrb ,

output [7:0] db

);

//=============================================

// DECLARATION

//=============================================

// Reset Signals

reg rst_n_f ;

reg rst_sys_n;

// Clka Domain

reg [7:0] da_temp ;

reg [2:0] cnt_clka ;

// Clkb Domain

reg wra_n_ff1 ;

reg wra_n_ff2 ;

reg wra_n_ff3 ;

wire wrb ;

wire [7:0] db ;

//=============================================

// MAIN CODE

//=============================================

// Reset Signal Operation

always @(posedge clkb or negedge rst_n) begin

if (!rst_n) begin

rst_n_f <= 1'b0;

rst_sys_n <= 1'b0;

end

else begin

rst_n_f <= rst_n ;

rst_sys_n <= rst_n_f;

end

end

// Clka Domain

always @(posedge clka or negedge rst_sys_n) begin

if (!rst_sys_n) begin

da_temp <= 8'd0;

cnt_clka <= 3'd7;

end

else if (!wra_n) begin

da_temp <= {da_temp[6:0], da};

cnt_clka <= cnt_clka - 3'd1 ;

end

else

cnt_clka <= 3'd7;

end

// Clkb Domain

always @(posedge clkb or negedge rst_sys_n) begin

if (!rst_sys_n) begin

wra_n_ff1 <= 1'b0;

wra_n_ff2 <= 1'b0;

wra_n_ff3 <= 1'b0;

end

else begin

wra_n_ff1 <= wra_n ;

wra_n_ff2 <= wra_n_ff1 ;

wra_n_ff3 <= wra_n_ff2 ;

end

end

assign wrb = (wra_n_ff2 && ~wra_n_ff3)? 1'b1: 1'b0;

assign db = (wrb)? da_temp: 8'd0;

endmoduleTestBench代码

module tb_Interface_Conversion;

//==========================================================

// DEFINE INPUT

//==========================================================

reg clk_20M ;

reg clk_10M ;

reg rst_n ;

reg [0:0] da ;

reg wra_n ;

//==========================================================

// DEFINE OUTPUT

//==========================================================

wire [7:0] db ;

//==========================================================

// INSTANCE MODULE

//==========================================================

Interface_Conversion U_Interface_Conversion(

// System Signal

.rst_n (rst_n) ,

// Clka

.clka (clk_20M) ,

.da (da) ,

.wra_n (wra_n) ,

// Clkb

.clkb (clk_10M) ,

.wrb (wrb) ,

.db (db)

);

//==========================================================

// TESTBENCH CODE

//==========================================================

// Clock Generation

always #25 clk_20M = ~clk_20M;

always #50 clk_10M = ~clk_10M;

// Input Signal Generation

initial begin

clk_20M = 1'b0;

clk_10M = 1'b0;

rst_n = 1'b0;

da = 1'b0;

wra_n = 1'b1;

#100 rst_n = 1'b1;

#200 begin

da = 1'b0;

wra_n = 1'b0;

end

#50 da = 1'b0;

#50 da = 1'b1;

#50 da = 1'b1;

#50 da = 1'b0;

#50 da = 1'b0;

#50 da = 1'b1;

#50 da = 1'b0;

#50 wra_n = 1'b1;

end

endmodule

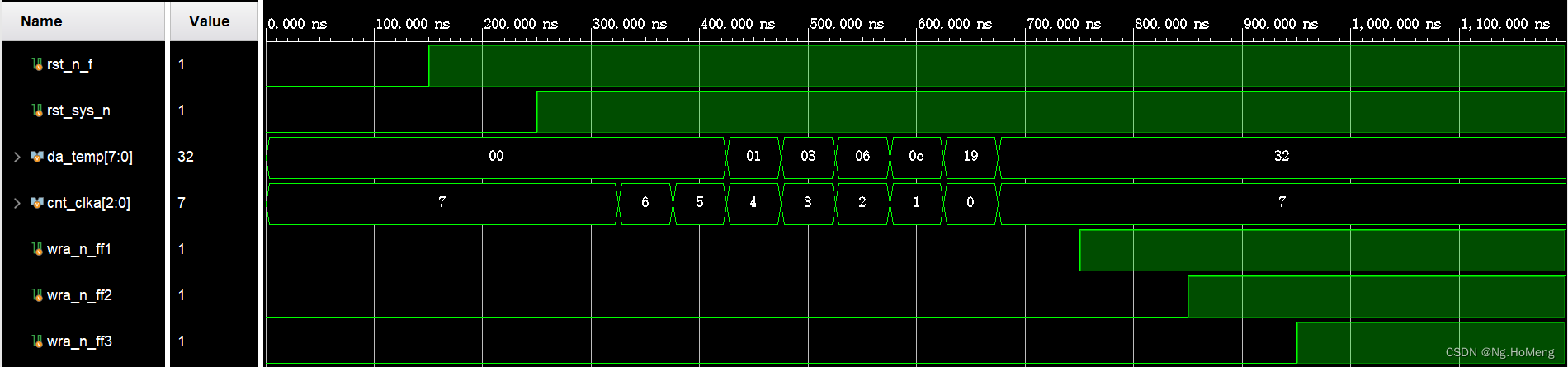

测试波形图

模块主要信号(输入输出接口信号):

模块内部处理信号:

答案仅供参考,如有错误欢迎留言指正~

1118

1118

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?