题目

使用FSM实现一个仲裁器电路,该电路控制三个请求设备对某种类型资源的共享访问。每个设备通过设置信号r[i]=1来请求资源,其中i = 0, 1, 2,每个r[1]是FSM的输入信号,代表三个设备之一。只要没有请求,FSM就会保持状态IDLE。当发生一个或多个请求时,FSM决定哪个设备接收到使用该资源的授权,并更改为将该设备的g[i]信号设置为1的状态。每个g[i]是FSM的输出。有一个优先级系统,设备0的优先级>设备1的优先级>设备2的优先级,当有多个请求同时发出的时候,优先级最高的获得仲裁权。一旦设备(即FSM给了设备i)授权,只要它的请求r[i] = 1,则该设备将继续接收授权直到它的请求拉低。画出状态图,使用三段式写法设计代码。(需要考虑达到仲裁器最高效率)

module top_module(

input clk,

input resetn, // active-low asynchronous reset,

input [2:0] r, // request, synchronized to clk posedge

output [2:0] g, // grant

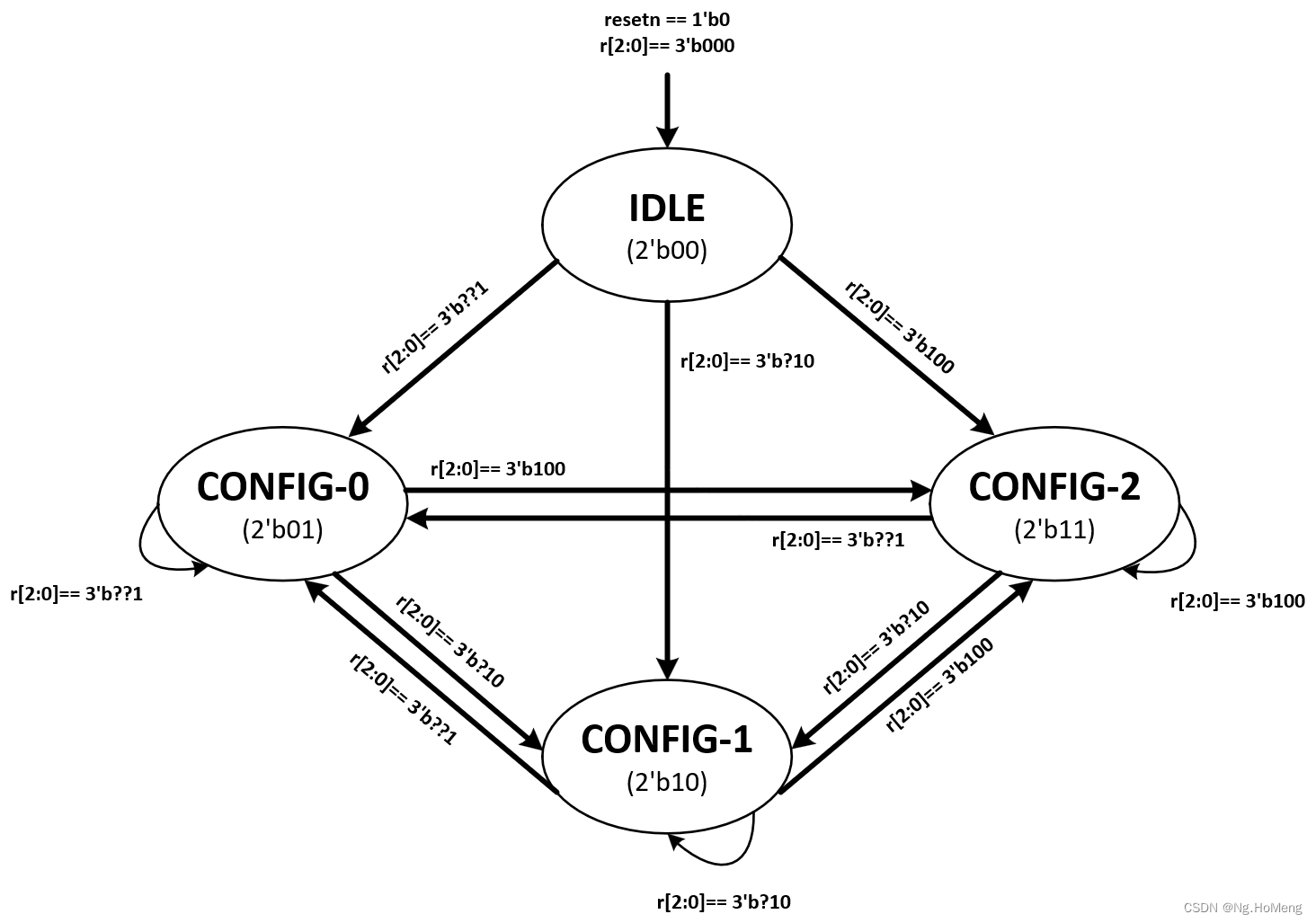

状态图

模块代码

module ARB_MASTER(

// INPUT

input clk ,

input resetn , // active-low asynchronous reset

input [2:0] r , // request, synchronized to clk posedge

// OUTPUT

output reg [2:0] g // grant

);

//===============================================

// DEFINE PARAMETER

//===============================================

parameter IDLE = 2'b00;

parameter CONFIG_0 = 2'b01;

parameter CONFIG_1 = 2'b10;

parameter CONFIG_2 = 2'b11;

//===============================================

// DEFINE REG , WIRE

//===============================================

reg [1:0] st_cur;

reg [1:0] st_next;

//===============================================

// MAIN CODE

//===============================================

//1st Para

always @(posedge clk or negedge resetn) begin

if (!resetn)

st_cur <= 2'b00;

else

st_cur <= st_next;

end

//2nd Para

always @(r)

casex(r)

3'b000: st_next = IDLE;

3'b??1: st_next = CONFIG_0;

3'b?10: st_next = CONFIG_1;

3'b100: st_next = CONFIG_2;

default: st_next = IDLE;

endcase

//3rd Para

always @(posedge clk or negedge resetn) begin

if (!resetn)

g <= 3'b000;

else if (st_next == CONFIG_0)

g <= 3'b001;

else if (st_next == CONFIG_1)

g <= 3'b010;

else if (st_next == CONFIG_2)

g <= 3'b100;

else

g <= 3'b000;

end

endmoduleTestBench代码

`timescale 1ns / 1ps

module tb;

//=============================

// DEFINE INPUT

//=============================

reg clk;

reg resetn;

reg [2:0] r;

//=============================

// DEFINE OUTPUT

//=============================

wire [2:0] g;

//=============================

// INSTANCE MODULE

//=============================

ARB_MASTER U_ARB_MASTER(

// INPUT

.clk (clk) ,

.resetn (resetn), // active-low asynchronous reset

.r (r) , // request, synchronized to clk posedge

// OUTPUT

.g (g) // grant

);

//=============================

// TESTBENCH CODE

//=============================

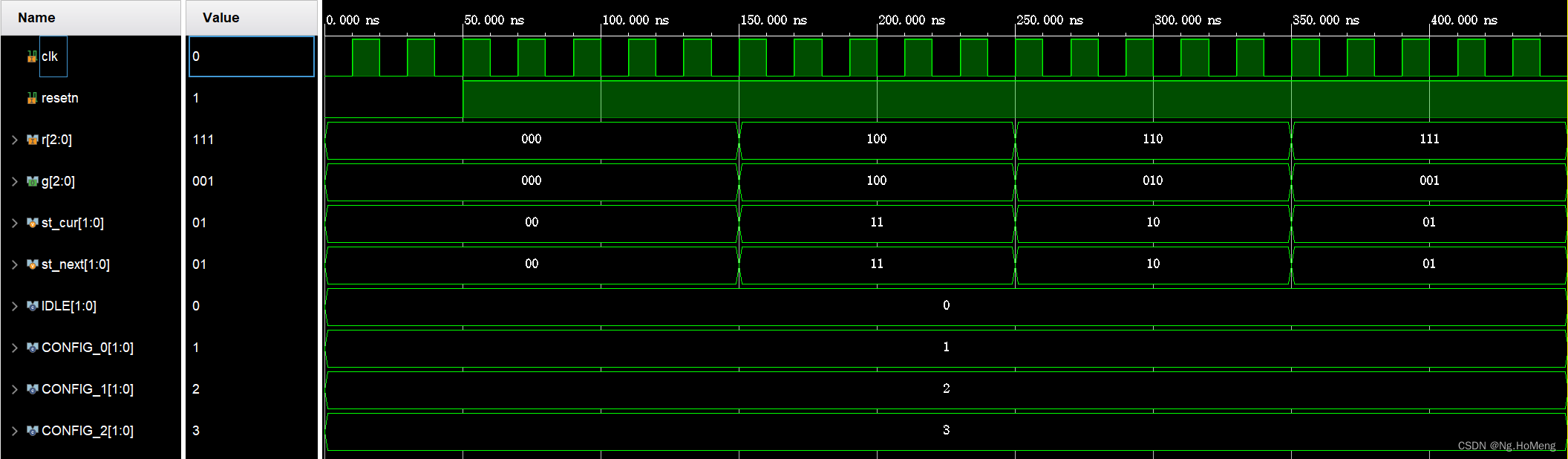

always #10 clk = ~clk;

initial begin

clk = 0;

resetn = 0;

#50 resetn = 1;

#50 r = 3'b000;

#100 r = 3'b100;

#100 r = 3'b110;

#100 r = 3'b111;

#100 $stop;

end

endmodule测试波形图

答案仅供参考,如有错误欢迎评论指正~

6556

6556

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?