说明:华科大四课程《功率集成电路》作业论文复现 可能有错误

参考文献:. M. Tan, C. Zhan, and W.-H. Ki, “A 4uA quiescent current output-capacitor-free low-dropout regulator with fully differential input stage,” in IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, pp. 2457-2460, Jun. 2014

写这篇文章的意义就是总结一下复现过程遇到的困难以及所学到的新的体会,如有错误还请指正。

目录

一、结果展示

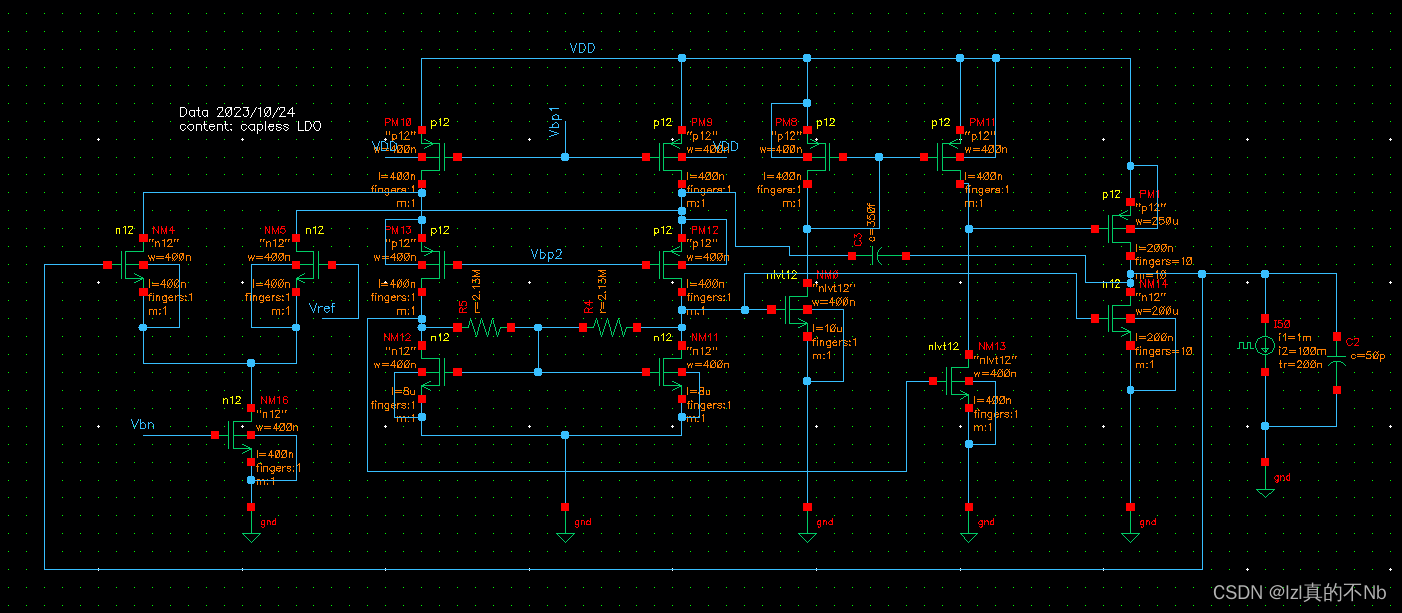

(1)顶层设计

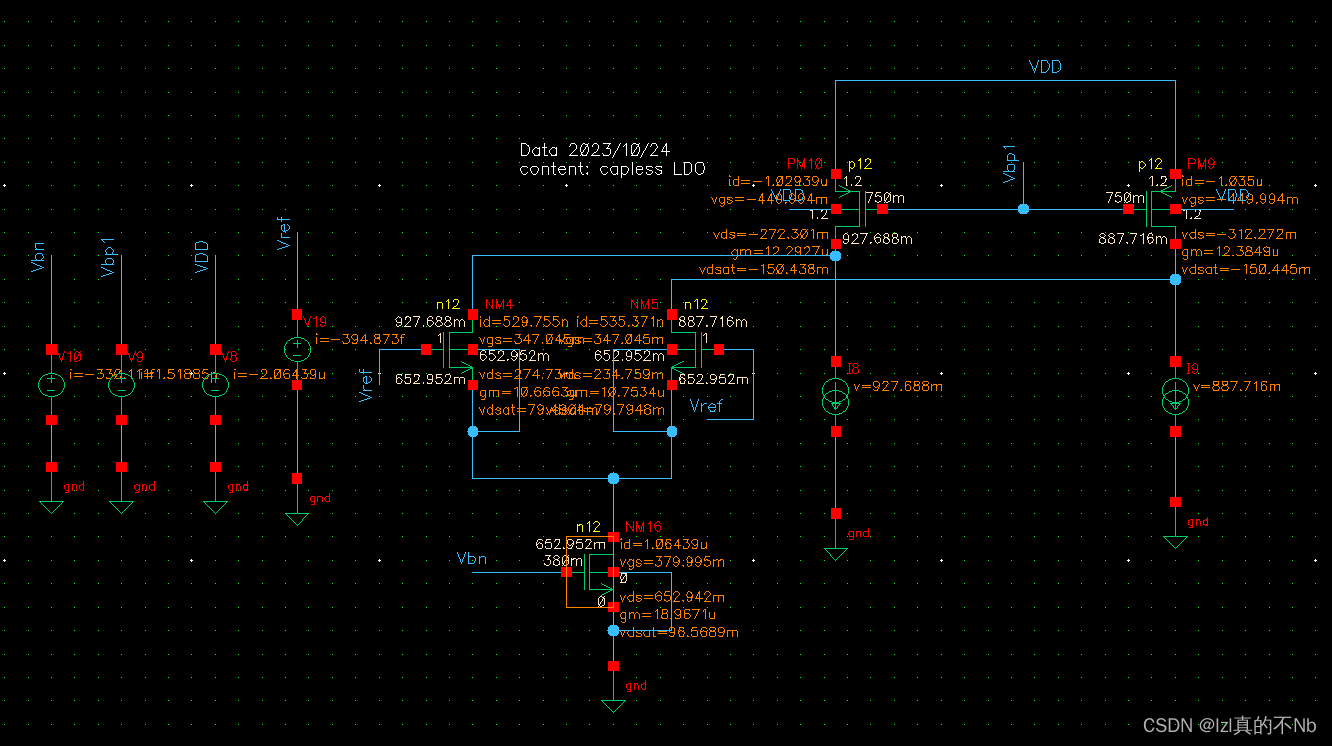

(2)偏压设计

工艺:SMIC.13 工艺角:tt

| 名称 | 电压 | 备注 |

|---|---|---|

| VDD | 1.2V | 可调 |

| Vo | 1V | 0.5V~1V 可调 |

| Vbp1 | 750mV | 偏置电压 |

| Vbp2 | 400mV | 偏置电压 |

| Vbn1 | 380mV | 可用电流镜镜像 |

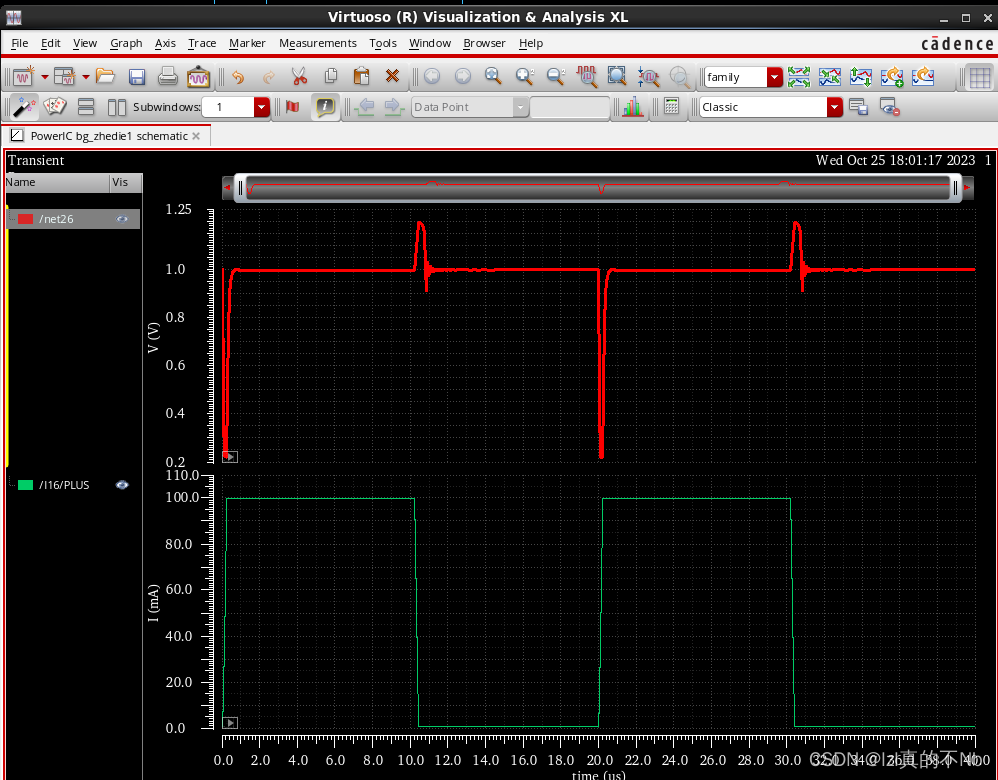

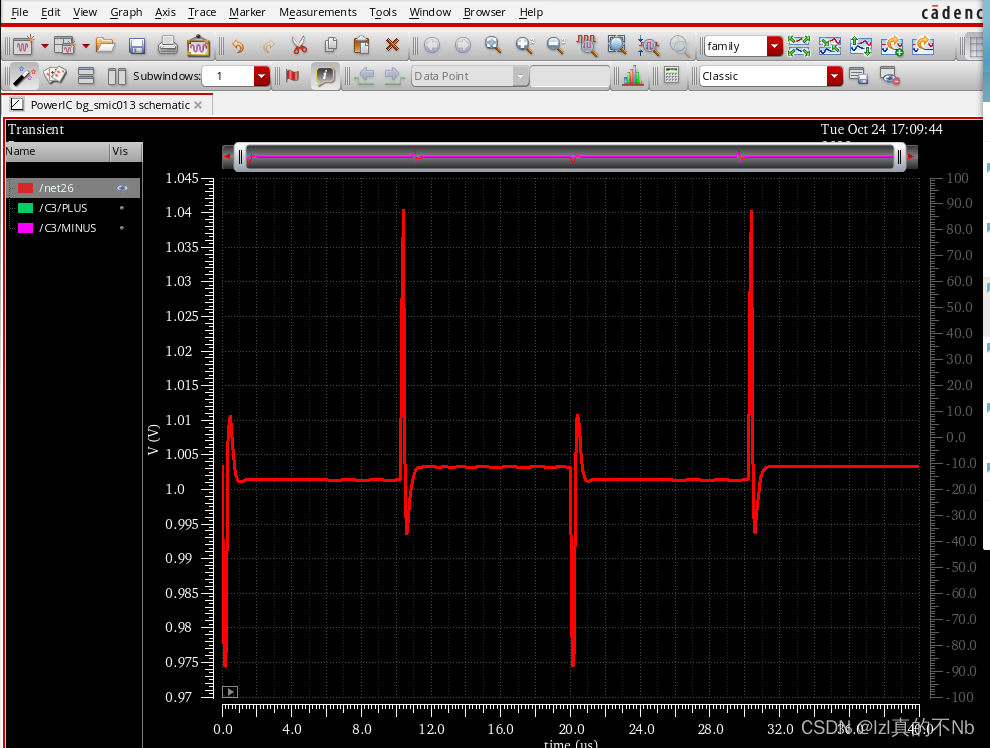

(3)输出瞬态

上升时间与下降时间:200ns

输出电流:1mA~100mA波动 周期20us 占空比:50%

PS:紫色为输出端电流跳变 红色为驱动功率PMOS的栅极电压变化 绿色为输出Vo

PS:紫色为输出端电流跳变 红色为驱动功率PMOS的栅极电压变化 绿色为输出Vo

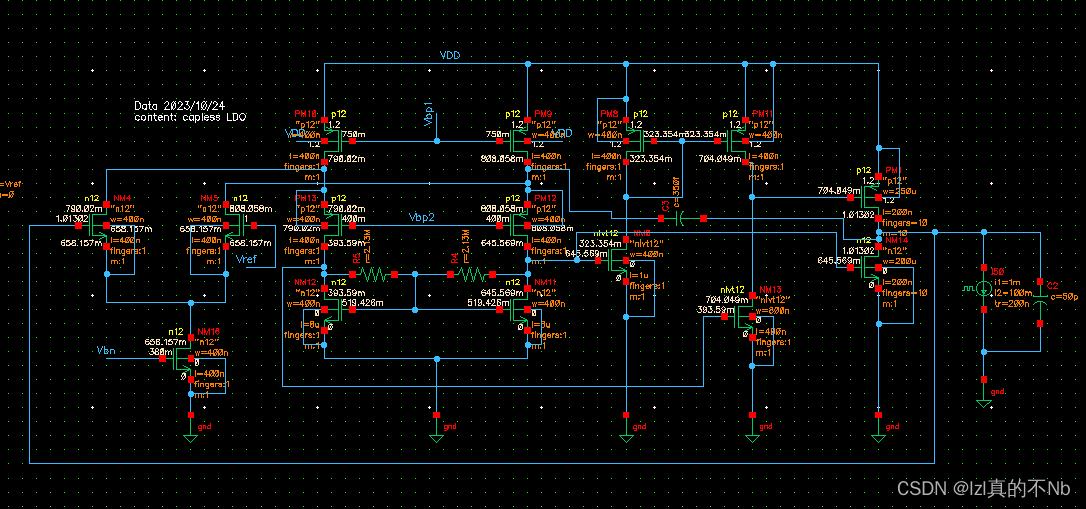

(4) DC工作点与反馈电压

PS:n12lvt是低阈值MOS管

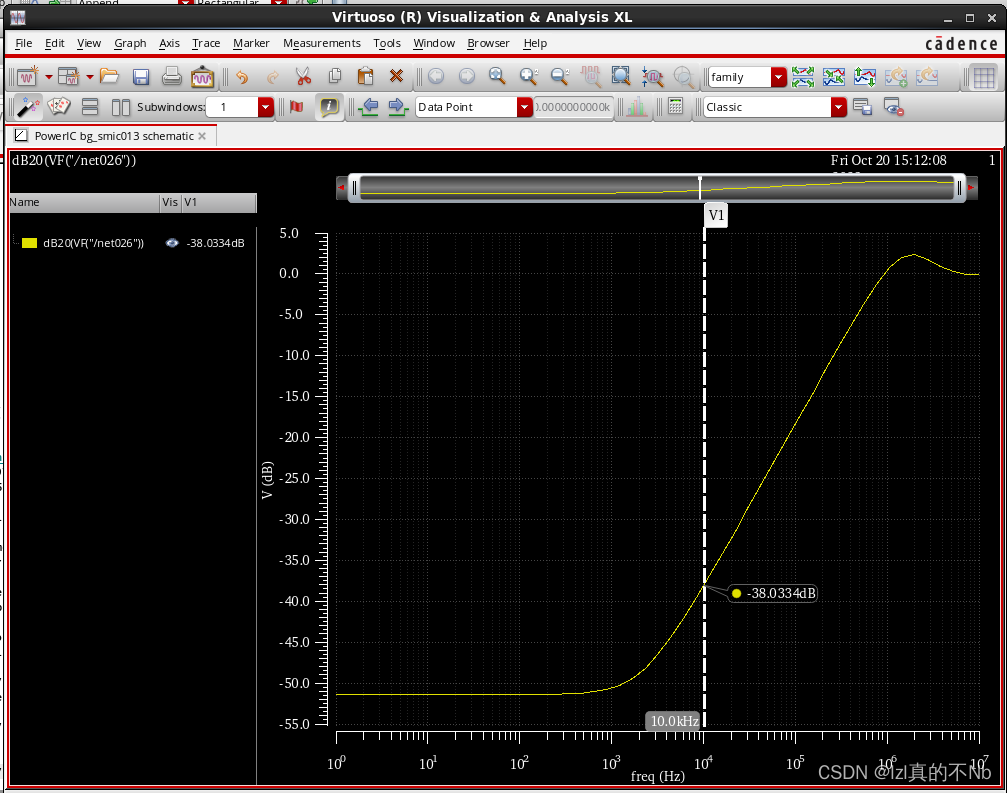

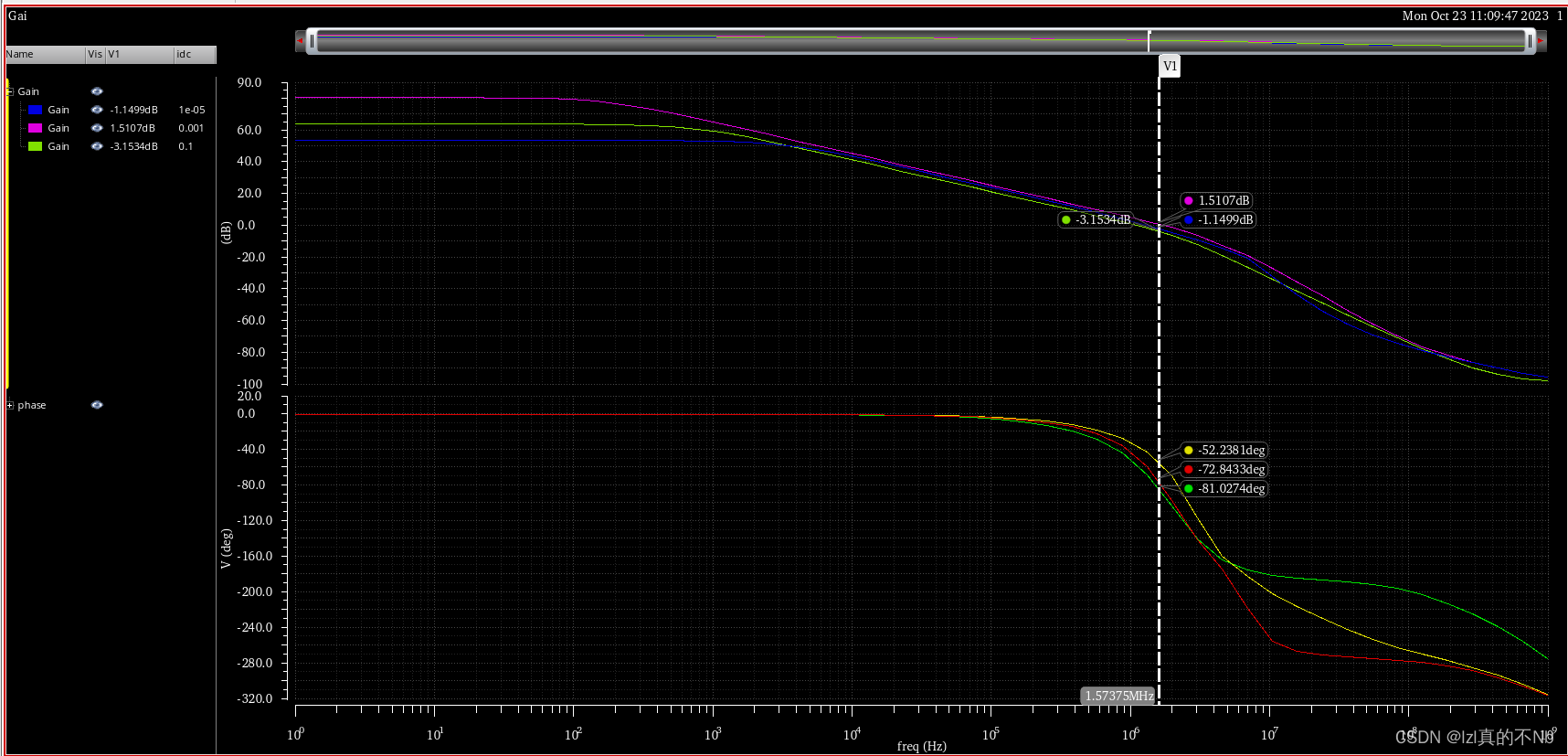

(5)PSRR与相位曲线:

图:电源电压抑制比PSRR+

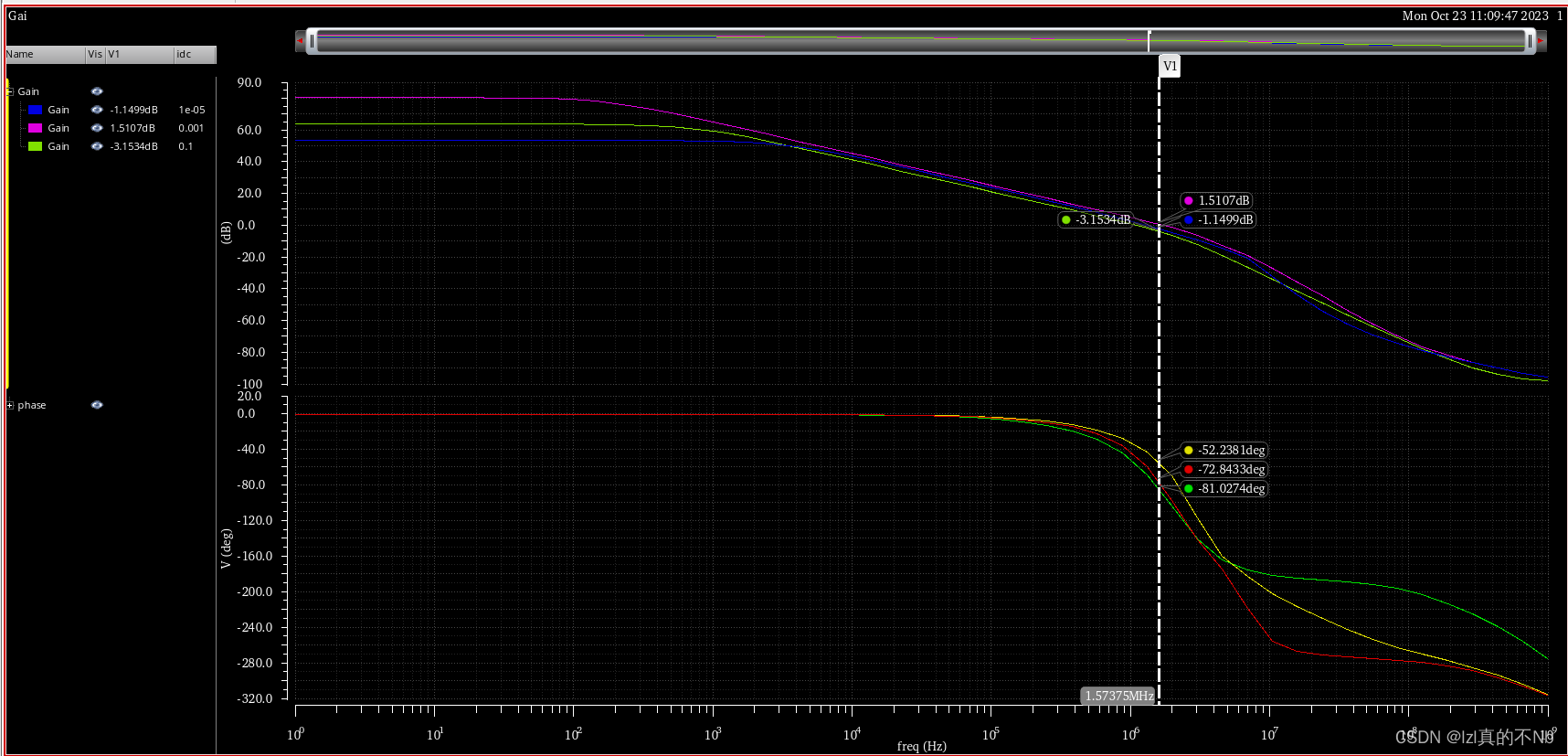

图:10uA - 100mA负载电流下的相位裕度

二、论文学习与分析

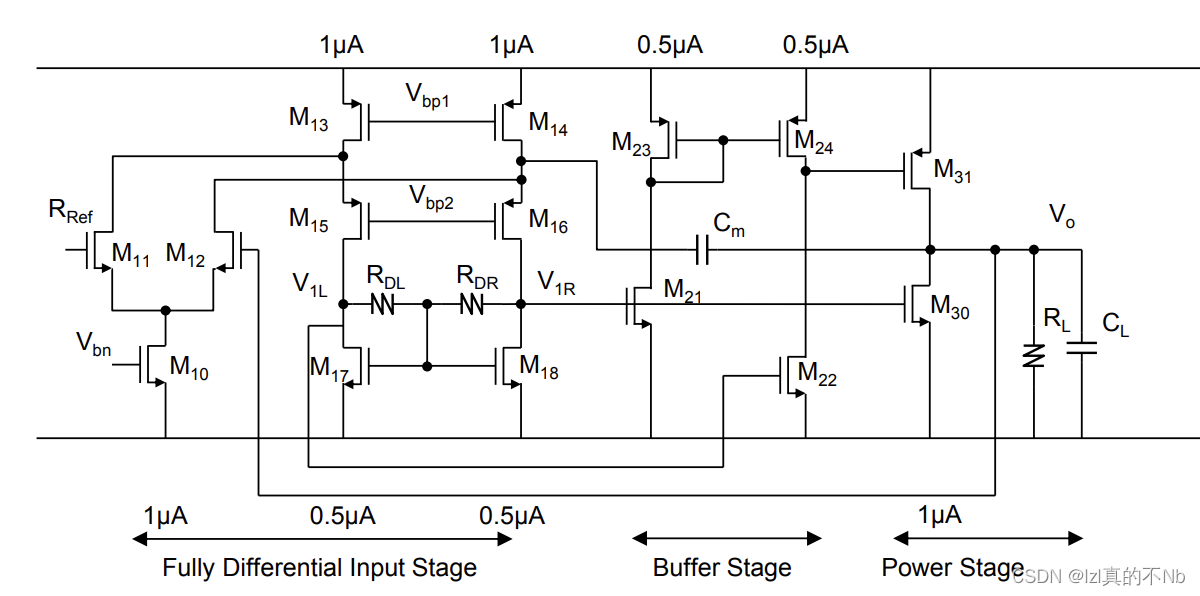

(1)论文主体结构:

(2)全差分输入级分析:

第一级采用了全差分的折叠式Cascode放大器,并且嵌套了miller补偿。

这种miller补偿我们一般称为cascode Miller补偿,他在切断前馈的同时有利于增益的提高。

采样电阻:

对于DC分析来说,由于RDL和RDR连接的是两个栅极,没有电流流过,也就是说M17和M18是二极管式连接,作用就是采样Vd用以下级的电流差分。同时,RDL和RDR可以进行共模反馈用以稳定第一级输出的直流工作点。

(3)BUFFER级分析

Buffer级是一个电流镜结构,主要作用是用以替换传统的源极跟随器的BUFFER结构用来完成极点分裂补偿相位。值得一提的是:这个电流镜是非反向结构。

(4)Power级分析

Power级分析最主要的就是M30的作用,本文没有采用经典的双电阻采样。经过本人对老师(即原作者)的询问,可以不经采样电阻采样,直接反馈令β=1也是可以的。

M22作用:M22本质上是构成一个快速前馈通路,利用他的gm用以进行相位补偿,(降低Q值,降低复杂极点峰值)。当然也有文章说M22构成了弱推挽结构,加大了电流的输出有利于瞬态。

(5)瞬态电流突变影响:

负载端发生很大的瞬态电流突变的时候,Pmos的Vd端要快速下降(电容提供电流导致电压下降)用以增大Id,反馈回第一级输出使得Vgs快速下降,容易将偏置管压入线性区。从而影响主电路的电流分配进而影响第二级BUFFER级的输入电压。

三、误差放大器设计:

既然文章中已经给出了静态电流,我们这直接上手设计静态电流便好了。

同时先分配Vds,从Vds从上往下分别为 400mV 300mV 500mV

400mV:保留0.8V的余量,防止反馈的时候(或电流突变)因为过大的Vd变化导致偏置管进入线性区进而影响主电路的电压。

(1)电流的设计

<1>仿真单管饱和区PMOS,大概知道Vth是多少。

<2>确定Vgs,我一般习惯Vg比Vth大0.1~0.2,同时引入Idc源模拟支路电流500nA情况。

<3>套筒结构经过计算留有大概0.8V的Vd,主要利用Vgs和W/L先调偏置管的Id=1uA,注意文章中的反馈稳定是1V,负载NMOS管的输入端都要保证1V。先确定偏置管W/L后,满慢利用W/L来调节电流。

<4>调节Vd,可以利用增大W/L来降低Vd或者反之,Vd不用调的太精准,800mV±150mV就行了。

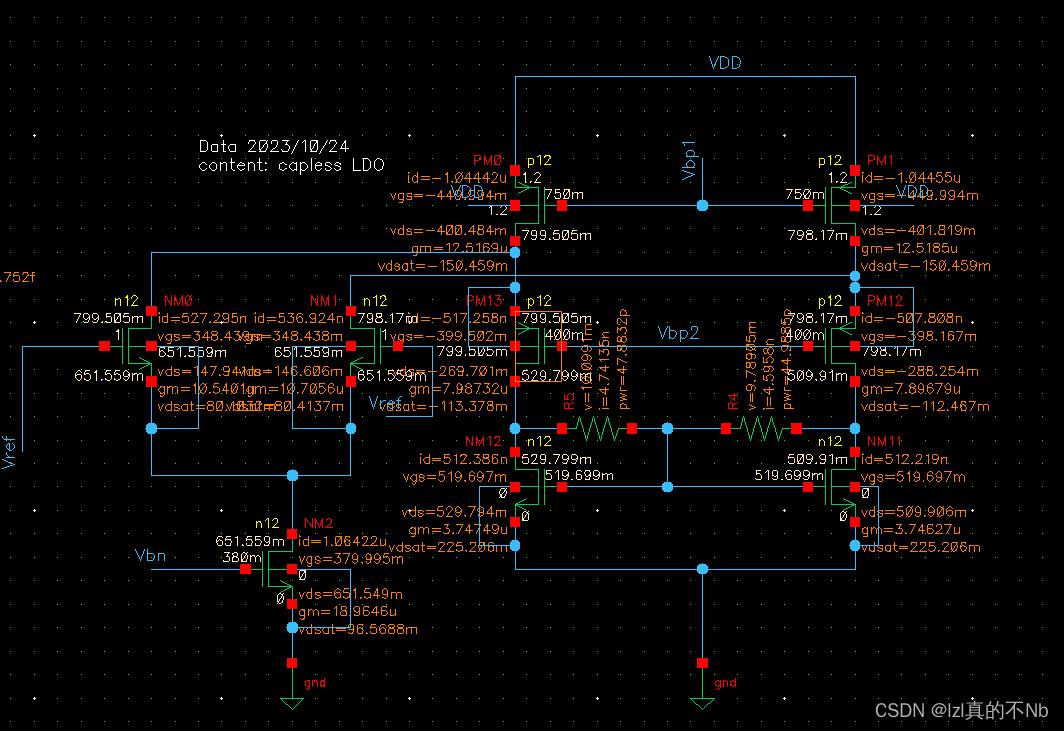

(2)主放大结构负载Casecode NMOS管设计。

<1>首先要明确,最底下的两个NMOS是二极管连接,要让Vd大的话只有一种方法,减小W/L(电流恒定下)。

<2>我们假设Vd PM0 = 800mV的情况下,先确定Vbp2的偏压。此时NM12和NM13可以先让W/L=1 让他去分最小的Vds,后面我们再调节。(假定忽略沟长调制效应,Vds不影响Id,那NM11和NM12的Vd变化,从而影响PM12和PM12的Vd变化,而Vs不变。因为Vds对于Id没有影响,你Vd变就变呗,PM12和PM13的W/L和Vov不变电流就不变。)

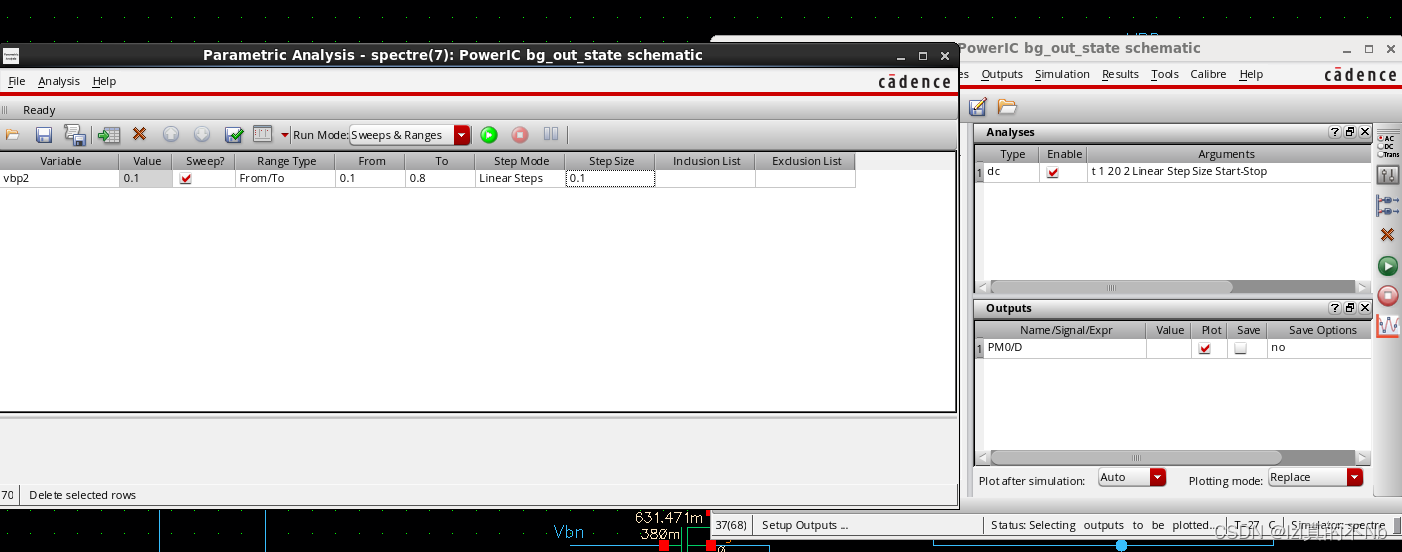

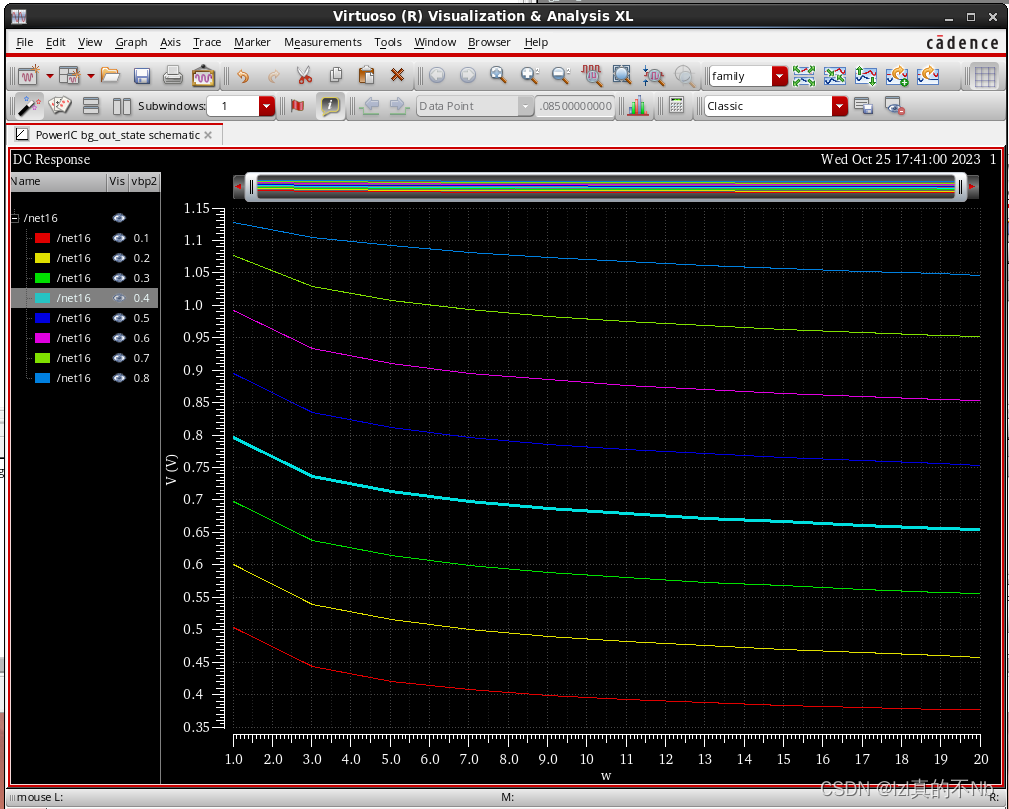

<3>先调节Vbp2:上面我们也分析了,完全可以放着NM12和NM11不管,因为他不会影响PM0和PM11的Vs,重要的是调节PM13和PM12的W/L和Vgs,这对于PM0和PM1的Vs影响很大,我们通过扫描的方式,确定Vs=800mV左右。

设置W=400n L=400n 对fingers和Vg扫描。

图:参数扫描

选择使得Vs=0.8V的曲线和参数即可。

(3)Vds分配

扫描NM12和NM13的W/L即可。

四、BUFFER设计以及补偿。

(1)BUFFER设计

BUFFER级很简单,是个电流镜结构,PMOS直接1:1实现电流的精确复制。

差分输入的两个NMOS W/L可以设置成一致,同第一级放大的NM11和NM12以时间电流的精确复制。(W/L也可以失配,后面我们会提到为什么要失配以及为社么用lvtmos管)

(2)相位曲线仿真

相位裕度仿真只需要仿误差放大和BUFFER级就i可以了。典型的单端输出和双端输入结构。

图:相位裕度仿真

相位裕度不够可以通过增大Cm米勒电容来弥补,可以看到再负载电流不同的情况下,我们所有的相位裕度均大于60°。

(增益和相位裕度仿真可以参考:https://blog.csdn.net/qq_33599939/article/details/123928961)

五、SR瞬态增强设置

<1>SR增强难点:

本文的负载电流最大高达100mA,同时带有50pF的负载电容。对于100mA的负载,功率PMOS的W/L≈,很大的长宽比导致电容很大,栅极容易出现SR上升慢的问题。

图:POWER MOS上升过慢导致过冲恢复太慢。

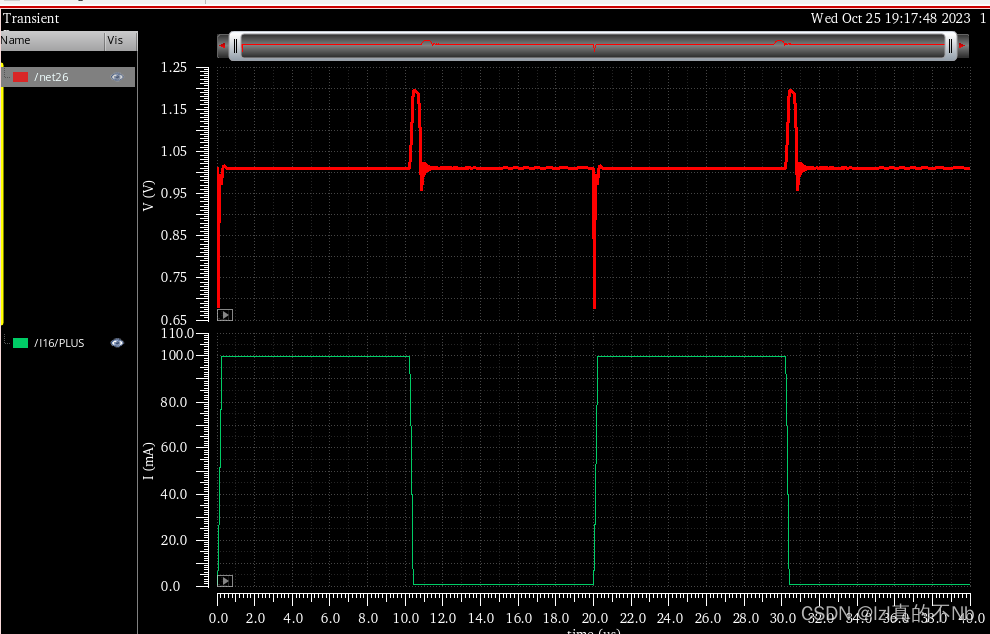

<2>增强方法:轻度失配

N30的W/L:8u/400n -> 4u/ 400n :让电流更多的流入下一级用以更快的充电:

可以更大的增加失配用以更快速的充电。但是输入端产生的电压容易降低Vgs从而使MOS离开饱和区(这也是为什么要用低vt管子)

图:轻度适配下的输出过冲,可以看到明显减小

增大失配:W/L:8u/400n -> 800n/400n

可以看出,LDO的瞬态响应已经很好了

代价:<1> 静态电流小幅增加

<2>第二级输入端产生电压差,会反馈到输出端产生直流偏置(但这个偏置很小,只有) A0是低频增益,大概只有几十个uV,只要你增益够大就可以忽略

结论:

总的来说,我的复现大概是失败了,指标基本都做到了,但是静态电流大了很多。

https://blog.csdn.net/weixin_47569031/article/details/132689861?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522169822376416800215073506%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=169822376416800215073506&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v1~rank_v31_ecpm-2-132689861-null-null.142%5Ev96%5Epc_search_result_base5&utm_term=2023%E9%9B%86%E5%88%9B%E8%B5%9B%E5%9B%BD%E5%AE%B6%E9%9B%86%E5%88%9B%E4%B8%AD%E5%BF%83&spm=1018.2226.3001.4187

https://blog.csdn.net/weixin_47569031/article/details/132689861?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522169822376416800215073506%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=169822376416800215073506&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v1~rank_v31_ecpm-2-132689861-null-null.142%5Ev96%5Epc_search_result_base5&utm_term=2023%E9%9B%86%E5%88%9B%E8%B5%9B%E5%9B%BD%E5%AE%B6%E9%9B%86%E5%88%9B%E4%B8%AD%E5%BF%83&spm=1018.2226.3001.4187

1040

1040

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?