上一篇文章我们介绍了SDC里面的各种约束,今天我们来看下PrimeTime UserGuide里面有关约束的描述是怎样的。(文末有惊喜!)

6.1 Timing Constraints

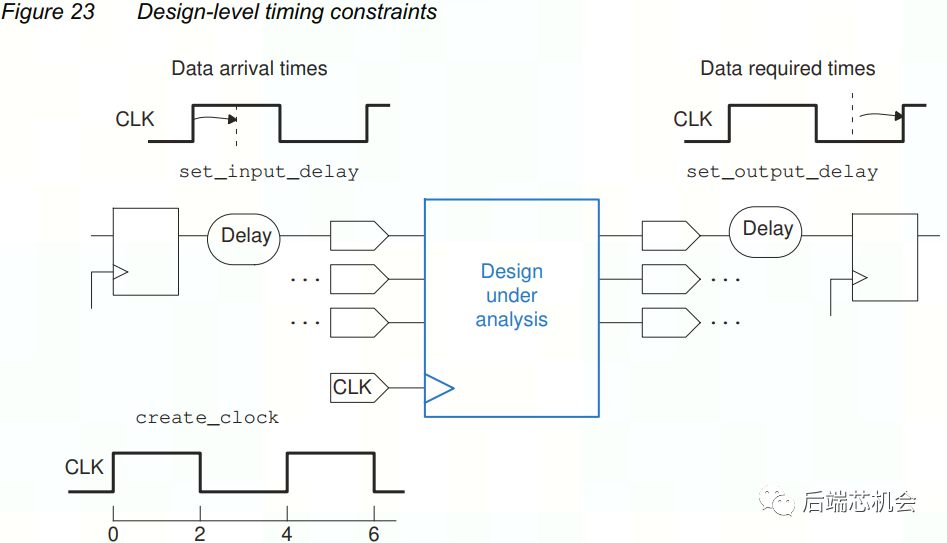

在开始时序分析之前,我们需要指定design中的时序约束。时序约束(也称为时序声明)限制了信号到达输入端或输出端有效的一个允许的时间范围。

6.2 Input delay

一般的,要在design输入端进行约束检查,工具需要知道信号在输入端的到达时间的相关信息。为了指定通向输入端的外部路径的时序,我们使用set_input_delay命令。工具使用此信息检查输入端和输入端fanout的时序违例。通过该命令,我们可以规定信号从时钟沿到指定输入端的最大或最小延迟。

将set_drive或set_driving_cell命令应用到端口会导致端口产生cell delay,该delay是外部driving-cell delay的load值。为了防止该delay被计算两次,我们先预估一下driving-cell的load相关延迟,然后从端口上的输入延迟中减去该量。

Input delay应等于从源头触发器的clk pin到的driving-cell输出pin的路径长度,减去driving-cell delay的load相关部分。下面的例子显示了L1时钟端口到端口IN1的外部路径。

当我们使用set_input_delay命令时,可以指定延迟值是否包括net latency或source latency。

例1:

如果从L1时钟端口到IN1的延迟(减去driving-cell的load相关延迟)为4.5,则该set_input_delay命令为:

set_input_delay 4.5 -clock PHI1 {IN1}

例2:

如果有来自多个时钟的路径到达同一个端口,请使用-add_delay选项指定每个端口。如果省略-add_delay选项,则会删除此端口之前已设定的delay值。如:

set_input_delay 2.3 -clock PHI2 -add_delay {IN1}

如果延迟源是电平敏感锁存器(level-sensitive latch),请使用-level_sensitive选项,这样就允许PT为源自该端口的路径确定正确的单周期时序约束。使用-clock_fall选项表示是负电平敏感锁存器,否则-level-sensitive选项一般意味着是一个正电平敏感锁存器。

如果想看到端口上的input delay具体值,我们可以使用report_port -input_delay报出该值。

在当前design中set_input_delay设置了input delay后,如果想移除该值,可使用命令remove_input_delay。一般默认是删除port_pin_list选项中的所有input delay信息。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?