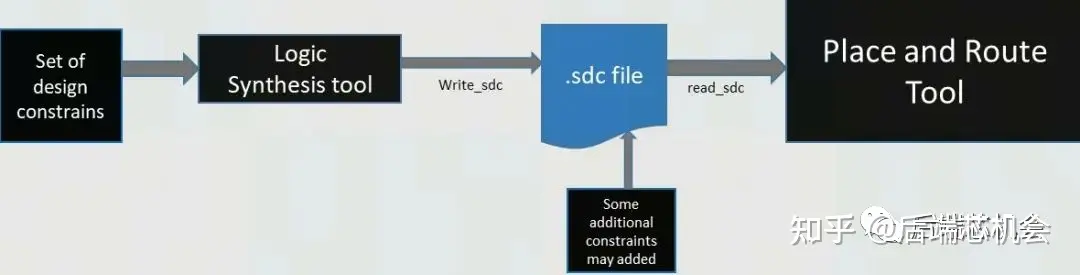

SDC是Synopsys设计约束“Synopsys Design Constraint”的缩写,是一种常用的约束设计的格式。SDC对电路的时序、功耗、面积等进行约束,从而使芯片满足设计要求的规范。SDC文件语法基于TCL格式,所有命令都遵循TCL语法。

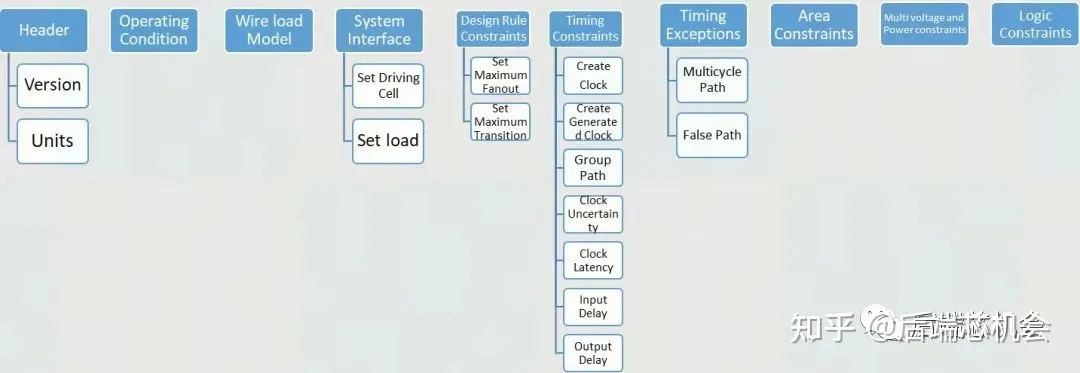

下图显示了一些重要的值得关注的约束

01、SDC Version

它表明了sdc当前的版本,目前有2.1,2.0,1.9或者更老的版本。

set sdc_version 2.1

02、Units

我们可以用set_unit命令去指定各种变量的单位,如:time、resistance、capacitance、voltage、current、power等。我们也可以单个set_unit命令去设置倍数单位。

set_unit -time ns -resistance kohm -capacitance of -voltage V -current mA

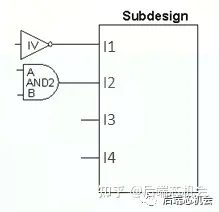

03、Set driving cells

规定了由Tech库中的cell驱动的输入输出端口的drive特性。这些命令将库引脚与输入端口相关联,以便可以准确地建模计算delay。

语法:

set_driving_load [-lib_cell lib_cell_name] [-library lib_name] [-rise] [-fall] [-min] [-max] [-pin pin_name] [-from_pin from_pin_name] [-dont_scale] [-no_design_rule] [-input_transition_rise rtrans] [-input_transition_fall ftrans] [-multiply_by_facrtor] [-clock clock_name] [-clock_fall] port_list

例:

set_driving_cell -lib_cell IV {I1}

set_driving_cell -lib_cell AND2 -pin Z -from_pin B {I2}

04、Set_load

设置当前设计中指定的port和net的load属性。load值的单位是本文件中定义的电容单位。

语法:set_load value objects [-subtract_pin_load] [-min] [-max] [[-pin_load] [-wire_load]]

例:set_load -pin_load 0.001 [get_ports {port[10]}]

05、Set maximum fanout

为特定的输入端口和/或设计设置最大扇出。

如:set_max_fanout 5 [get_ports {port[10]}]

06、Set maximum transition

设置最大转换时间。

如:set_max_transition 2.5 [get_ports IN]

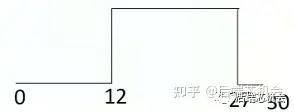

07、Create clock

在当前设计中创建一个时钟对象,将指定的source_objects定义为时钟源。

语法:create_clock [-name clock_name] [clock_sources] [-period value] [-waveform edge_list] [-add] [-comment]

例:

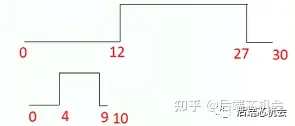

create_clock “u13/z” -name “CLK” -period 30 -waveform {12.0 27.0}

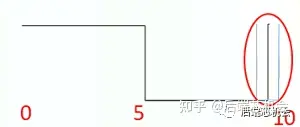

create_clock -name “PH12” -period 10 -waveform {0.0 5.0}

08、Create generated clock

创建一个generated clock,可以为generated clock对象指定pin或port。generated clock跟随master clock变化而自动变化。生成的时钟可以创建为分频时钟、倍频时钟、边缘分频时钟或反相时钟。

例:

create_generated_clock -multiplied_by 3 -source CLK [get_pins div3/Q]

上面的例子将生成一个时钟,该时钟是从名为CLK的原始时钟导出的。生成的时钟的频率将是原始时钟的3倍,时间周期将为原始时钟的三分之一(15ns –> 5ns)。

09、Group path

设置一组path或endpoints为group,有针对性地进行优化。指定endpoint后,所有通向这些endpoint的路径都在这组group里。

group_path -name “group1” -weight 2.0 -to {CLK1A CLK1B}group_path -name GROUP1 -from [get_ports ABC/in3] -to [get-ports FF1/D]

10、Clock uncertainty

在定义了时钟后,要注意在时钟网络中设置时钟的不确定性。时钟不确定性为设计留出了一定的margin,用来cover时钟网络和时钟源本身的非理想性导致的变化。它将不确定性的值设置为endpoint或时钟域之间预期的最差偏差。

语法:set_clock_uncertainity [object_list | -from from_clock | -rise_from rise_from_clock | -fall_from fall_from_clock -to to_clock | -rise_to rise_to_clock | -fall_to fall_to_clock] [rise] [-fall] [-setup] [-hold] uncertainty

例:

set_clock_uncertainty -setup 0.5 [get_clocks clk1]

set_clock_uncertainty -hold 0.2 [get_clocks clk1]

时钟的rise和fall time也可以设置clock uncertainty,如下所示,

set_clock_uncertainty -max_rise 0.12 [get_clocks clk1]

set_clock_uncertainty -max_fall 0.12 [get_clocks clk1]

set_clock_uncertainty -min_rise 0.12 [get_clocks clk1]

set_clock_uncertainty -min_fall 0.12 [get_clocks clk1]

11、Clock latency

时钟延迟指定从时钟源引脚到达时序元件的时钟引脚的时钟信号的latency。clock latency有两种类型,一种是net latency(默认),另一种是source latency(使用-source选项)

语法:set_clock_latency [-rise] [-fall] [-min] [-max] [-source] [-early] [-late] [-dynamic jitter] [-clock clock_list] delay object_list

例:set_clock_latency 2.35 [get_pins ABC/XYZ/CP]

12、Input delay

输入延迟定义了input port相对于时钟边缘的时序要求。如果未指定,则假定input port具有零输入延迟。delay值是起始点和设置set_input_delay的对象之间相对于时钟边缘的延迟决定的。

例:set_input_delay -max 1.35 -clock clk1 {ain bin}

13、Output delay

set_output_delay设置output 端口上相对于时钟边缘的输出延迟要求。如果未指定,则假定输出端口具有零输出延迟。

例:set_output_delay 1.7 -clock [get_clocks CLK1] [all_outputs]

14、Multicycle paths

多周期路径是不能满足单周期时序要求路径的例外。在多周期路径中,信号需要一个以上的单个时钟周期才能从路径的起点传播到终点。此命令指定了data path必须进行setup或hold检查的周期数。以下命令设置了从A到B的两个周期的约束。

set_multicycle_path 2 -from A -to B

15、False paths

false path是指不能传播信号的路径。时序分析时应排除false path。SDC命令set_false_path用于定义false path。

set_false_path -from U1/G -to U1/D

SUMMARY

以上描述了SDC中非常重要的常用的15个约束命令,实际上在一个复杂的design中还有很多重要的约束需要用到,这里不再提及。以下是15个约束的总结:

1. SDC Version

2. Units

System Interface

3. Set driving cells

4. Set load

Design rule constraints

5. Set maximum fanout

6. Set maximum Transition

Timing constraints

7. Create Clock

8. Create Generated Clock

9. Group Path

10. Clock Uncertainty

11. Clock Latency

12. Input Delay

13. Output Delay

Timing Exception

14. Multicycle Path

15. False Path

想查看更多后端知识和文章,请关注微信公众号:houduanxinjihui。

1297

1297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?