前言

在整理的时候发现Veriolg可以直接对字符串进行赋值。这里进行记录补充

一、字符串赋值

此处参考FPGA基础设计(8)Verilog常数赋值、字符串、标识符

(一)简介

Verilog HDL同样也支持字符串的使用,使用双引号“”表示字符串内容,一个字符串必须放在一行内。在表达式和赋值语句中使用字符串,工具会将其视作无符号整数,一个字符对应一个8bit的ASCII码。

\n、\r、\t、\和"等常用的转义字符,Verilog HDL也同样支持。

(二)例子

module test

(

input clk,

output reg [8*4-1:0] c ,

output [8*4-1:0] d

);

assign d = "CUIT";

always @(posedge clk)

c <= "CUIT";

endmodule

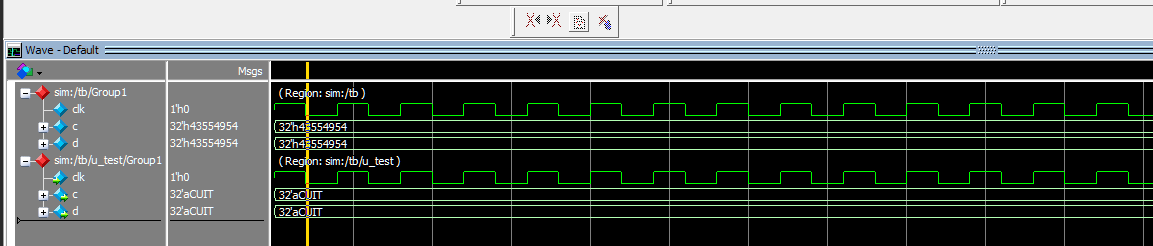

(三)仿真结果

由于一个字母对应8位ASCII码,CUIT四个字母对应4x8=32位 位宽,相应的16进制ASCII码为(32'h43_55_49_54)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?