Verilog系统函数

前言

在Verilog HDL语言中每个系统函数和任务前面都用一个标识符$来加以确认。这些系统函数和任务提供了非常强大的功能。

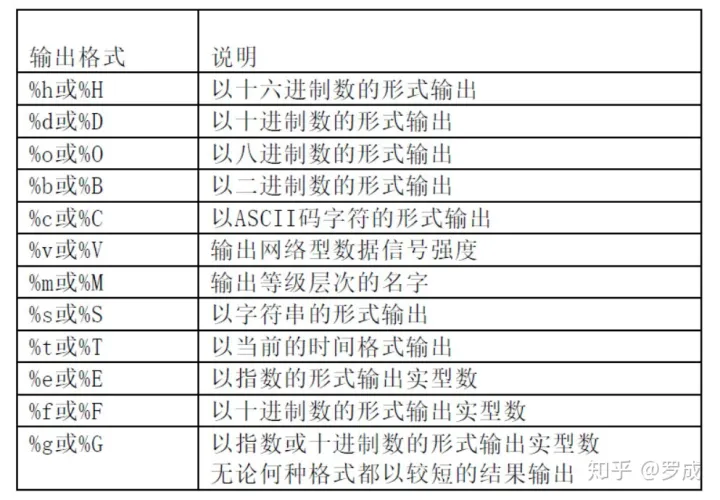

在ModelSim仿真时添加系统函数利于调试。

一、$width

(一)简介

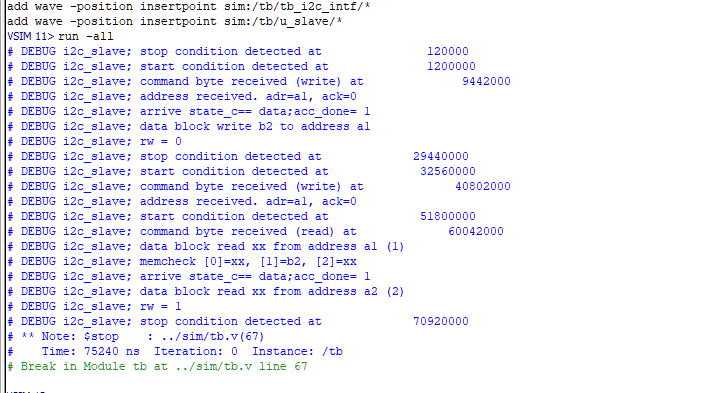

$width函数用于检查信号脉冲的宽度是否达到要求。而信号脉冲的宽度由信号的reference_event和data_event决定,如下图所示

(二)$width 参数

| Argument | Description | 翻译 |

|---|---|---|

| reference_event | Timestamp edge triggered event | 时间戳边缘触发事件 |

| (data_event - implicit) | Timecheck edge triggered event | 时间检查边沿触发事件 |

| limit | Non-negative constant expression | 非负常量表达式 |

| threshold(optional) | Non-negative constant expression | 非负常量表达式 |

| notifier (optional) | Reg | — |

-

第二个参数data_event是一个隐式参数,也就是说你不用将它写出来。系统会根据你的第一个参数得到第二个参数,也就是说,第二个参数就是第一个参数的反向取沿。

-

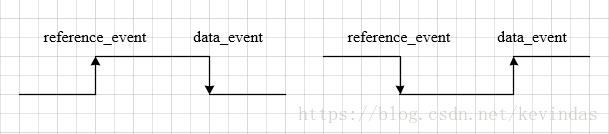

第3、4个参数是可选的。但是需要注意要使用第4个参数,首先要有第3个参数。

-

第3个参数是门限值,如果脉冲小于该门限,是不会报violation的,没有该参数时该值为0。

(三)例子

1.下面的示例演示了一些合法和非法调用的示例:

//Legal calls

$width ( negedge clr , lim ) ;

$width ( negedge clr , lim , thresh , notif) ;

$width ( negedge clr , lim , 0 , notif ) ;

//Illegal calls

$width ( negedge clr , lim, , notif ) ;

$width ( negedge clr , lim , notif);

2.如图

二、Specify参数

这些主要用于提供定时和延迟值,使用specparam关键字来声明。它既可以在specify块内使用,也可以在主模块体中使用。

// Use of specify block

specify

specparam t_rise = 200, t_fall = 150;

specparam clk_to_q = 70, d_to_q = 100;

endspecify

// Within main module

module my_block ( ... );

specparam dhold = 2.0;

specparam ddly = 1.5;

parameter WIDTH = 32;

endmodule

三、$display

(一)简介

$display(p1,p2,....pn);

作用是用来输出信息,即将参数p2到pn按参数p1给定的格式输出。参数p1通常称为“格式控制”,参数p2至pn通常称为“输出表列”。$display自动地在输出后进行换行。

(二)格式说明

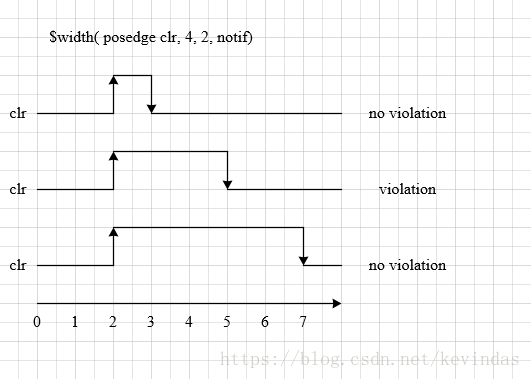

格式说明,由"%"和格式字符组成。它的作用是将输出的数据转换成指定的格式输出。格式说明总是由“%”字符开始的。对于不同类型的数据用不同的格式输出。下表中给出了常用的几种输出格式。

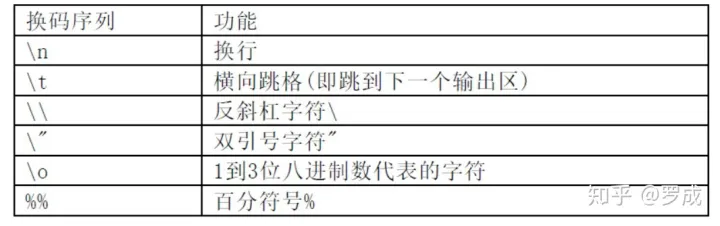

普通字符,即需要原样输出的字符。其中一些特殊的字符可以通过下表中的转换序列来输出。下面表中的字符形式用于格式字符串参数中,用来显示特殊的字符。

(三)例子

1.例1

module disp;

initial

begin

$display("\\\t%%\n\"\123");

end

endmodule

输出结果

\%

"S

从上面的这个例子中可以看到一些特殊字符的输出形式(八进制数123就是字符S)。

2.例2

module disp;

reg[31:0] rval;

pulldown(pd);

initial

begin

rval=101;

$display("rval=%h hex %d decimal", rval, rval);

$display("rval=%o otal %b binary", rval, rval);

$display("rval has %c ascii character value",rval);

$display("pd strength value is %v",pd);

$display("current scope is %m");

$display("%s is ascii value for 101",101);

$display("simulation time is %t",$time);

end

endmodule

输出结果

rval=00000065 hex 101 decimal

rval=00000000145 octal 00000000000000000000000001100101 binary

rval has e ascii character value

pd strength value is StX

current scope is disp

e is ascii value for 101

simulation time is 0

更详细例子参考Verilog语法之十二:系统函数和任务

四、$monitor

(一)格式

$monitor(p1,p2,.....,pn);

$monitor;

$monitoron;

$monitoroff;

(二)功能

任务$ monitor提供了监控和输出参数列表中的表达式或变量值的功能。其参数列表中输出控制格式字符串和输出表列的规则和$display中的一样。

当启动一个带有一个或多个参数的$ monitor任务时,仿真器则建立一个处理机制,使得每当参数列表中变量或表达式的值发生变化时,整个参数列表中变量或表达式的值都将输出显示。

如果同一时刻,两个或多个参数的值发生变化,则在该时刻只输出显示一次。但在$ monitor中,参数可以是$ time系统函数。这样参数列表中变量或表达式的值同时发生变化的时刻可以通过标明同一时刻的多行输出来显示。如:$ monitor($time,,"rxd=%b txd=%b",rxd,txd);

在$display中也可以这样使用。注意在上面的语句中,“,"代表一个空参数。空参数在输出时显示为空格。

(三)$ monitoron/$ monitoroff

$ monitoron和$ monitoroff任务的作用是通过打开和关闭监控标志来控制监控任务monitor的启动和停止,这样使得程序员可以很容易的控制$monitor何时发生。

-

- 其中$ monitoroff任务用于关闭监控标志,停止监控任务$monitor

-

- $ monitoron则用于打开监控标志,启动监控任务$ monitor。

-

- 通常在通过调用$ monitoron启动$ monitor时,不管$ monitor参数列表中的值是否发生变化,总是立刻输出显示当前时刻参数列表中的值,这用于在监控的初始时刻设定初始比较值。

-

- 在缺省情况下,控制标志在仿真的起始时刻就已经打开了。在多模块调试的情况下,许多模块中都调用了$ monitor,因为任何时刻只能有一个$ monitor起作用,因此需配合$ monitoron与$ monitoroff使用,把需要监视的模块用$ monitoron打开,在监视完毕后及时用$ monitoroff关闭,以便把$monitor 让给其他模块使用。

-

- $ monitor与$ display的不同处还在于$ monitor往往在initial块中调用,只要不调用 monitoroff,$ monitor便不间断地对所设定的信号进行监视。

五、$ time/$ realtime

(一)$time

1.简介

.时间度量系统函数,在Verilog HDL中有两种类型的时间系统函数: t i m e 和 time和 time和realtime。用这两个时间系统函数可以得到当前的仿真时刻。

$time可以返回一个64比特的整数来表示的当前仿真时刻值。该时刻是以模块的仿真时间尺度为基准的。

2.例子

`timescale 10ns/1ns

module test;

reg set;

parameter p=1.6;

initial

begin

$monitor($time,,"set=",set);

#p set=0;

#p set=1;

end

endmodule

输出结果为:

0 set=x

2 set=0

3 set=1

在这个例子中,模块test想在时刻为16ns时设置寄存器set为0,在时刻为32ns时设置寄存器set为1。但是由$time记录的set变化时刻却和预想的不一样。这是由下面两个原因引起的:

-

$ time显示时刻受时间尺度比例的影响。在上面的例子中,时间尺度是10ns,因为$ time输出的时刻总是时间尺度的倍数,这样将16ns和32ns输出为1.6和3.2。

-

因为$time总是输出整数,所以在将经过尺度比例变换的数字输出时,要先进行取整。在上面的例子中,1.6和3.2经取整后为2和3输出。注意:时间的精确度并不影响数字的取整。

(二)$realtime

1.简介

$ realtime和$ time的作用是一样的,只是$ realtime返回的时间数字是一个实型数,该数字也是以时间尺度为基准的。

2.例子

举例说明:

`timescale10ns/1ns

module test;

reg set;

parameter p=1.55;

initial

begin

$monitor($realtime,,"set=",set);

#p set=0;

#p set=1;

end

endmodule

输出结果为:

0 set=x

1.6 set=0

3.2 set=1

从上面的例子可以看出,$ realtime将仿真时刻经过尺度变换以后即输出,不需进行取整操作。所以$ realtime返回的时刻是实型数。

本文介绍了Verilog HDL中的关键系统函数,包括$width、Specify参数、$display、$monitor及$time/$realtime等,解释了它们的功能、使用格式及应用场景,并通过实例展示了如何运用这些函数来辅助调试。

本文介绍了Verilog HDL中的关键系统函数,包括$width、Specify参数、$display、$monitor及$time/$realtime等,解释了它们的功能、使用格式及应用场景,并通过实例展示了如何运用这些函数来辅助调试。

1952

1952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?