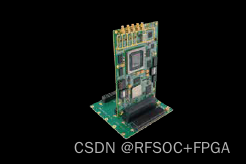

该模块是一款3u VPX 商用现成的直接射频采集及处理系统,采用传统的雷达信号处理架构,第3代Xilinx 射频片上系统(RFSoC)XCZU47DR+TI TMS320C6678ACYPA(DSP)。可最大限度地提高I/O通道密度,降低射频信号链的复杂性,并实现异构处理能力。

*FPGA与DSP之间具有EMIF接口,SRIO接口等数据传输能力

*FPGA及DSP的程序上电自加载均通过板内外挂存储器实现,远程加载方式采用网口(后替代为低速串口)进行加载

*工作时钟源颗选择外部输入时钟100MHz,也颗选择板上晶振提供,其余时钟采用板上晶振自供。

PS:1*QSPl Flash(2GB)固化配置文件 1*ETH(引至VPX接口) 1*JTAG调试接口

PL:RS422串口 LVDS SRIO EMIF

内存:PL: 2*DDR4(256M,16bit)

PS:1*DDR4 (256M,16bit)

供电:VPX电源供电接口

3973

3973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?