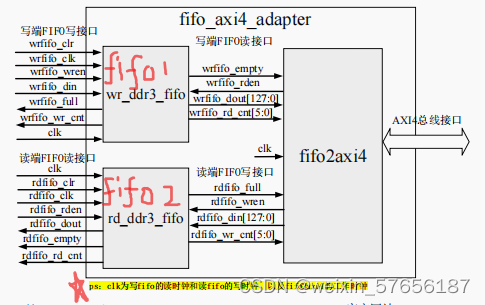

AXI4 转 FIFO 接口模块设计

PL 端要想读写 DDR,需要通过 AXI 总线,使用 PS 侧的 DDR 控制器,完成数据的读写。模块能够将数据转换成 AXI4 格式,通过 AXI 总线传输给 PS 侧 DDR 控制器,实现数据对 DDR 的读写操作。在 PS 与 PL 之间,存在有 4 个高性能 的 AXI 从接口(HP 接口, PS 端为从设备),该接口用于方便 PL 端与 DDR 间 大量数据的读写操作。任何情况下,只使用DDR控制器都 会出现问题,即使写入和读出的速率一样也是会出现 问题的,更何况实际应用中总是读写不连续的,就更 会出现问题所以要使用FIFO

其中,wr_ddr3_fifo 和 rd_ddr3_fifo 为上文中我们提到的读写 FIFO,用于存 储读写数据,同时解决时钟域等问题。fifo2axi4 为 AXI4 接口转换模块,负责 fifo 与 axi4 接口间的转换,将写侧 FIFO 里的数据读出然后存储在 DDR 存储器 以及将 DDR 存储器读出的数据存放到读侧 FIFO 缓存。

上面的读写FIFO都是先读形式的。

用FIFO转AXI4,就把对DDR的读写问题转换成对FIFO的读写控制问题。

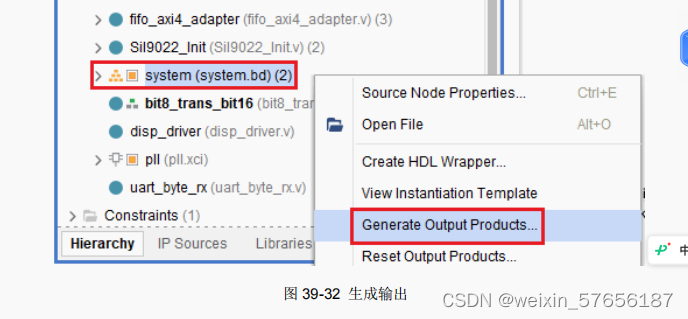

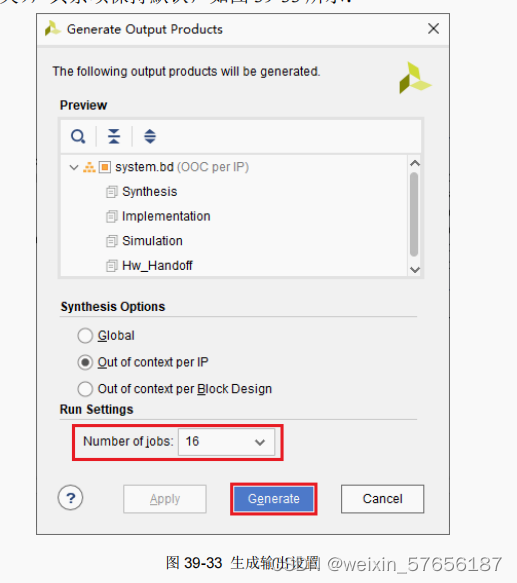

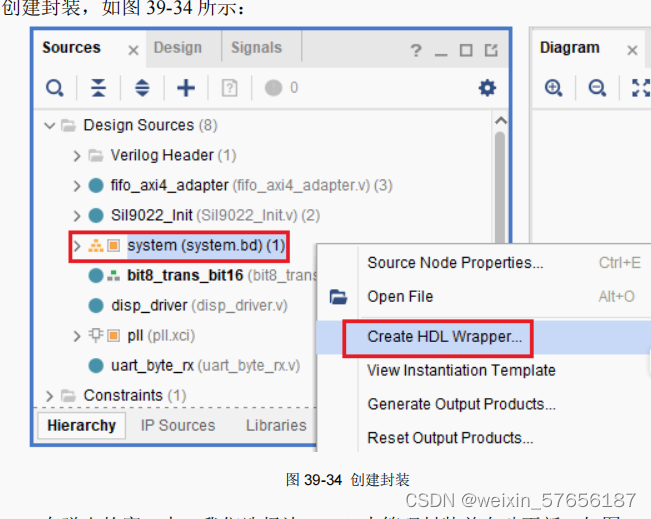

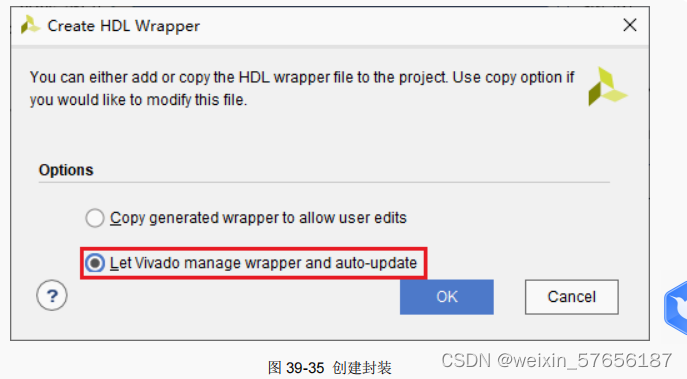

创建BD

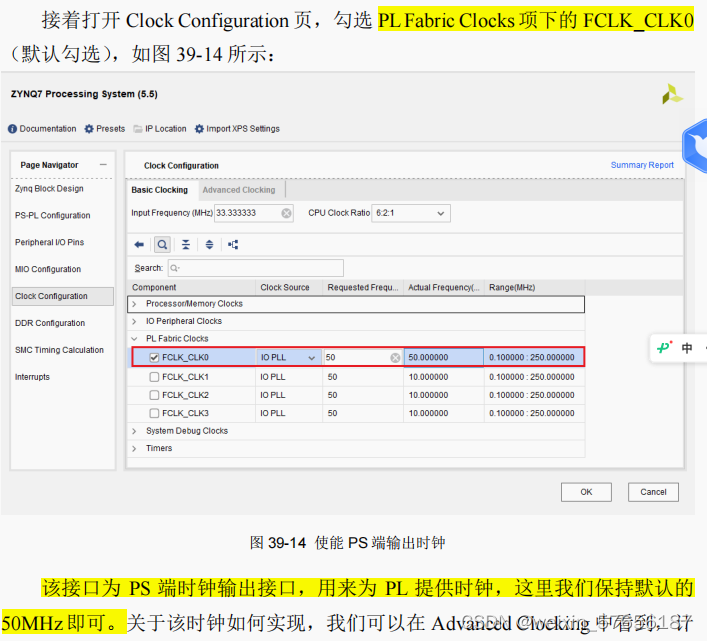

对ZYNQ的IP进行配置

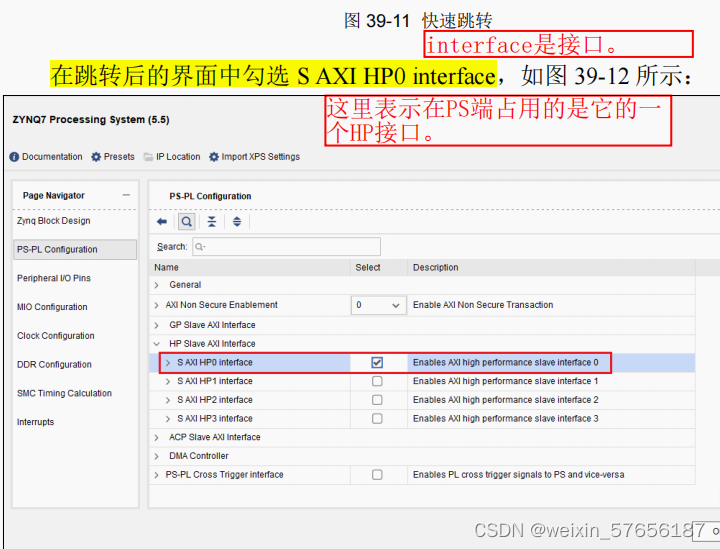

这里本次设计我们需要借助 HP 接口来实现数据写入到 PS 侧的 DDR3,所以要配置HP接口:

图形化界面快速跳转

使能HP接口

添加互联和复位IP核

端口连接

写顶层文件

为连接SDK做准备

引脚约束

生成比特流

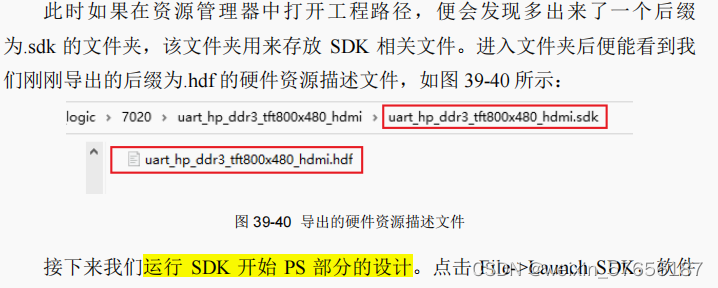

导出硬件

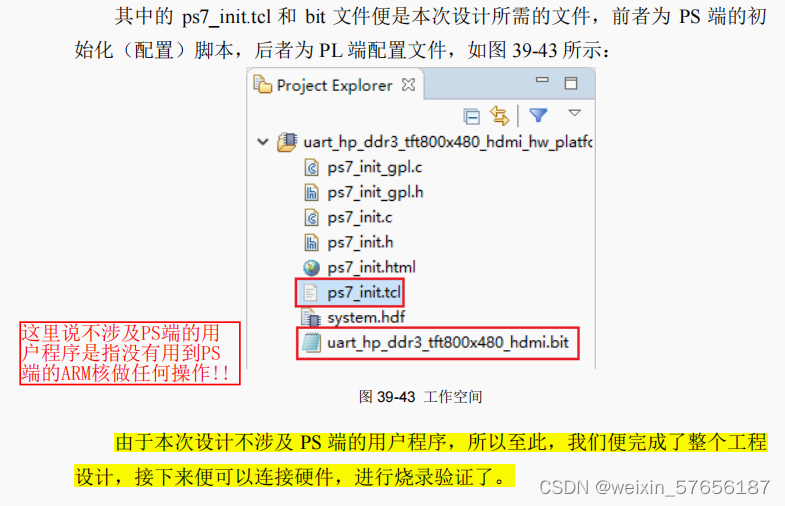

运行sdk

板级验证

硬件连接

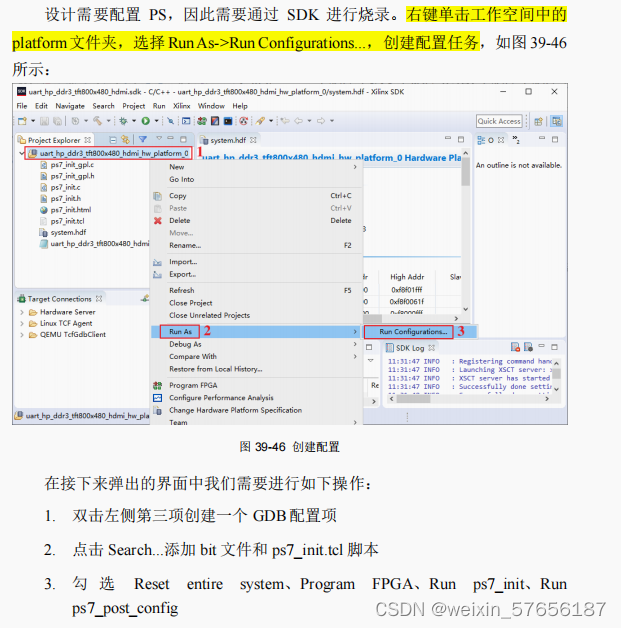

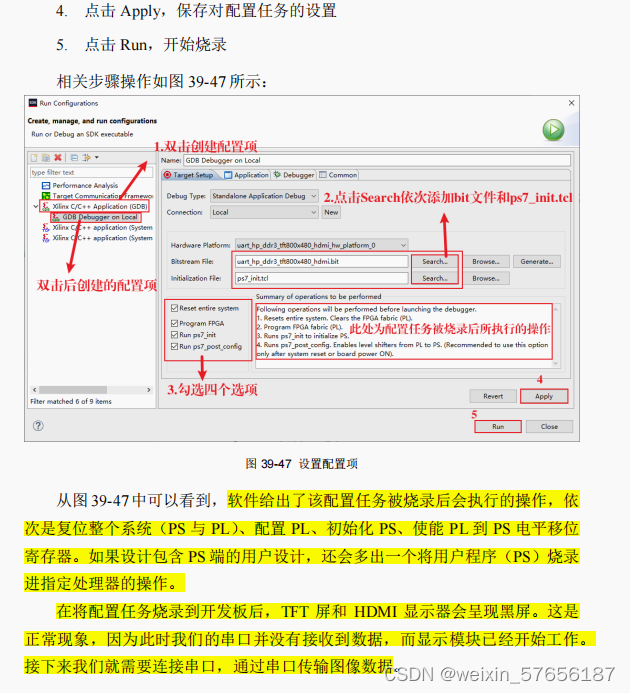

创建配置项

要把多路数据缓存到DDR上怎么处理?

怎么把自己的.v文件添加到BD文件中?

第一步:打开.bd文件,必须双击,bd文件界面转换到BD文件界面

第二步:想要添加自己的模块,找到Design Sources里面需要添加的模块,右键选择Add Module to Block Design。

后面从连接端口到生成HDF文件的过程跟上面一样。

2616

2616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?