GPIO

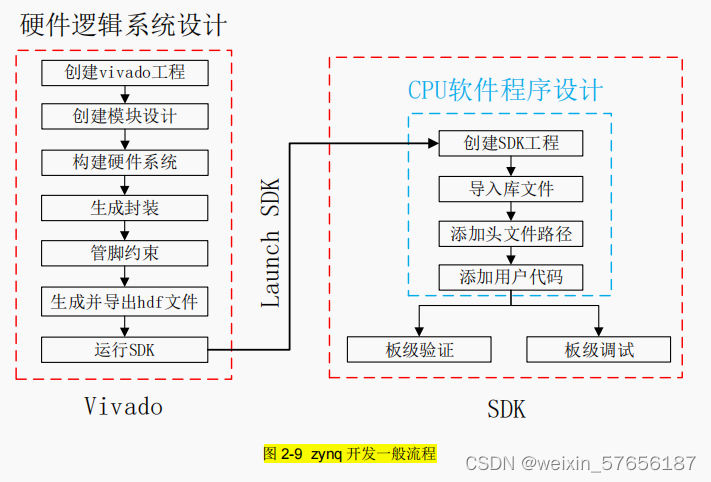

PS和PL联合工程的涉及步骤

生成封装【“Generate Output Products...”生成输出;“Create HDL Wrapper...”创建 HDL 封装】

引脚约束;

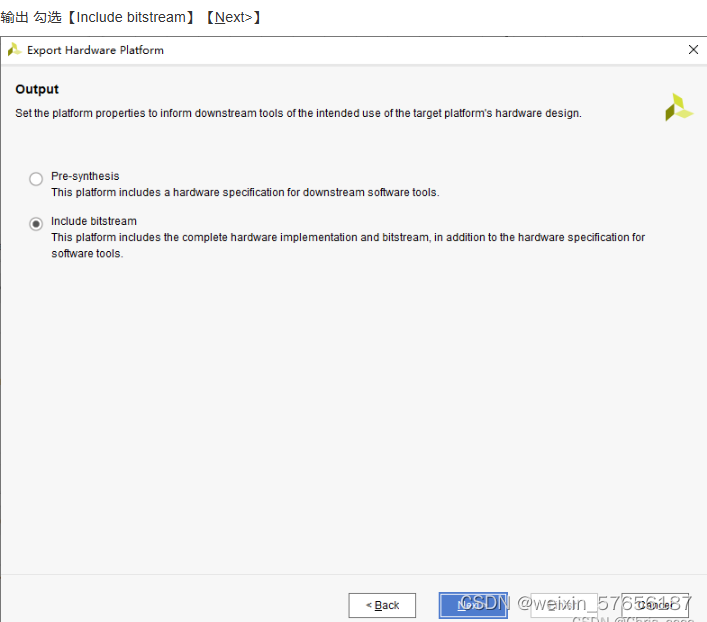

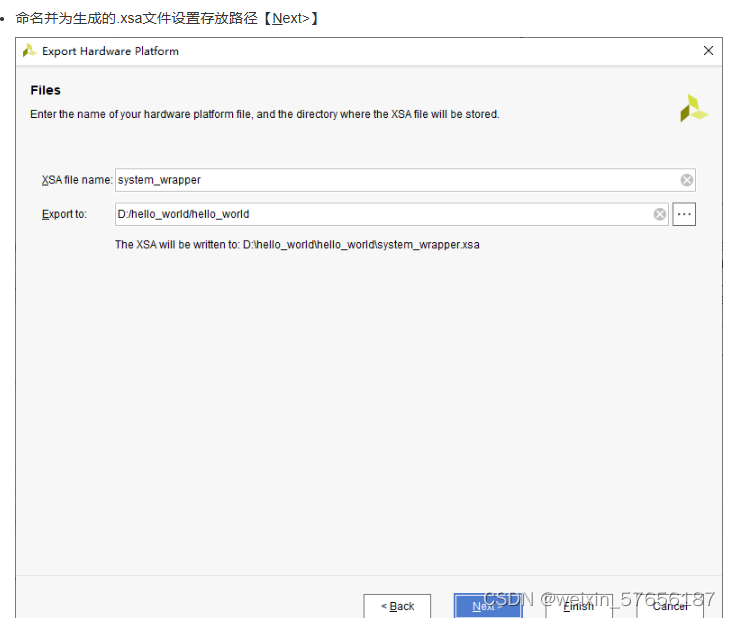

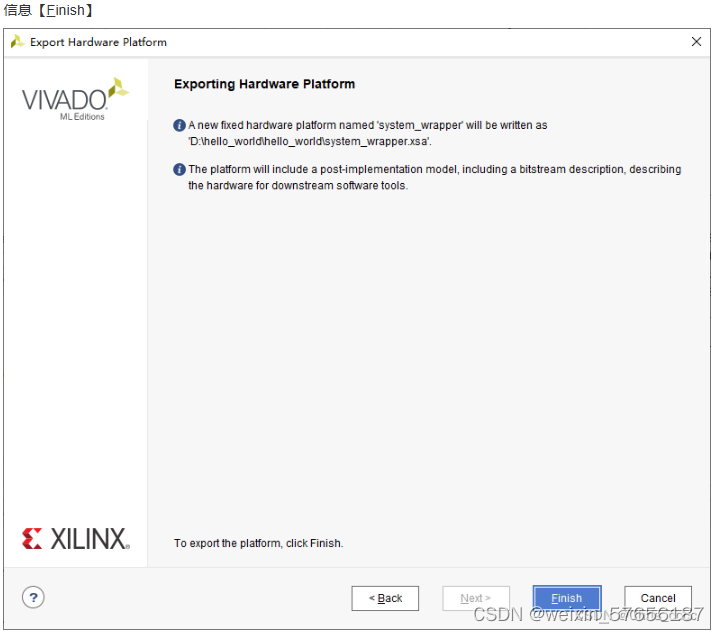

生成BIT流,file-->Export -->选择“ExportHardware...”将硬件描述文件(HDF文件)导出;

若是使用vivado2018版本,使用步骤就和教程中完全一致。

file-->latch SDK,启动SDK;

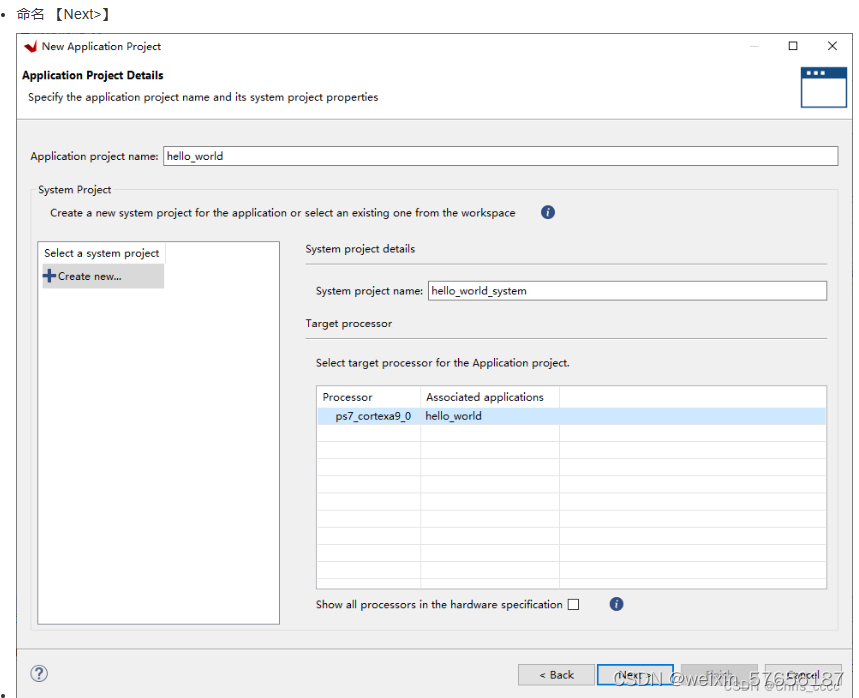

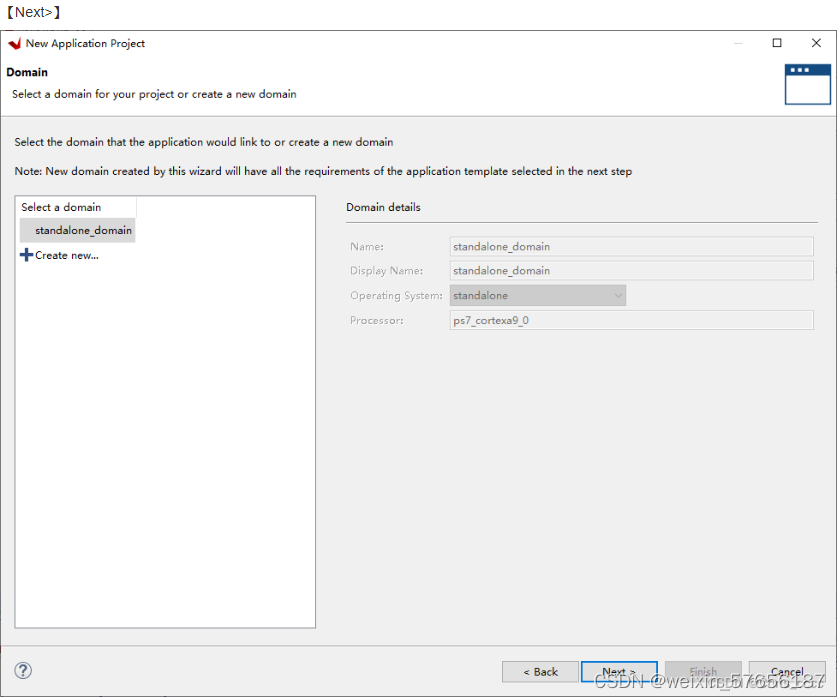

创建SDK工程;

添加应用库即对应的LIB文件夹;

添加头文件路径和声明;

编写main.c文件;

添加用户宏定义【就是把main.c函数中用到的所有变量和GPIO的端口号对应一下,这样主函数中对变量的操作就是对端口的操作】;

上板验证和调试。

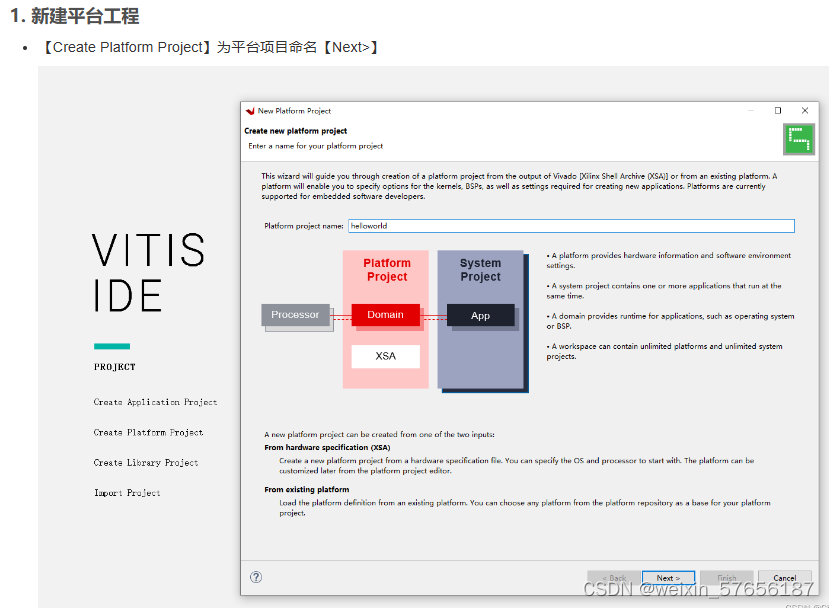

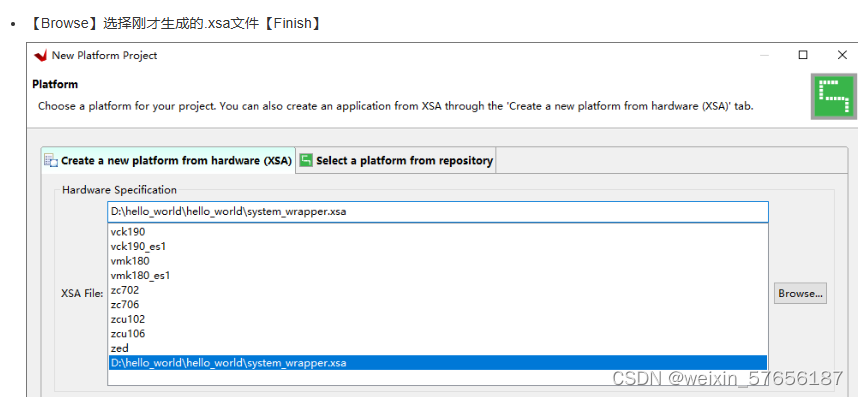

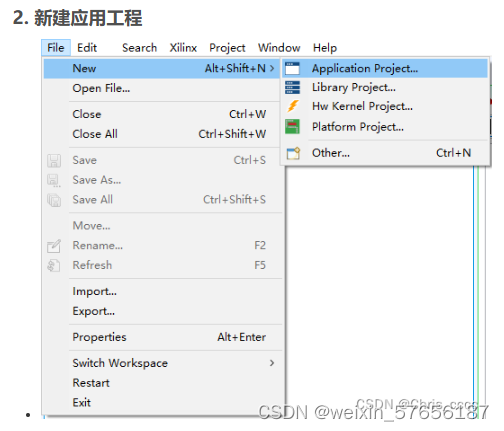

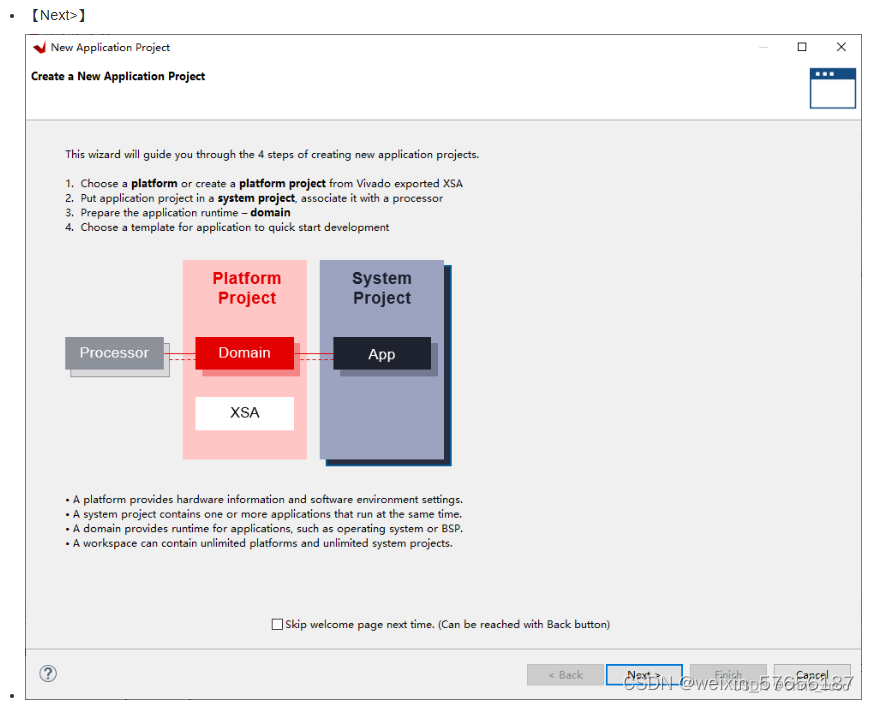

viviado的2020版本所以执行如下操作:

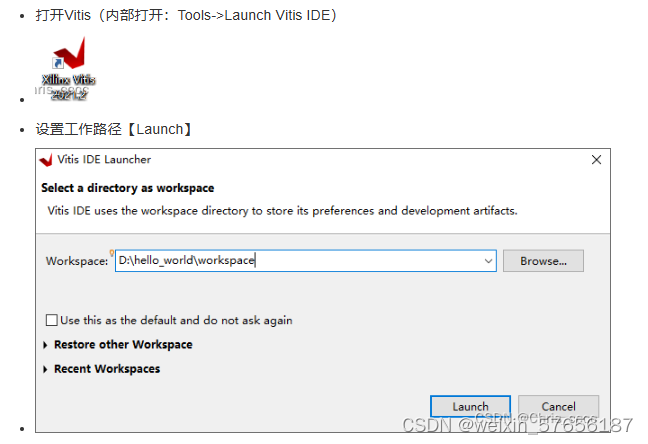

手动打开vitis,或者在vivado的内部用tool-->latch vitis ide打开;

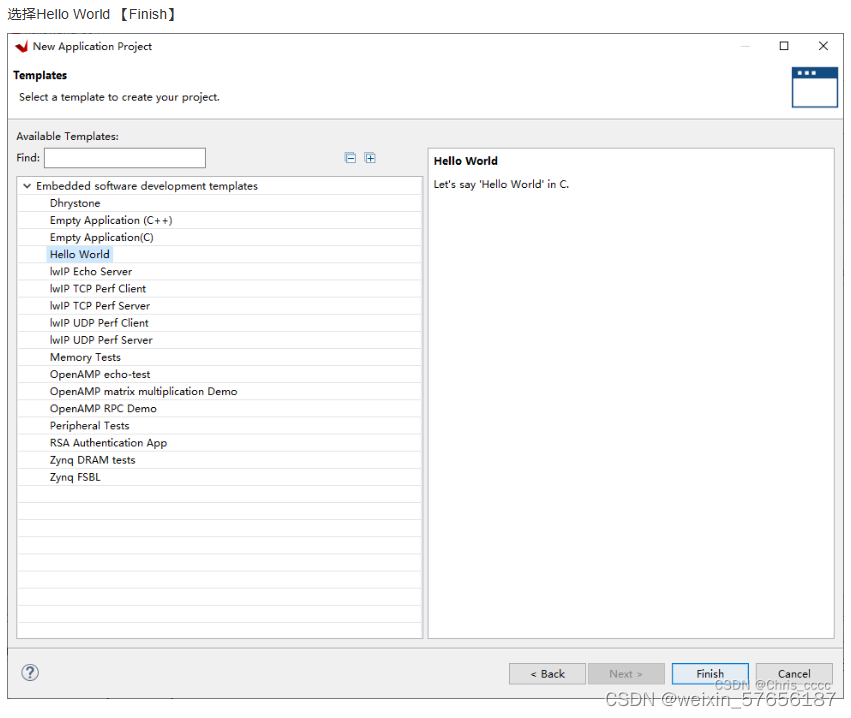

下面这里是选择生成的工程中自带的例程,这里可以选择一个空的例程。(C)表示用C写的;

添加应用库即对应的LIB文件夹;

添加头文件路径和声明;

编写main.c文件;

添加用户宏定义【就是把main.c函数中用到的所有变量和GPIO的端口号对应一下,这样主函数中对变量的操作就是对端口的操作】;

上板验证和调试。

项目中的main.c文件怎么写?

写main.c文件本质上和写嵌入式的编码没有什么区别。

关于GPIO的一些系统函数在gpiops: xgpiops.c File Reference (xilinx.github.io)有详细介绍。

xgpiops.c只要是对GPIO进读写;xgpiops.h是.c文件的头文件;

通过上述的系统函数,可以实现对GPIO的初始化,读,写等操作。

514

514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?