1、题目要求:

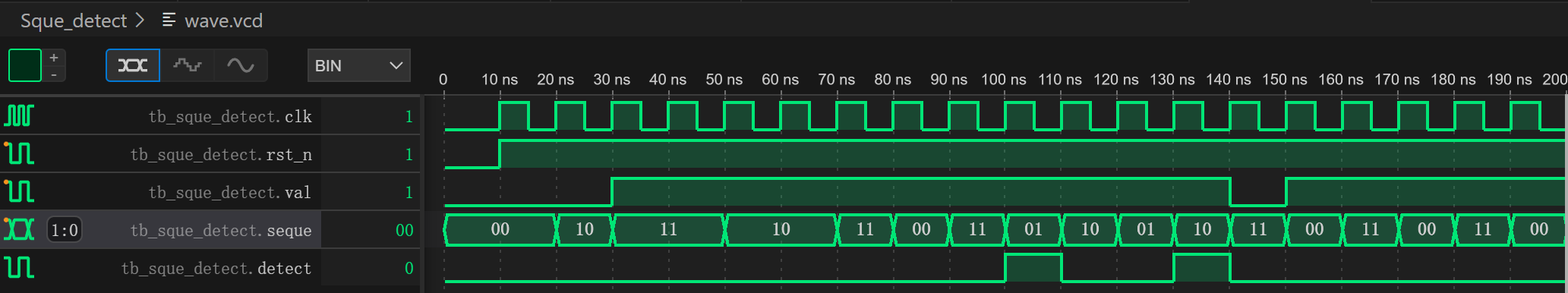

| 设计一个可以进行序列检测的模块。模块每拍并行输入2bit的数,请实现对(1011001)的序列检测功能。输入数据的顺序为高位2bit先输入,当检测位(val)高电平时开始检测。若检测到该序列,则输出一拍高电平脉冲信号。并且当检测位信号拉低再拉高时,要清除之前的输入重新开始检测。 模块名称和求: module name: sque_detect input ports: clk, rst_n(同步复位), [1:0]seque, val output ports: detect 示例波形:

|

2、Verilog代码

module sque_detect(

input clk,

input rst_n,

input [1:0]seque,

input val,

output reg detect

);

reg [7:0] tmp;

always@(posedge clk)begin

if(!rst_n)

tmp<=0;

else if(!val) //当检测位val为高时开始检测,即为enable使能信号

tmp<=0;

else if(val)

tmp[7:0]<={tmp[5:0],seque[1:0]}; //因为只检测七位序列,两位两位的输入,因此用八位向量存放

end //对应八位移位寄存器,每次移动两位

always@(posedge clk)begin

if(!rst_n)

detect<=0;

else if(tmp[7:1]==7'b1011001 || tmp[6:0]==7'b1011001) //分别检测7-1和6-0是否对应序列

detect<=1;

else

detect<=0;

end

endmodule用简单的移位寄存器进行实现即可。八位移位寄存器存放数据。 八位宽的向量来实现八位串进串出移位寄存器。

3、testbench:

module tb_sque_detect();

reg clk;

reg rst_n;

reg [1:0] seque;

reg val;

wire detect;

sque_detect U(clk,rst_n,seque,val,detect);

initial begin

#10 rst_n=1;seque=2'b01;val=0;clk=0;

#10 rst_n=0;seque=2'b00;val=1;clk=1;

#10 rst_n=0;seque=2'b00;val=1;clk=0;

#10 rst_n=1;seque=2'b10;val=1;clk=1;

#10 rst_n=1;seque=2'b10;val=1;clk=0;

#10 rst_n=1;seque=2'b11;val=1;clk=1;

#10 rst_n=1;seque=2'b11;val=1;clk=0;

#10 rst_n=1;seque=2'b00;val=1;clk=1;

#10 rst_n=1;seque=2'b00;val=1;clk=0;

#10 rst_n=1;seque=2'b11;val=1;clk=1;

#10 rst_n=1;seque=2'b11;val=1;clk=0;

#10 rst_n=1;seque=2'b01;val=1;clk=1;

#10 rst_n=1;seque=2'b01;val=1;clk=0;

#10 rst_n=1;seque=2'b10;val=1;clk=1;

#10 rst_n=1;seque=2'b10;val=1;clk=0;

end

initial begin

$dumpfile("test.vcd");

$dumpvars(0);

end

endmodule波形图:

4、总结:

用八位向量实现八位移位寄存器。然后分别检测[7:1]和[6:0]序列就行。

7925

7925

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?