问题描述:在学习模拟集成电路以及数字集成电路时,我们都清楚地知道:当MOS管截止时,没有导电沟道,Ids为0;当MOS管处于线性或者饱和区时,存在导电沟道,Ids也有相应的计算公式,但是我们始终没有注意到Vds是什么样的(+_+)?

1、当MOS管“导通时”

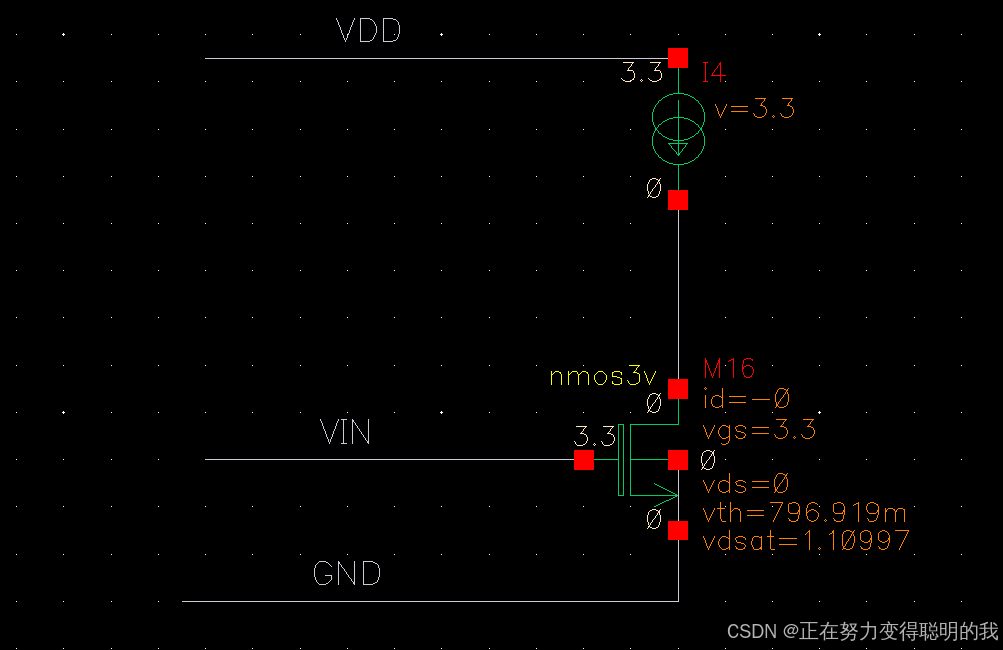

如下所示,设置电流源电流为0。当NMOS管的Vgs>Vth时,NMOS导通,但是此时由于电流源的存在,Ids等于0,此时NMOS处于深度线性区,我们可以根据线性区的电流公式:

对于这个式子,很明显,(Vgs-Vth)不等于0,故我们可以得到此时的Vds约等于0。具体如下图所示的直流仿真结果:

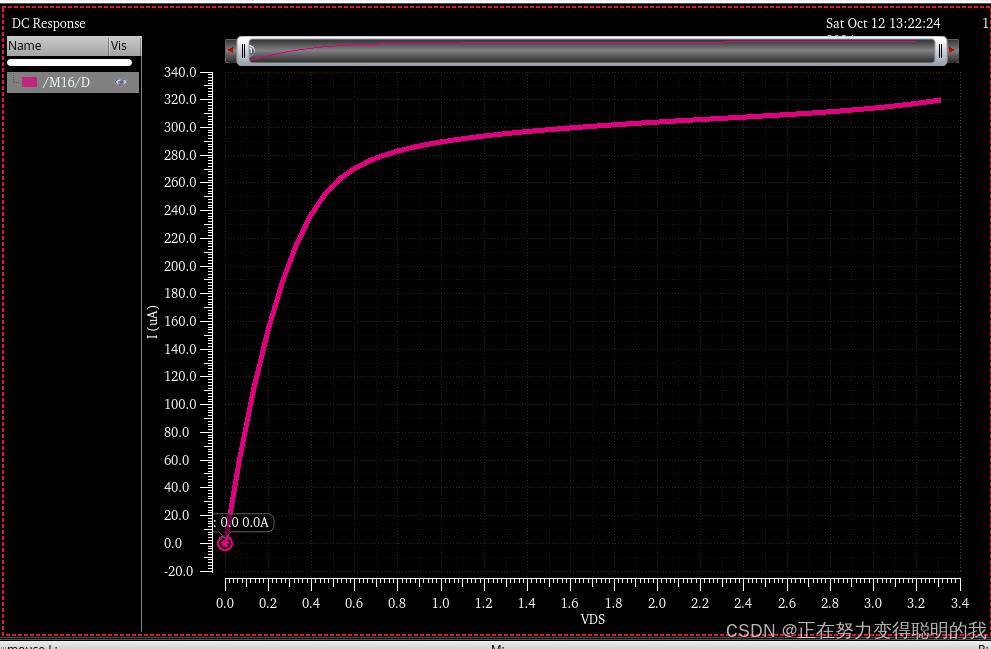

当然,我们也可以从NMOS的-

特性曲线上观察到,如下图是NMOS的

-

特性曲线:可以看到,当Vgs>Vth,且Ids等于0时,Vds等于0。

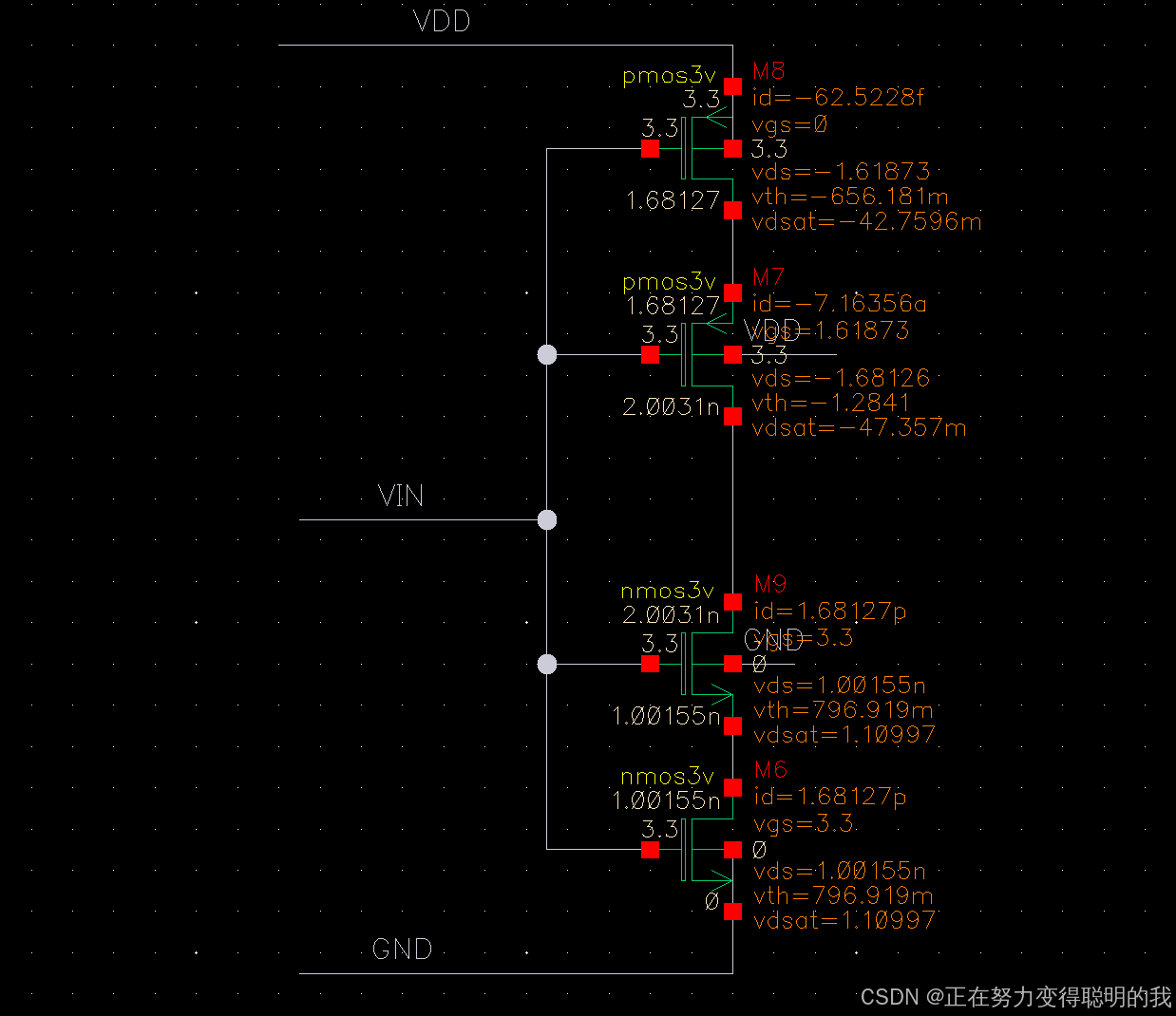

2、当MOS管截止时

如下所示,上方的PMOS网络是两个PMOS进行串联;同样,下方的NMOS网络是两个NMOS进行串联,那么当输入为高电平VDD时,下方的两个NMOS导通,上方的两个PMOS截止,Ids等于0,那么下方的两个NMOS的Vds均约等于0,而上方处于截止状态的PMOS的|Vds|,一个是1.618,一个是1.681,均为1.6多,相当于两个PMOS构成一个分压器(我是这样理解的,设置的VDD为3.3V,而两个PMOS相当于阻抗,且其阻抗值相差不大)。

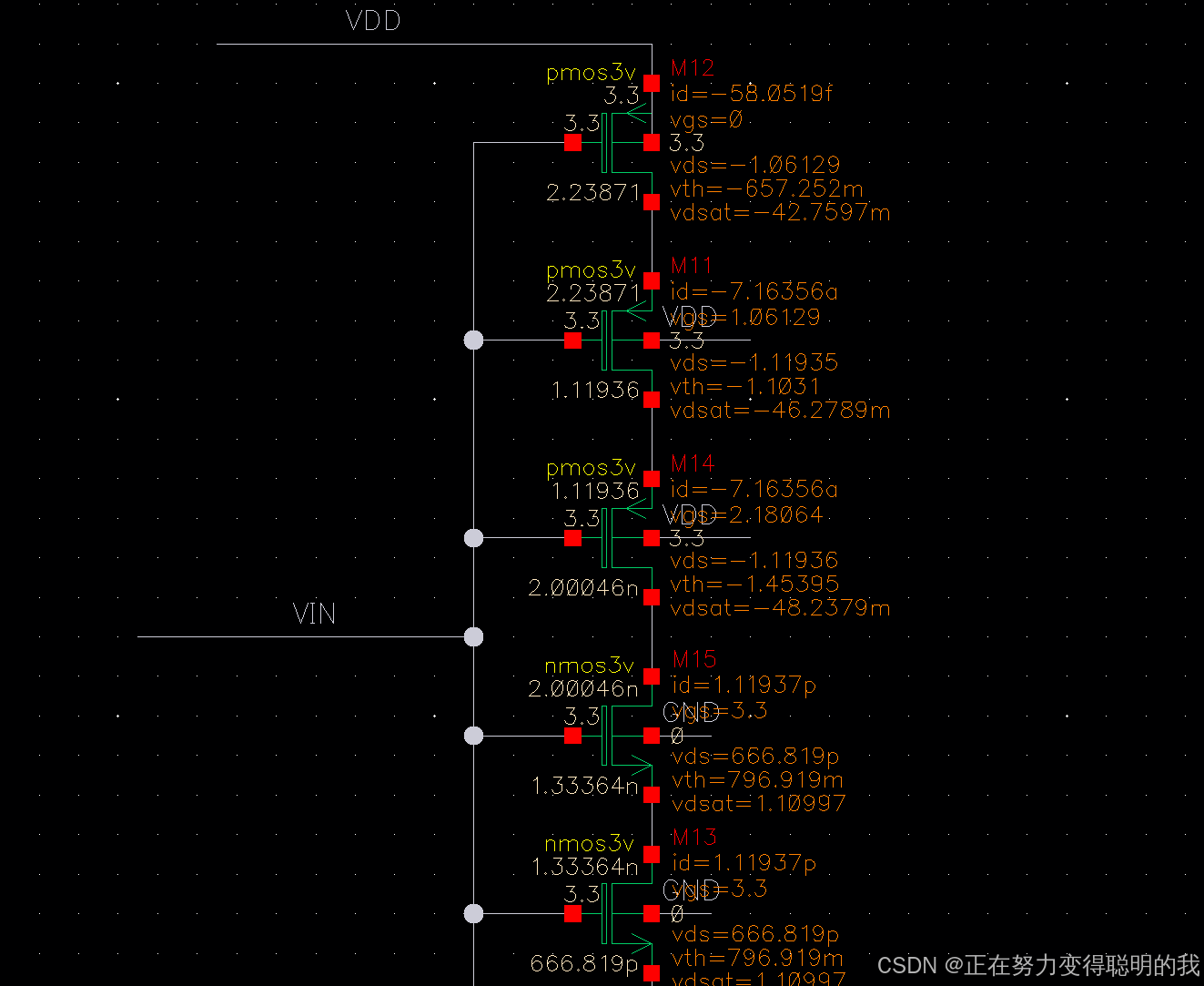

为了进一步验证,我们采用三个PMOS串联,可以看到,每个PMOS的Vds均为1.1左右,也是均分3.3V电压(当然,我们每次电路采用的都是长宽一样的PMOS)

PS:Candence Virtuoso 如何在电路图里显示直流工作点相关参数呢(+_+)?

在进行DC分析之后,选择【results】——【Annotate】,然后就可以选择所希望看到的直流仿真结果或者参数了,我这里选择的是【DC Note Voltages】和【DC Operating Points】

如果这篇文章帮助到您了,可以给我点个赞吗

(✿◕‿◕✿)

2607

2607

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?