视频链接

SPI Flash电路设计

1、SPI flash介绍

SPI是串行外设接口(Serial Peripheral Interface)的缩写,由Motorola提出,是一种高速的、全双工、同步的通信总线。一般主要应用在MCU和外围设备之间的通讯,广泛应用在Flash,模数转换器,通讯模块等外围芯片或者模块与MCU之间的通讯。

SPI flash就是通过串行的接口进行操作的flash存储设备。

一般板卡会配有一个spi flash存储芯片。flash具有断电数据不丢失的特性。

将上电程序固化在FLASH中,上电后FPGA芯片读取到FLASH中存储的程序进行运行,这样就能做到程序断电不丢失了。

flash按照内部存储结构不同,分为两种:nor flash和nand flash。这里spi flash属于nor flash!

此类芯片厂家一般有winbond(华邦),Micron(镁光),numonyx(恒亿)、ISSI(芯成),兆易创新等厂家。

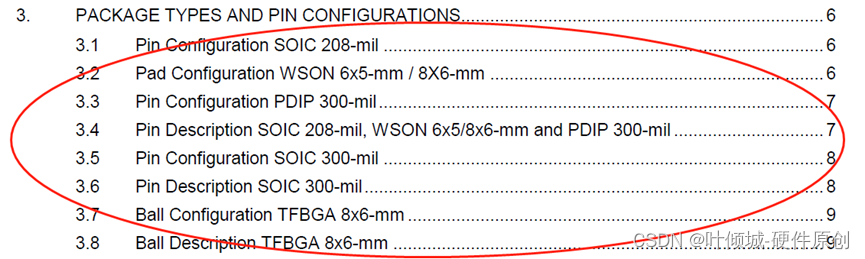

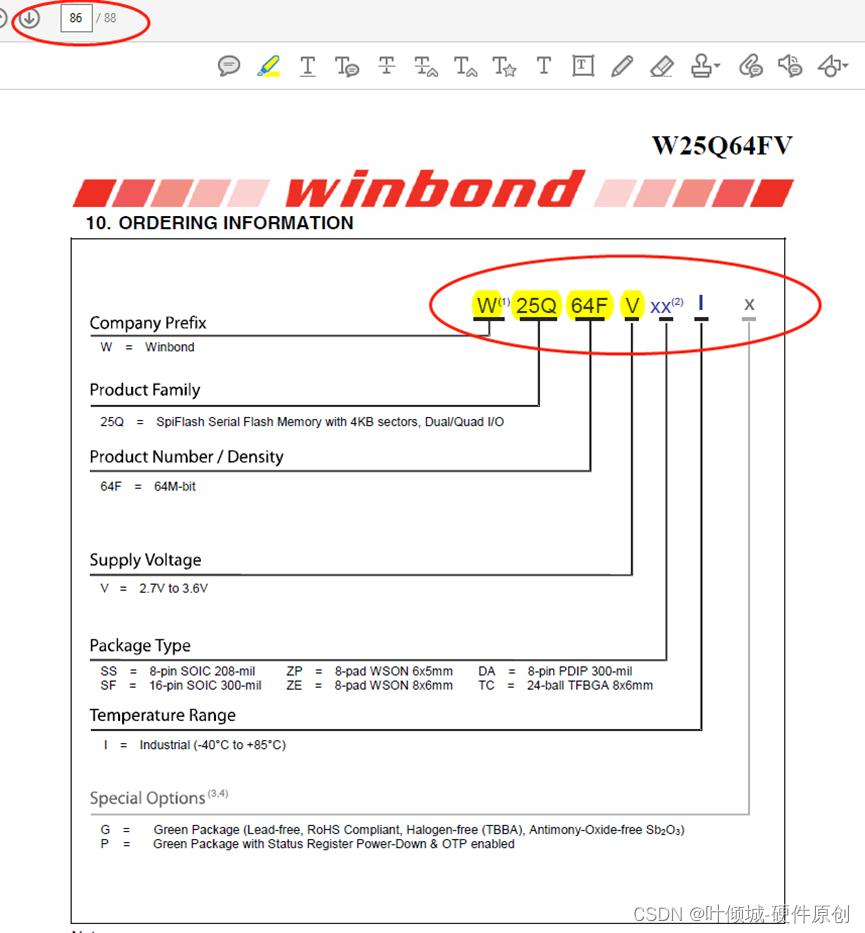

2、SPI flash的常见封装和型号

以winbond(华邦)以型号W25Q64为例进行简要说明。

3.1、封装

3.2、器件选型

3、SPI Flash的内部结构(一般情况)

4、SPI flash的特点

1. 串行通信接口:SPI flash通过串行接口与主控制器通信,通常使用SPI协议进行数据传输。

2. 低功耗:SPI flash通常具有低功耗特性,适合用于移动设备和便携式设备中,能够延长设备的电池寿命。

3. 随机访问速度:与传统的并行flash相比,SPI flash的随机访问速度较快,能够更快地读写数据。

4. 小尺寸:SPI flash通常体积小巧,集成在电路板上时占用空间较少,适合应用于空间受限的设备中。

5. 易于集成:SPI flash与主控制器通过简单的串行接口进行通信,集成到各种设备中较为容易。

6. 低成本:由于SPI flash采用了串行通信接口,其生产成本相对较低,适合大规模应用。

5、EEPROM和SPI Flash的区别

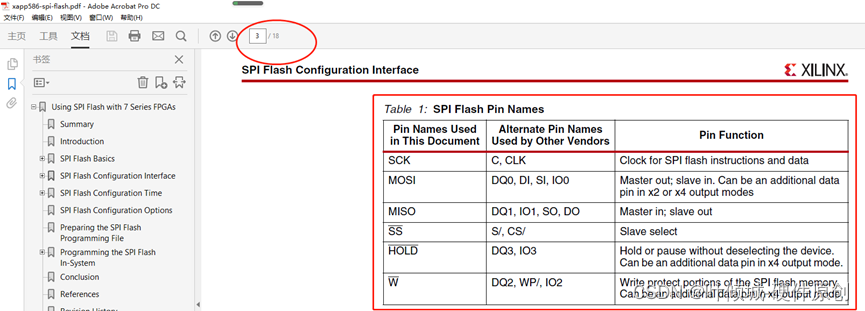

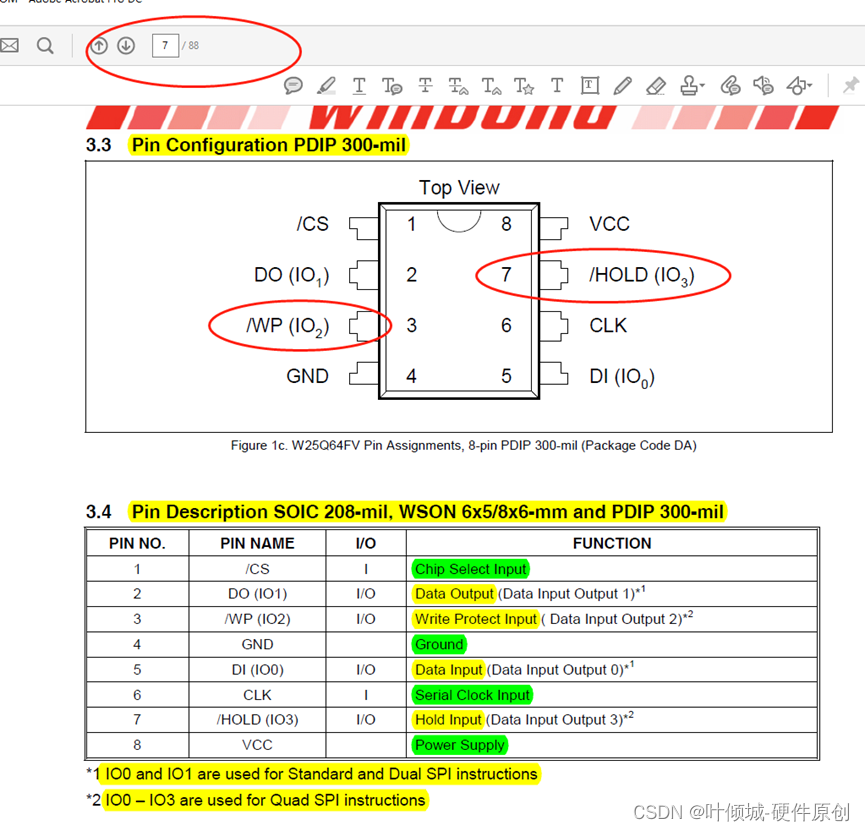

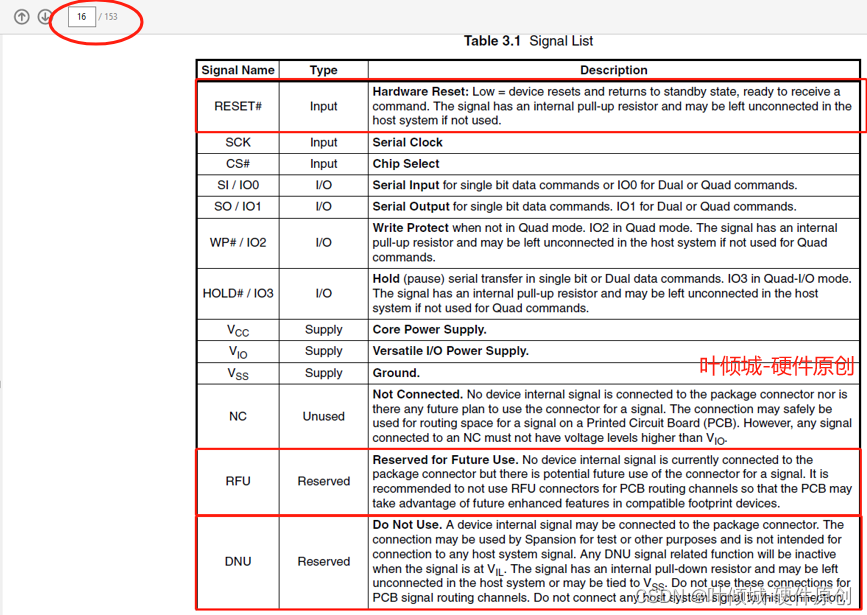

6、SPI Flash的管脚定义

引用:XAPP586-SPI-FLASH P3页

不同供应商的SPI Flash编写Datasheet的时候,因为缺少规范,所以不同供应商的SPI Flash的寄存器可以不同,寄存器的各位的名称,指令,甚至于IO引脚的名称也不尽相同。

SCK: Serial Clock,作用是主设备往从设备传输时钟信号,控制数据交换及速率;

SS/CS:Slave Select/Chip Select,用于主设备片选从设备,由主设备控制;

SDO/MOSI:Serial Data Output/Master Out Slave In, 主机数据输出,从机数据输入;作用是SPI设备发送数据;

SDI/MISO:Serial Data Input/Master In Slave Out, 主机数据输入,从机数据输出;作用是SPI设备接收数据;

/CS:CS高电平的时候其他引脚成高阻态;处于低电平的时候,可以读写数据

(SPI芯片选择(/CS)引脚启用和禁用设备操作。当/CS高时,设备被取消选择,串行数据输出(DO,或IO0,IO1,IO2,IO3)引脚处于高阻抗。当取消选择时,设备的功耗将处于待机状态,除非正在进行内部擦除、程序或写状态寄存器循环。当/CS低时,设备将被选中,功耗将增加到激活水平,可以写入指令和从设备读取数据。通电后,/CS必须从高到低转换,才能接受新的指令。在上电时,/CS输入必须跟踪VCC电源水平。如果需要,可以使用/CS上的上拉电阻来实现这一点。)

DI:标准SPI使用单向的DI,来串行的写入指令,地址,或者数据到FLASH中,在时钟的上升沿。

DO:标准SPI使用单向的DO,来从处于下降边沿时钟的设备,读取数据或者状态

/WP:防止状态寄存器被写入;低有效

(写保护(/WP)引脚可以用来防止状态寄存器被写入。与状态寄存器的块保护(CMP,SEC,TB,BP2,BP1和BPO)位和状态寄存器保护(SRP)位结合使用,小到4KB扇区或整个存储阵列都可以得到硬件保护。/WP引脚低有效。然而,当状态寄存器2的QE位设置为Quad I/0时,/WP引脚功能不可用,因为这个引脚用于I02。)

(/HOLD引脚,当它有效时允许设备暂停。当/HOLD低而/CS低时,DO引脚将处于高阻抗,DI和CLK引脚上的信号将被忽略。当/HOLD为高时。设备操作可以恢复。当多个设备共享相同的SPI信号时,/HOLD功能可以用到。

串行CLK:为输入输出功能提供时钟

串行CLK:为输入输出功能提供时钟

还有的spi flash带有reset管脚

参考给出的器件手册:S25FL256SAGNFI00------飞索半导体

7、SPI Flash的三种IO

SPI Flash现在有三种可用的IO,Winbond称之为Standard/Dual/Quad IO,也有的写为1X/2X/4X IO。Dual/Quad IO的目的是为了提升Standard SPI Flash的读写速度的。

以同时支持三种IO的W25Q16BV为例,其IO引脚的定义为:

| VCC,GND,/CS,CLK为共用Pin | ||||

| Pin脚编号 | 5 | 2 | 3 | 7 |

| Standard IO | DI (输入) | DO (输出) | /WP (输入) | /HOLD (输入) |

| Dual IO | IO0 | IO1 | /WP (输入) | /HOLD (输入) |

| Quad IO | IO0 | IO1 | IO2 | IO3 |

8、SPI Flash硬件电路设计要点(★)

8.1、常规注意点

8.2、超级重要:注意

8.3、各FPGA对应的专用管脚

A7

K7

ZYNQ

XC6S BANK2

| DCLK | R15管脚 |

| 片选 | V3管脚 |

| IO0 | R13管脚 |

| IO1 | V16管脚 |

| IO2 | T14管脚 |

| IO3 | V14管脚 |

EP4CE10

| DCLK | H1管脚 |

| 片选 | D2管脚 |

| IO0 | C1管脚 |

| IO1 | H2管脚 |

9、硬件实战设计(★)

9.1 A7实战

9.2 K7实战

9.3 ZYNQ7020实战

9.4 K7-米联客

9.5 xilinx-S6实战

9.6 altera-EP4CE10实战

9.7 HI3516实战

9.8、其他

10、PCB走线规范

1、SPI Flash在布局的时候要紧靠对应的MCU(FPGA)。

2、注意等长。误差+/- 5mil。

3、注意3W。

4、千万不要跨分割。

1857

1857

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?