视频链接

PCIE转USB 3.0电路设计01_哔哩哔哩_bilibili

PCIE转USB 3.0电路设计

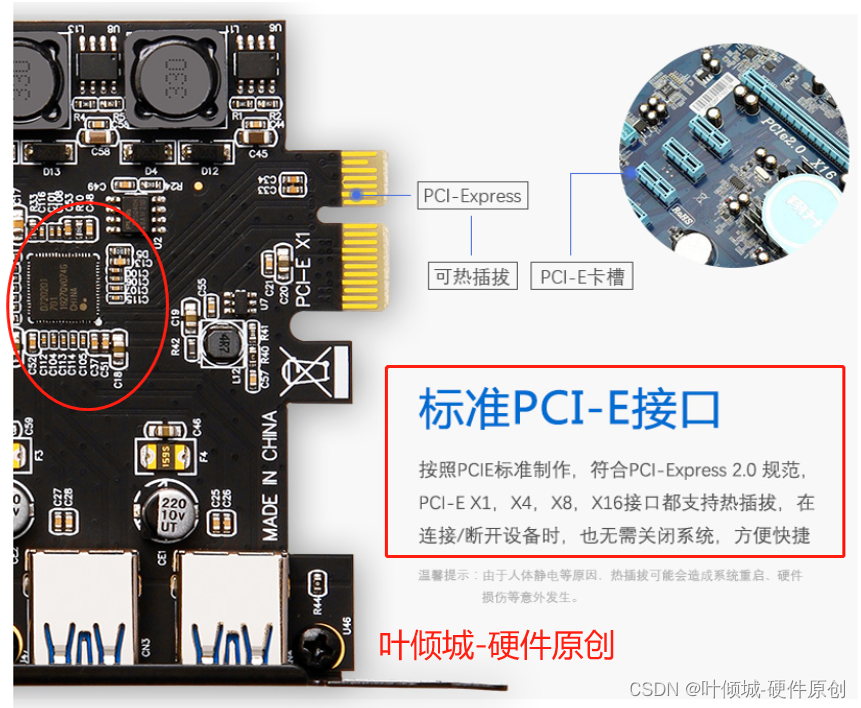

1、PCIE转USB电路设计基本介绍

很多CPU只有USB2.0的接口,没有集成USB3.0的接口,就需要通过PCIE转USB3.0。

2、PCIE转USB的两种方案

2.1、瑞萨µPD720201(PCIe转USB3.0芯片)

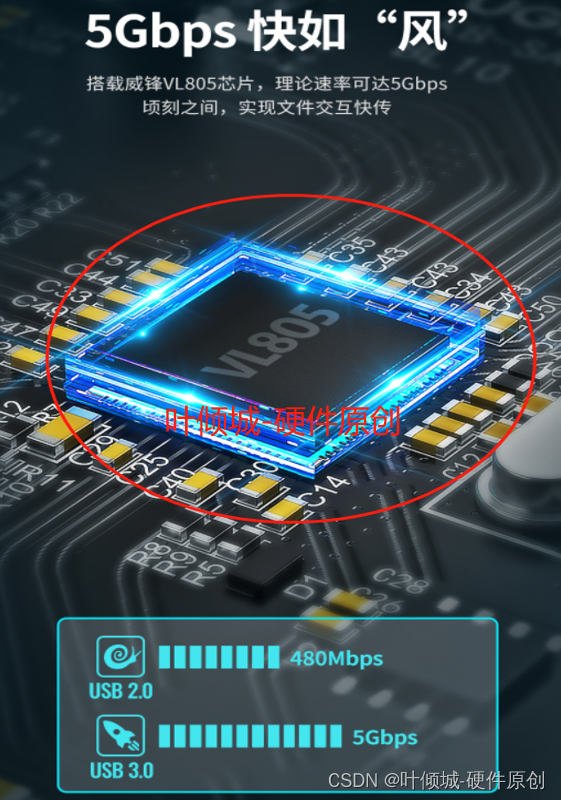

2.2、威丰VL805(PCIe转USB3.0芯片)

3、套片、桥片、PCIE switch等基本介绍

3.1、套片(不需要)

3.2、PCIE switch

3.3、桥片

3.4、CPU本身自带的PCIE接口

4、以超威主板为例

5、PCIE转USB的方案(以µPD720201为例)

//国微电子: SM720201MP USB3.0转换控制器对标µPD720201

瑞萨发布第三代USB 3.0控制器

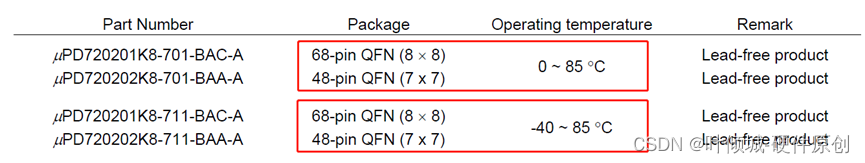

μPD720201最多支持四个USB3.0个超高速端口,μPD720202最多支持两个USB3.0个超高速端口。

| 优势产品 | 应用 |

| USB3.0 | 主机控制器 |

| 4port | uPD720201K8-701-BAC-A(QFN68 pin 8×8) |

| 2port | uPD720202K8-701-BAA-A(QFN48 pin 7×7) |

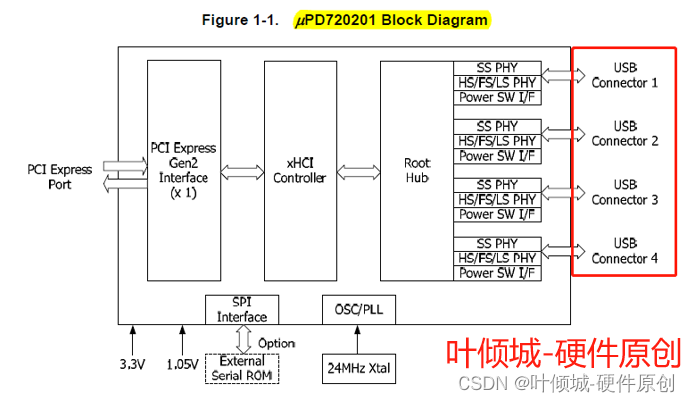

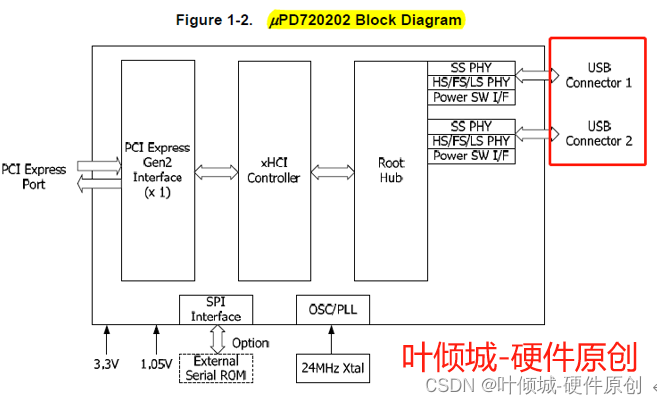

5.1、结构框图

μPD720201和μPD720202两者的区别在于

μPD720201 转出4路

μPD720202 转出2路

5.2、信号定义

1、Power supply

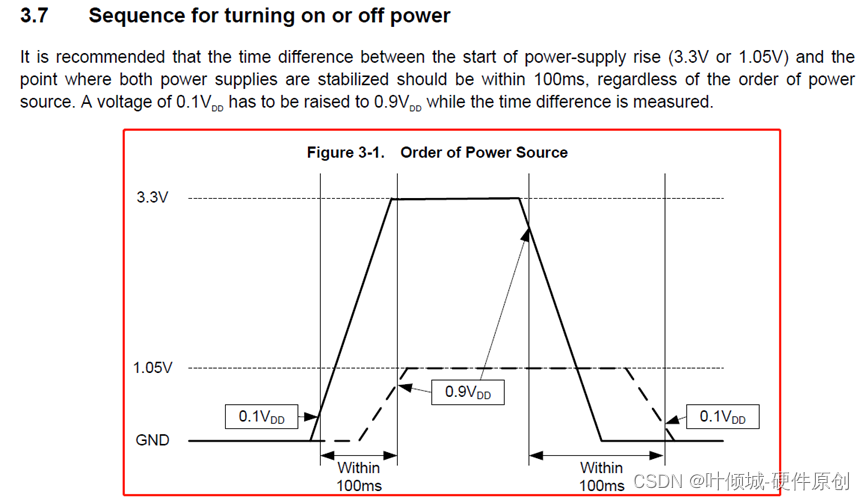

对于电源电压,系统要求

| 管脚符号 | 类型 | 描述 |

| VDD33 | Power | +3.3 V power supply |

| VDD10 | Power | +1.05 V power supply. |

| AVDD33 | PWR | +3.3 V power supply for analog circuit. |

| GND | GND | Ground |

| IC(L) | I | Test pin. Connect to ground. |

2、Analog Signal

| 管脚符号 | 类型 | 描述 |

| RREF | USB2 | Reference resistor connection. |

3、System Signal

3.1、clock

| 管脚符号 | 类型 | 描述 |

| XT1 | I (OSC) | Oscillator in Connect to 24 MHz crystal. |

| XT2 | O (OSC) | Oscillator out Connect to 24 MHz crystal. |

3.2、Interface Signal

| 管脚符号 | 类型 | 描述 |

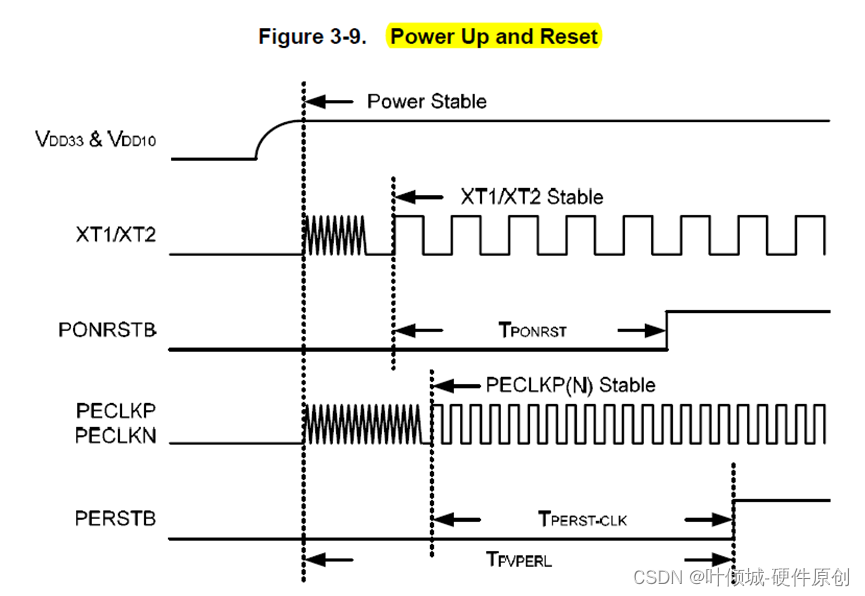

| PONRSTB | I (3.3 V Schmitt Input) | Power on reset signal. When supporting wakeup from D3cold, this signal should be pulled high with system auxiliary power supply. |

| SMIB | O (Open Drain) | System management Interrupt signal. This is controlled with the USB Legacy Support Control/Status register. |

3.3、PCI Express Interface

| 管脚符号 | 类型 | 描述 |

| PECLKP | I (PCIE) | PCI Express 100 MHz Reference Clock. |

| PECLKN | I (PCIE) | PCI Express 100 MHz Reference Clock. |

| PETXP | O (PCIE) | PCI Express Transmit Data+. |

| PETXN | O (PCIE) | PCI Express Transmit Data-. |

| PERXP | I (PCIE) | PCI Express Receive Data+. |

| PERXN | I (PCIE) | PCI Express Receive Data-. |

| PERSTB | I (3.3 V Input) | PCI Express “PERST#” signal. |

| PEWAKEB | O (Open Drain) | PCI Express “WAKE#”signal. |

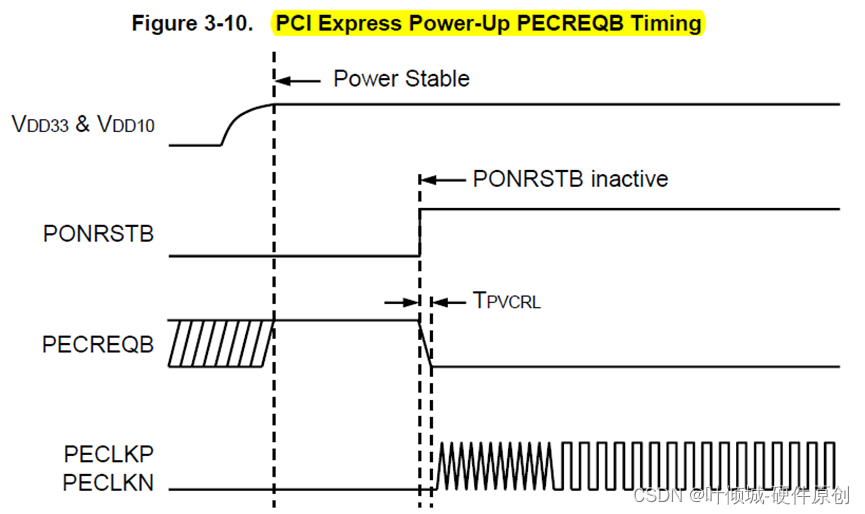

| PECREQB | O (Open Drain) | PCI Express “CLKREQ#” signal. |

这边仅以8个网络为一组PORT为例!实际是8X4(4组合计32根线)!

| 管脚符号 | 类型 | 描述 |

| U3TXDP1 | O (USB3) | USB3.0 Transmit data D+ signal for SuperSpeed |

| U3TXDN1 | O (USB3) | USB3.0 Transmit data D- signal for SuperSpeed |

| U3RXDP1 | I (USB3) | USB3.0 Receive data D+ signal for SuperSpeed |

| U3RXDN1 | I (USB3) | USB3.0 Receive data D- signal for SuperSpeed |

| U2DP1 | I/O (USB2) | USB2.0 D+ signal for Hi-/Full-/Low-Speed |

| U2DM1 | I/O (USB2) | USB2.0 D− signal for Hi-/Full-/Low-Speed |

| OCI1B | I (3.3 V Input) | Over-current status input signal. |

| PPON1 | O (3.3 V Output) | USB port power supply control signal. |

3.5、SPI Interface

| 管脚符号 | 类型 | 描述 |

| SPISCK | O (3.3 V Output) | SPI serial flash ROM clock signal. |

| SPICSB | O (3.3 V Output) | SPI serial flash ROM chip select signal. |

| SPISI | O (3.3 V Output) | SPI serial flash ROM slave input signal. |

| SPISO | I (3.3 V Input) | SPI serial flash ROM slave output signal. |

本文详细介绍了PCIE转USB3.0电路设计,包括瑞萨的μPD720201和威丰的VL805芯片方案,涉及套片、桥片和PCIEswitch等概念,并以超威主板为例,展示了μPD720201的特性、信号定义及设计要点,建议结合视频进行深入学习。

本文详细介绍了PCIE转USB3.0电路设计,包括瑞萨的μPD720201和威丰的VL805芯片方案,涉及套片、桥片和PCIEswitch等概念,并以超威主板为例,展示了μPD720201的特性、信号定义及设计要点,建议结合视频进行深入学习。

930

930

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?